# **Table of Contents**

| 1 | Introduction1            |                                                    |    |  |  |  |

|---|--------------------------|----------------------------------------------------|----|--|--|--|

|   | 1.1                      | Background                                         | 1  |  |  |  |

|   | 1.2                      | Addressing Range Considerations                    | 3  |  |  |  |

|   | 1.3                      | Wide Bus Utilization                               |    |  |  |  |

|   | 1.4                      | Cache Misses: Conflict and Compulsory              |    |  |  |  |

|   | 1.5                      | Interference in Unified Caches                     |    |  |  |  |

|   | 1.6                      | Summary of Data Placement Opportunities            |    |  |  |  |

|   | 1.7                      | Outline of Ensuing Chapters                        | 6  |  |  |  |

| 2 | Related Work             |                                                    |    |  |  |  |

|   | 2.1                      | Code Placement                                     |    |  |  |  |

|   | 2.2                      | Data Prefetching                                   |    |  |  |  |

|   | 2.3                      | Loop Transformations 1                             |    |  |  |  |

|   | 2.4                      | Data Transformations                               |    |  |  |  |

|   | 2.5                      | Load and Store Coalescing for Wide Buses           |    |  |  |  |

|   | 2.6                      | Reducing Range-Dependent Addressing Costs          |    |  |  |  |

|   | 2.7                      | Heap Optimizations                                 |    |  |  |  |

|   | 2.8                      | Cache Conscious Data Placement                     |    |  |  |  |

|   | 2.9                      | The Potential for Improvement on Prior Work        | 20 |  |  |  |

| 3 | Data A                   | nta Affinity Analysis                              |    |  |  |  |

|   | 3.1                      | Code and Data Profiling in Prior Work              |    |  |  |  |

|   | 3.2                      | Interprocedural Static Data Analysis               |    |  |  |  |

|   |                          | 3.2.1 Intraprocedural Analysis                     |    |  |  |  |

|   |                          | 3.2.2 Interprocedural Data Analysis                |    |  |  |  |

|   | 3.3                      | Inlining Functions in the CFGs of a Program        |    |  |  |  |

|   | 3.4                      | Path Analysis to Produce the Affinity Array        |    |  |  |  |

|   |                          | 3.4.1 Path Analysis without Complete Inlining      |    |  |  |  |

|   |                          | 3.4.2 Result of Path Analysis                      |    |  |  |  |

| 4 | Data Placement           |                                                    |    |  |  |  |

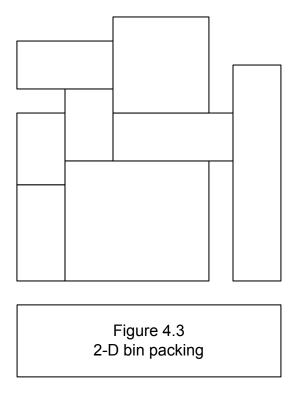

|   | 4.1                      | Cache Line Packing                                 | 56 |  |  |  |

|   |                          | 4.1.1 The Greedy Algorithm for Cache Line Packing. |    |  |  |  |

|   |                          | 4.1.2 A Graph Matching Algorithm for Cache Line Pa |    |  |  |  |

|   |                          | 4.1.3 Cache Line Packing by Graph Partitioning     |    |  |  |  |

|   |                          | 4.1.4 Other Methods for Cache Line Packing         |    |  |  |  |

|   | 4.2                      | Data Placement by Graph Partitioning               |    |  |  |  |

|   | 4.3                      | Fine Tuning the Graph Partitioning 70              |    |  |  |  |

|   | 4.4                      | Local Refinement of the Data Placement Solution    |    |  |  |  |

|   | 4.5                      | Padding Large Arrays to Minimize Conflicts 83      |    |  |  |  |

|   | 4.6                      | Data Placement for Local Variables                 |    |  |  |  |

|   | 4.7                      | Reducing Bus Cycles with Load Coalescing           |    |  |  |  |

|   | 4.8                      | Reducing Addressing Costs for Global Variables     |    |  |  |  |

|   | 4.9                      | Reducing Code/Data Conflicts in Unified Caches     |    |  |  |  |

|   | 4.10                     | Code Generation after Data Placement               |    |  |  |  |

| 5 | Measurements and Results |                                                    |    |  |  |  |

|   | 5.1                      | Benchmark Programs                                 |    |  |  |  |

|   |                          |                                                    |    |  |  |  |

|   | 5.2                                           | Performa                                                                  | ance Results for Optimizations                                   | 102        |  |  |  |

|---|-----------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------|------------|--|--|--|

|   |                                               | 5.2.1                                                                     | Data Placement Of Local Variables                                | 119        |  |  |  |

|   | 5.3                                           | Analyzing the Optimization Stages                                         |                                                                  |            |  |  |  |

|   | 5.4                                           | Comparison to Prior Work                                                  |                                                                  |            |  |  |  |

|   | 5.5                                           | Enhancements Suggested by the Measurements and Results 130                |                                                                  |            |  |  |  |

| 6 | Determi                                       | <b>Determining Cache Parameters and Retargeting the Optimizations</b> 131 |                                                                  |            |  |  |  |

|   | 6.1                                           | Background 132                                                            |                                                                  |            |  |  |  |

|   |                                               | 6.1.1                                                                     | Dynamic Measurements Using Timing Tools                          | 133        |  |  |  |

|   | 6.2                                           | Robustne                                                                  | ess and Portability                                              | 134        |  |  |  |

|   |                                               | 6.2.1                                                                     | Performance Counter APIs and Portability                         | 134        |  |  |  |

|   |                                               | 6.2.2                                                                     | Robustness and Reliability                                       | 135        |  |  |  |

|   | 6.3                                           | Algorithms and Measurements                                               |                                                                  |            |  |  |  |

|   |                                               | 6.3.1                                                                     | Data Cache Line Size                                             | 137        |  |  |  |

|   |                                               | 6.3.2                                                                     | Data Cache Size                                                  | 138        |  |  |  |

|   |                                               | 6.3.3                                                                     | Data Cache Associativity                                         | 139        |  |  |  |

|   |                                               | 6.3.4                                                                     | Write Allocation Policy                                          | 140        |  |  |  |

|   |                                               | 6.3.5                                                                     | Replacement Policy                                               | 140        |  |  |  |

|   |                                               | 6.3.6                                                                     | Data Cache Subblocking                                           |            |  |  |  |

|   |                                               | 6.3.7                                                                     | Data Cache Miss Penalties                                        | 143        |  |  |  |

|   |                                               | 6.3.8                                                                     | Data Cache: Split or Unified                                     | 145        |  |  |  |

|   |                                               | 6.3.9                                                                     | Instruction Cache Line Size                                      | 146        |  |  |  |

|   |                                               | 6.3.10                                                                    | Instruction Cache Size                                           | 146        |  |  |  |

|   |                                               | 6.3.11                                                                    | Instruction Cache Associativity                                  | 147        |  |  |  |

|   |                                               | 6.3.12                                                                    | TLB Measurements                                                 | 147        |  |  |  |

|   | 6.4                                           | Summary                                                                   | y of Measurements                                                | 148        |  |  |  |

|   | 6.5                                           | Implementation                                                            |                                                                  |            |  |  |  |

|   | 6.6                                           | Software Availability                                                     |                                                                  |            |  |  |  |

|   | 6.7                                           | Ongoing Work                                                              |                                                                  |            |  |  |  |

|   | 6.8                                           | Supplem                                                                   | enting AMP with Microbenchmarks                                  | 150        |  |  |  |

|   |                                               | 6.8.1                                                                     | Computing Benefits of Load and Store Coalescing                  | g 151      |  |  |  |

|   |                                               | 6.8.2                                                                     | Computing Benefits of Immediate-Mode Addressical Variables 152   | ng for Lo- |  |  |  |

|   |                                               | 6.8.3                                                                     | Computing Benefits of Moving Cache Misses Ear<br>Cache Lines 153 | lier in    |  |  |  |

|   |                                               | 6.8.4                                                                     | Computing the Cost of Cache Thrashing                            | 153        |  |  |  |

|   | 6.9                                           | Retargeti                                                                 | ing the Optimizations                                            | 153        |  |  |  |

| 7 | Implications for Hardware and Software Design |                                                                           |                                                                  |            |  |  |  |

|   | 7.1                                           |                                                                           | ture Interactions                                                |            |  |  |  |

|   | 7.2                                           | Implicati                                                                 | ons for Microarchitecture Implementation                         | 158        |  |  |  |

|   | 7.3                                           | Implications for Software Engineering Practices                           |                                                                  |            |  |  |  |

| 8 | Conclusions and Future Work                   |                                                                           |                                                                  |            |  |  |  |

|   | 8.1                                           | Summary                                                                   | y of Contributions of the Research                               | 162        |  |  |  |

|   | 8.2                                           | Future E                                                                  | nhancements and Extensions of the Research                       | 164        |  |  |  |

|   |                                               |                                                                           |                                                                  |            |  |  |  |

| TABLE 5-1:  | Benchmark programs.                                                | 100    |

|-------------|--------------------------------------------------------------------|--------|

| TABLE 5-2:  | Cumulative sizes of global variables by category                   | 101    |

| TABLE 5-3:  | Execution time speedup results                                     | 103    |

| TABLE 5-4:  | First-level data cache read misses.                                | 104    |

| TABLE 5-5:  | Second-level unified cache data read misses.                       | 106    |

| TABLE 5-6:  | Second-level unified cache data write misses.                      | 107    |

| TABLE 5-7:  | Second-level unified cache total data misses.                      | 107    |

| TABLE 5-8:  | Changes in instruction cache misses and invalidations.             | 110    |

| TABLE 5-9:  | Data cache changes as a percentage of executed instructions        | 111    |

| TABLE 5-10: | First-level data cache read miss rates.                            | 113    |

| TABLE 5-11: | Effect of using split second-level caches.                         | 114    |

| TABLE 5-12: | Associativity effect on DYFESM data cache misses                   | 116    |

| TABLE 5-13: | First-level cache write misses.                                    | 118    |

| TABLE 5-14: | Data TLB misses.                                                   | 118    |

| TABLE 5-15: | Path analysis path terminations by cause.                          | 120    |

| TABLE 5-16: | Cache line packing data.                                           | 121    |

| TABLE 5-17: | Relative conflict reductions by optimization stage                 | 122    |

| TABLE 5-18: | Relative benefits of the best five swaps and all rotations         | 123    |

| TABLE 5-19: | Compilation times in seconds.                                      | 125    |

| TABLE 5-20: | Compilation time in seconds by stage.                              | 126    |

| TABLE 5-21: | Compilation time in seconds by stage (continued)                   | 127    |

| TABLE 5-22: | Comparison with CCDP (different benchmarks used)                   | 129    |

| TABLE 6-1:  | Measured Cache and TLB Parameters                                  | 148    |

| TABLE 6-2:  | Miss Penalties for Various Intel CPU Personal Computers and SG 149 | I MIPS |

:

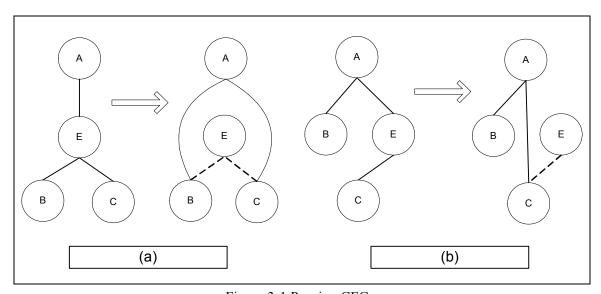

Temporal relationship graph. 11 Pruning CFGs. 37 Further CFG pruning examples. 38

# Chapter 1

## Introduction

Many recent research efforts in the field of optimizing compilers have focused on the placement of data. Careful placement of data items has been demonstrated to reduce cache misses and execution time in popular benchmark programs. These efforts have been concentrated on just a few types of data (large arrays, and heap-allocated objects) and in only a few application program categories (scientific array-processing programs, and programs that primarily traverse pointers across recursive data structures). The first level data cache has been the primary focus of most of these efforts. It appears that these research areas are nearing maturity, as will be seen in the next chapter.

However, this research will demonstrate that data placement optimizations can have greater scope and impact than previously thought. Several architectural features of modern microprocessors interact with the placement of data and affect performance. Specifically, (1) limited addressing ranges and use of registers for addressing, (2) wide data buses, and (3) multilevel cache hierarchies, each require data placement optimizations to ensure their efficient use.

After providing background information about these problems in this chapter, we will discuss related work in the next chapter. We then devote the remaining chapters to exposition of a unified data placement framework that efficiently utilizes all of these architectural features while still being easily retargeted to numerous machines with different microarchitectures and memory hierarchies.

# 1.1 Background

The processor and various memory hierarchy components of a modern computer system are constructed from a variety of technologies that are improving at differing rates. Processor speed is primarily determined by on-chip transmission and transistor switching speeds, which are improving rapidly as semiconductor processes evolve. Cache memories

5/6/04

Chapter 1: Introduction Background 2

are constructed from SRAM chips that also depend on transistor switching and use the same semiconductor processes as CPUs. However, at some point in a modern multi-level cache system, physical boundaries must be crossed that do not depend primarily upon transistor switching. Driving current through chip pins and printed circuit board traces, charging and discharging capacitors in a DRAM chip, and accessing electromechanical mass storage devices are all examples of memory hierarchy technologies that are not driven primarily by transistor switching speeds. None of these elements of the computer system can be expected to keep up with the speed improvements of CPUs; e.g., the 50% annual improvement in processor speeds has been widely contrasted with about a 7% annual improvement in DRAM first-access times ([Hennessy and Patterson 1990], p. 426).

Both hardware and software approaches that address this problem have been attempted. In hardware, the addition of pipelined memories and cache memories, including as many as three levels of cache memory in some systems, has been refined over several decades [Boland et al. 1967, Chen and Baer 1992, Jouppi and Wilton 1994, Wilson and Olukotun 1997, Bodin and Seznec 1995]. Recent architectural advances attempt to use the instruction-level parallelism (ILP) of a program to efficiently utilize otherwise wasted CPU cycles while waiting on the memory hierarchy [Jourdan et al. 1995, Hara et al. 1996, Morano et al. 2003]. Hardware cache controllers, some assisted by compiler-generated hints, have been designed to reduce cache misses and miss penalties [McKee et al. 1996, Johnson 1998].

A few software approaches to reducing memory hierarchy delays have also been tried. Data prefetching attempts to mask cache miss penalties by issuing non-blocking data fetches that are scheduled many CPU cycles before the value is used to give the cache time to load the new line [Mowry et al. 1992, Luk and Mowry 1996, Annavaram et al. 2001, Solihin et al. 2002]. Various loop optimizations in compilers have attempted to optimize memory access patterns by reordering computations, along with such techniques as internal array padding to reduce intra-array conflicts. This area of compiler research is fairly mature [Abu-Sufah 1979, Kandemir 2001, Irigoin and Triolet 1988, Wolf and Lam 1991, Carr et al. 1994, Chatterjee et al. 2001]. More recently, data cache miss reduction in code that intensively uses pointers and heap data objects has been achieved via reordering within pointer-linked data structures [Kistler and Franz 2000] and also by passing cache placement hints

to custom heap allocators [Calder et al. 1998, Chilimbi and Larus 1998] and by redesigning allocators to optimize cache locality and not just to reduce memory fragmentation [Grunwald et al. 1993, Shuf et al. 2002]. These software research efforts will be surveyed in more detail in the next chapter.

In addition to the delays at each level of the memory hierarchy, other aspects of the architecture of modern computers may cause a degradation of performance if an application has poor data locality. The sections below will examine two of these considerations, namely the expense of addressing data objects in memory and the efficiency of utilization of the buses that connect each level of the memory hierarchy to adjacent levels.

# 1.2 Addressing Range Considerations

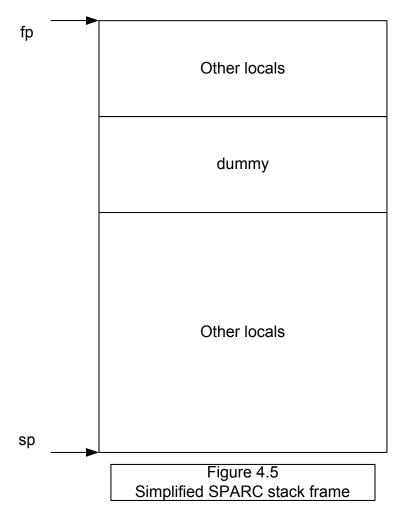

Most processor architectures have several available addressing modes in the instruction set. For example, the address of a data item could be produced by specifying two registers whose values are added (register plus register addressing), or an instruction could encode a base register and an immediate value offset to be added to the base register (base register plus offset addressing). Base register plus offset addressing is generally more efficient for addressing local data, as the base register is the frame pointer register which is set upon entry to a function and remains invariant throughout the function, while the immediate offset is computed at compilation time when the compiler arranges the local variables in the stack frame. Thus, both the base register and the immediate offset are available without further computation at the time that a local variable needs to be accessed. However, if a stack frame is large enough to exceed the range of the immediate offset, then the base address of the data item will have to be computed in a register other than the frame pointer when the data item is used in an expression, which will be more expensive than using the invariant frame pointer register as a base address. The dynamic frequency of this more expensive addressing of locals can be controlled by data placement within large stack frames

Similarly, global variables are most often addressed by computing the base address of the global in a register just prior to its use, then computing offsets either in an immediate field (if the offsets can be computed at compilation time) or in another register (as is the

Chapter 1: Introduction Wide Bus Utilization 4

case when looping through a data array using a loop index as the offset). In either case, the base register computations are not generally available in the header of each function, unlike the setting of the frame pointer, making accesses to global variables more expensive than accesses to local variables. If global data items were grouped by a data placement optimization according to their temporal locality in a program, then several global items accessed within a function could fall within the range of an immediate offset. By computing a global base address for these several variables into a register just once, in the function header, the address computations on most architectures could be reduced to a single load instruction at the point where each global is accessed. The size of the immediate addressing range differs from one machine to another, so this optimization is machine dependent.

#### 1.3 Wide Bus Utilization

A typical first-level data cache memory fetches 16, 32, or even 64 bytes from lower levels of the cache and memory hierarchy to satisfy a cache miss. The data item requested by the CPU is then provided over the cache-to-CPU-registers bus. Because many CPU designs now include 64-bit registers, it is common to have a 64-bit (8-byte) cache-to-CPU bus today.

However, many application program variables are still declared as 32-bit objects, or even as 16-bit or 8-bit data types. Thus, a portion of the 64-bit bus is idle when transferring a 32-bit value from the cache into a CPU register. If two consecutive 32-bit memory addresses were requested by load instructions, these loads could be combined, or *coalesced*, into a single 64-bit load that only requires one bus transaction rather than two [Davidson and Jinturkar 1994]. Rather than combine loads that happen to be from consecutive addresses, a compiler could perform a data placement optimization that maximizes the number of loads (or stores) that can be coalesced.

## 1.4 Cache Misses: Conflict and Compulsory

A request for a data item not found in the cache is a *cache miss*. Cache misses are generally classified into three categories: *Compulsory* misses, so named because they are caused by referencing a data item for the first time in a program's execution history; *capacity* misses,

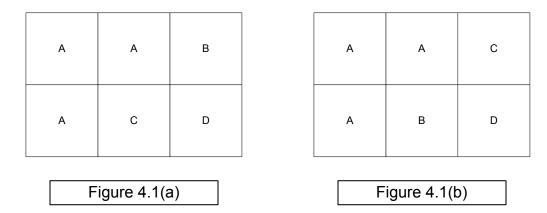

caused by referencing more cache lines over time than can fit into the cache; and *conflict* misses, caused by referencing different memory items which map to the same cache line number in the cache and exceed its ability to hold them all by its associativity (and which are neither compulsory nor capacity misses). For example, with a direct-mapped 16KB data cache, when a 32KB array is completely and repetitively processed from start to finish, the first 32KB set of references will generate compulsory misses, while the next complete processing of the array would generate capacity misses, as a 16KB array cannot be expected to hold 32KB of data. By comparison, if a program accessed repeatedly two array elements at offsets 0 and 16KB from the start of the array, the first two accesses would generate compulsory misses, while further misses would be classified as conflict misses, because these two addresses within the array will map to the same cache line number in the direct-mapped cache. Even though the program only accesses a few bytes within the array, and thus capacity is not a problem, the cache will be said to thrash as we repeatedly alternate accesses between these two elements. If, instead of a single array, a program had two consecutive 16KB arrays and accessed offset 0 within each array, this conflict miss thrashing could be avoided by placing the arrays in non-consecutive fashion, perhaps using some smaller variables between them, so that the starting offsets of the arrays did not map to the same cache line. This suggests that a data placement optimization can reduce conflict misses in a cache.

Furthermore, if variables within a program are not large enough to fill a cache line, they will share that cache line with other variables. When the first reference to any of these variables occurs, the compulsory miss will cause the entire cache line to be filled. References to other variables in that same line will then not suffer misses, due to the property of *spatial locality* exhibited, namely that references to items at addresses close to each other have occurred. A data placement optimization can reduce compulsory misses by grouping small variables together in a cache line if they are referenced close enough together in the execution time of the program to have the cache line still be present when the second reference occurs. It should be noted that different cache levels in a cache hierarchy often have different line sizes, with the bigger and lower levels having larger lines. Where this is the case, the cache line packing optimization must be designed to reduce compulsory misses at more than one level of cache by using a hierarchical packing algorithm.

### 1.5 Interference in Unified Caches

The most common design for a cache hierarchy is to have separate, or *split*, first level instruction and data caches, with second and lower level caches *unified*, i.e. containing both instructions and data. The split caches at the first level of most cache hierarchies offer the advantage of higher bandwidth, as instruction fetches and data fetches can be in progress simultaneously from separate caches over separate busses. Unified caches at the second and third cache levels have been observed to dynamically adapt themselves well to different applications, some of which reference a larger data set than their instruction stream, and some of which are the opposite. However, unified caches create the potential for conflicts between code and data, such that a data item is evicted from a unified cache by an instruction cache miss, causing a later reference to that data item to be a conflict miss. A data placement optimization should place data at addresses that do not conflict with the instruction stream that references that very same data set in order to be effective for multilevel cache hierarchies.

# 1.6 Summary of Data Placement Opportunities

It is apparent that a comprehensive data placement optimization would enhance program performance if it could simultaneously reduce addressing costs, reduce bus cycles, reduce conflict misses between data items, reduce compulsory data cache misses, and reduce code/data conflict misses in unified levels of the cache hierarchy. It is shown in the next chapter that prior work has addressed some of these concerns but not others, and no data placement optimization has addressed all of these performance issues in concert.

# 1.7 Outline of Ensuing Chapters

The remainder of this dissertation is organized as follows. Chapter 2 examines related prior work and the potential for improving upon those efforts. Chapter 3 presents the data analysis framework that provides the necessary information for data placement to proceed. Chapter 4 presents the data placement algorithms in detail, explaining the many design decisions and alternatives. Chapter 5 contains the measured results of applying our optimizations on various benchmarks. Chapter 6 addresses retargeting issues, the machine-

dependent information needed to implement the proposed data placement optimizations, and how to obtain that information. Chapter 7 examines the interactions between our optimizations and architectural design decisions, including lessons that computer architects could apply in their future designs to maximize performance and reduce hardware complexity in the presence of any compiler that implements our optimizations. Interactions with software engineering methodology are presented in this chapter as well. Chapter 8 presents a summary and conclusion.

# Chapter 2

#### Related Work

Prior work has addressed memory hierarchy related optimization in several ways. Code placement reduces conflict (and sometimes capacity) misses in the instruction cache. Prefetching attempts to reduce data cache misses without directly addressing placement issues. Loop transformations reduce data cache misses for applications that spend most of their time processing large arrays. Data transformations change the layout and size of arrays to reduce intra-array conflicts. Heap data placement reduces data cache conflicts between heap objects. Cache conscious data placement reduces conflicts in the first level data cache by placing global and heap variables. Each of these areas of prior work will be discussed in the following sections, along with their limitations and the need for further work.

#### 2.1 Code Placement

Code placement work has been published at least since 1989, beginning with McFarling's work that used profiling information to reduce direct-mapped instruction cache misses by combining code placement with cache bypassing [McFarling 1989]. Each basic block was placed in whatever order was deemed best by the placement algorithm, not being confined to the original ordering of the program. Certain instructions that created cache conflicts, even after code placement, were tagged as ineligible for caching, because the cost of caching exceeded the benefit. A hypothetical architecture that could make a caching decision on each instruction (with each instruction cache line being only one word long) could make use of this optimization. Results obtained by simulating such an architecture demonstrated cache miss reductions of as much as 61% (using cache bypassing) or 19% (without cache bypassing). Reducing the instruction cache misses by 19% translated into a 1.7 percentage point increase in the (already high) hit rate of the cache. No timings were made on real machines.

5/6/04 8

Chapter 2: Related Work Code Placement 2

Pettis and Hansen targeted not only cache misses but expensive branch instructions [Pettis and Hansen 1990]. On their Hewlett-Packard architecture, branches beyond a certain range required a more expensive instruction sequence than branches within that range. Accordingly, they used profiling information to group basic blocks into popular and unpopular sets, with the popular blocks placed closer to the top and unpopular blocks closer to the bottom of the procedure. A third set of basic blocks, called fluff, were never observed to execute at all during profiling (perhaps they contained error handling code, for example). These fluff blocks could be physically separated from the rest of the procedure's blocks and grouped into a memory region with fluff blocks from other procedures, a technique they called *procedure splitting*. A greedy algorithm then built a chain of procedures beginning with the two procedures that had the most calls and returns between them, adding to the chain until all procedures were ordered in the chain. This ordering reduced cache conflicts, as adjacent placement would minimize the overlap between two procedures in the cache. This combined approach of making often-executed blocks adjacent within a procedure while making procedures with mutual affinity in the call graph adjacent in the final code placement by the linker reduced the expensive branches while reducing instruction cache misses at the same time. Pettis and Hansen demonstrated that placing procedures alone was not as effective as reordering basic blocks within procedures first and then placing the procedures. Procedure placement achieved an 8% reduction in run time on their system, basic block reordering a 12% reduction, and the combination a 15% reduction. All figures are due partly to cache miss reduction and partly to reduction of the execution count of the long branches.

Hashemi, Kaeli and Calder modified the approach of Pettis and Hansen [Hashemi et al. 1997]. They labeled the procedures of the program as popular or unpopular depending not on their execution time, but on the frequency of calls into and out of each procedure. They then created a map of the cache, based on the actual cache size and cache line size, and began building a chain of procedures, starting with the most popular edge between a pair of procedures in the call graph, as in Pettis and Hansen. After placing a pair of procedures, the cache lines used are marked with arbitrary *colors* and further procedures are considered for adding to the chain. If the next most popular edge connects two procedures, neither of which was in the first pair of procedures just placed, then these form a new pair

Chapter 2: Related Work Code Placement 10

with arbitrary colors assigned. If the next most popular edge connects a procedure from one placed pair to a procedure in the other placed pair, then the possible orderings (e.g. for procedure pairs A-B and C-D, the possible chainings are A-B-C-D, B-A-C-D, A-B-D-C, and B-A-D-C) to place the two procedures with the popular edge between them close together (e.g. given A-B and C-D, with new popular edge B-D to process, an order A-B-D-C would be chosen). Then, if this ordering causes cache line conflicts between B and D, a gap will be inserted between B and D if such a gap eliminates or reduces the conflicts. If so, a best-fit search of the unpopular procedure list will attempt to find a way to fill this gap. If necessary, there will be gaps in the code layout. Thus, in contrast to Pettis and Hansen, the minimization of cache conflicts is directly addressed via cache line coloring while the procedure chain is being built. Measured results are a small improvement on Pettis and Hansen's results on about half of all benchmarks, and statistically identical on the other half.

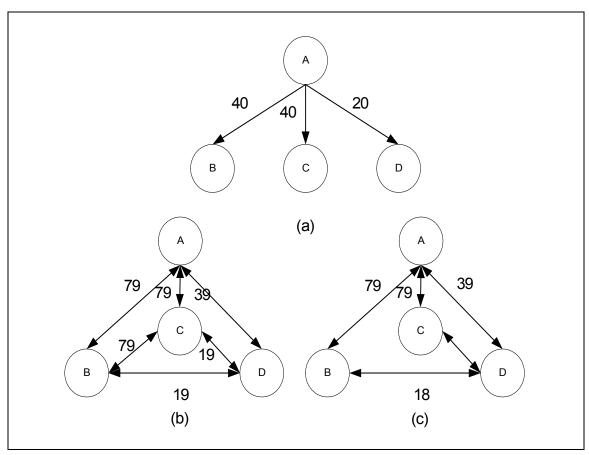

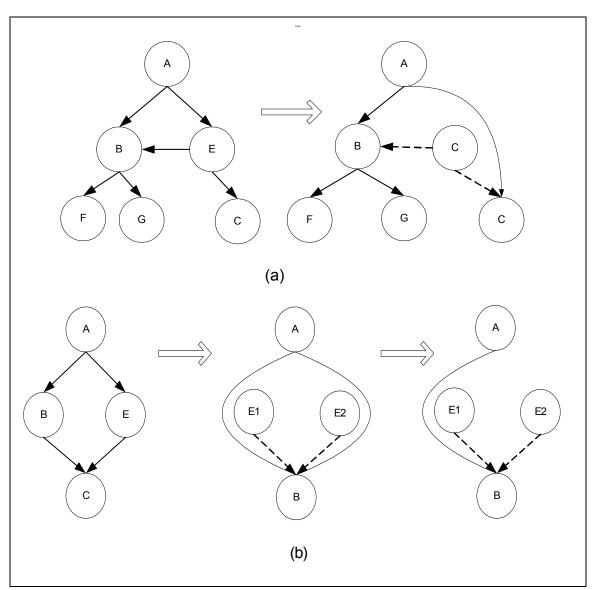

Following up on this work, Gloy, Blackwell, Smith, and Calder apply the same basic approach (chaining popular procedures, filling in gaps with unpopular procedures) with a few differences [Gloy et al. 1997]. The most important innovation is the profiling method, which produces a finer-grained data structure called a temporal relationship graph (TRG). The weighted call graph (WCG) of a hypothetical program (mimicking an example from their paper) is shown in Figure 2-1(a). From the WCG, we can determine that the main procedure, A, calls procedures B and C 40 times each, and it calls procedure D 20 times. Unfortunately, this tells us little about the cache behavior of the code. The dynamic procedure call trace of the program could be: A (BCBCD) <sup>20</sup>, meaning that procedure A goes through a loop 20 times, calling B, then C, then B, then C again, and then D. The same weighted call correspond to the call graph could procedure A ( (B)  $^4$ D)  $^{10}$  ( (C)  $^4$ D)  $^{10}$ , meaning that procedure A goes through a loop 10 times, calling B 4 times and then calling D once on each iteration, and then goes through a similar loop 10 times calling C and D. In the first case, if procedures B and C map to the same cache lines, they will thrash (cause excessive alternating conflict misses), while in the second case, procedures B and C could be mapped to the same cache lines with no conflict misses at all. Clearly, the WCG is not sufficient to distinguish between these two situations, which have very different implications for code placement.

Chapter 2: Related Work Code Placement 11

**Figure 2-1.** Temporal relationship graph.

To address this shortcoming, Gloy et al. developed the TRG. At all procedure call and return points, a call is made to a profiling procedure that maintains an ordered set of recent procedure references. If the current call or return is to procedure B, for example, the profiling procedure scans backwards in the set to find another instance of B. If found, then all of the references to other procedures in between the old reference to B and the current reference to B are recorded in the TRG, with new nodes and/or edges added as needed. Upon completion of profiling, the TRG accurately represents the potential conflicts in the instruction cache between pairs of procedures. For example, the second hypothetical dynamic procedure call trace above will become the call-and-return trace: A ((BA) <sup>4</sup>DA) <sup>10</sup> ((CA) <sup>4</sup>DA) <sup>10</sup> (because procedure returns are now represented in the trace, not just calls, as a return to a calling procedure causes the instruction fetches to be made from the procedure to which control is returned, affecting the instruction cache, and hence returns are modeled explicitly.) The TRG produced is shown in Figure 2-1(c). The first procedure call trace above corresponds to the TRG in Figure 2-1(b). Notice that the

Chapter 2: Related Work Data Prefetching 12

different temporal relationships between procedures B and C are now accurately modeled. In Figure 2-1(b), we can clearly see that B and C would conflict in the cache, while Figure 2-1(c) clearly shows that they do not have overlapping lifetimes and will not conflict in the cache. Unfortunately, the TRG profiling method causes the profiling run to take approximately 25 times as long as a normal run of the program. Thus, it is not practical for use on long-running programs, which are prime candidates for high levels of compiler optimization.

Further code placement work was done in the dissertation of Kalamatianos using yet another profiling method, which produced a Conflict Miss Graph (CMG) [Kalamatianos 2000]. The CMG uses a stack of procedure references, similar to the TRG approach, to model the interaction between procedures in the cache. The CMG operates at the cache line level and counts the worst case number of cache line conflicts that each procedure can cause another procedure to suffer. Code placement was done both with a first-level cache model, and with a multilevel cache model. Caches of arbitrary degrees of associativity could be modeled, whereas Gloy et al. targeted direct-mapped caches and described how the work could be extended to higher associativity caches. Otherwise, the same cache line coloring placement approach is used in both authors' work. Measured results were almost identical between the CMG and TRG approaches. Altering the placement algorithm to take into account more than one level of instruction caches did not lead to improvement. This was partly due to the fact that the placement algorithms were unable to address both L2 cache misses and page locality (and hence, instruction TLB (ITLB) misses). One of these metrics was always sacrificed to the other in the various algorithm versions tried. Another reason that multilevel placement did not yield benefits is that the L2 cache is shared, and conflicts between data and code must be modeled and reduced in order to optimize the performance of this level of the cache. No data placement was undertaken in this work.

# 2.2 Data Prefetching

Data prefetching attempts to mask cache miss penalties by issuing non-blocking data fetches that are scheduled many CPU cycles before the value is used to give the cache time to load the new line [Mowry et al. 1992, Luk and Mowry 1996]. If the prefetched line

Chapter 2: Related Work Loop Transformations 13

displaces a cache line that will be needed even before the prefetched line, then the prefetch was a mistake and degrades performance. If the prefetch requests a line that is already in the cache, then the prefetch instruction was an unnecessary bloat in the instruction stream and degrades performance. Thus, prefetching is best implemented within a data placement framework, where it can be used only for the few data variables that are known to be placed unavoidably in conflict with other objects that will have evicted these variables from the cache, making a prefetch profitable. Furthermore, the data placement framework will be able to determine "how far is too far" when hoisting the prefetch up to a location before the data is needed, because it will know when the hoisting of the prefetching load is crossing over another load that conflicts with the prefetched variable. Prefetching could be quite valuable within such a placement framework, but it is certainly not a substitute for data placement.

## 2.3 Loop Transformations

Various loop optimizations in compilers (loop tiling, loop inversion, cache blocking, etc.) have attempted to optimize memory access patterns by reordering computations [Irigoin and Triolet 1988, Wolf and Lam 1991, Carr et al. 1994, Abu-Sufah 1979]. One of the most precise efforts in this regard has been based on cache miss equations, which model the cache misses that will be produced by a given loop nest if the array subscript expressions of the arrays accessed within the loop nest are analyzable at compilation time, and apply loop transformations to directly address the cache conflict problems [Ghosh et al. 1999]. Because of the importance of fine tuning the performance of scientific applications that heavily process large arrays in loop nests, this area of research is probably the most mature within the general area of data cache miss reduction.

## 2.4 Data Transformations

Bacon et al. developed a compiler framework that analyzed affine array subscript equations and determined where there would be intra-array and inter-array conflicts [Bacon et al. 1994]. To solve intra-array conflicts, they introduced padding of dimensions within the array, e.g. making each column in a Fortran array longer by adding rows. To solve inter-

array conflicts, they calculated optimal inter-array padding distances, then reordered arrays and added dead space between arrays where it was needed. These kinds of data transformations, as with all others we are aware of, are applicable only to programs that spend the bulk of their time in array processing.

# 2.5 Load and Store Coalescing for Wide Buses

Davidson and Jinturkar examined the effectiveness of coalescing array loads and stores on machines with buses wider than some common data types, such as single-precision floating-point values [Davidson and Jinturkar 1994]. Their implementation unrolled loops in order to produce more than one load or store per loop iteration, then coalesced the loads or stores in order to reduce the number of loads and stores performed and hence reduce the number of bus cycles. After each coalesced load, the results must be unpacked into 2 or more destination registers. Similarly, before each store, results must be packed into a single register. Because most architectures have more efficient instruction sequences for unpacking bit fields from a register than for packing bit fields into a register, coalescing stores was not as productive as coalescing loads. In fact, coalescing stores was not beneficial on any of the three architectures tested (the DEC Alpha 21064, Motorola 88100, and Motorola 68030), and the expense of the unpacking instructions caused the benefits of load coalescing to vary across the architectures, even dropping into the negative range for the Motorola 68030, while DEC Alpha loop kernels saw execution time reductions of up to 40%. Operating on array items within unrolled loops, no data placement was involved in this optimization.

Nandivada and Palsberg performed a load and store coalescing optimization for the Intel IXP1200 network processor that relied on data placement [Nandivada and Palsberg 2003]. This architecture is unusual in that it supports loading an eight-byte data value into two separate four-byte registers in a single load instruction, which is ideal for the load coalescing optimization. Furthermore, the eight-byte data item could be aligned on a four-byte boundary, where most architectures would require eight-byte address alignment for an eight-byte load. With these advantages, they formulated the placement problem as an integer linear program (ILP) and used a commercial ILP solver as a library routine to determine

a near-optimal placement of scalars. The execution time reductions ranged from 0.8% to 15.1% on the benchmarks tested. However, they make no mention of cache effects or cache measurements, so it is not clear how to separate the cache effects of their placement optimization from the load coalescing effects. The optimization was not integrated with a cache-conscious data placement optimization. In addition, their peephole optimization phase coalesces non-scalar loads and stores where this can be done without loop unrolling, and no measurements are given to separate the benefits of these non-placement-related coalescings from the benefits derived from the placement-related coalescings.

# 2.6 Reducing Range-Dependent Addressing Costs

No prior work in reducing addressing costs of global variables for general purpose processors through data placement existed when this research began. Srivastava and Wall performed a link-time optimization for the Alpha AXP processor that reduced accesses to the Global Address Table (GAT) that was used for accessing all global variables on that machine [Srivastava and Wall 1994]. As on many machines, the Alpha collected the addresses of all globals accessed in a function into a GAT for that function. In order to load the value of a global variable, two memory accesses were required. The first access loaded the address of the global variable from its entry in the GAT, and then the second memory access used that address to load the value of the global variable. Separate GATs were created for each function because of a lack of knowledge at compile time concerning program size, distances between function, separate compilation units, dynamic and shared libraries, etc. At link time, however, the entire program is visible, and GATs for adjacent functions can be merged, the global pointer register can be made to point to a merged GAT and thus does not have to be saved and restored around function calls, etc. Some variables might be within immediate offset range of the global pointer register; thus, instead of using the global pointer register to load the address of the global from the GAT, the value of the global could be loaded in one step. No rearranging of data was performed in this optimization, although the linker changed code sequences. An average improvement of just more than 3 percent was seen on the benchmarks tested.

As this dissertation was being completed, two new papers have been published on reducing addressing costs for global variables by means of link-time [Haber et al. 2003] and post-link-time [Luk et al. 2004] optimizations. The link-time work of Haber et al. placed global data in order of its frequency of use and positioned the IBM PowerPC GAT just before the most frequently accessed data item. This permits some two-step accesses to the most frequently accessed variables to be made in one step by using an immediate offset from the global pointer register. Furthermore, the grouping by frequency of access makes an indirect improvement on data locality and hence should reduce cache misses. A profiling run is made first, then the link-time optimization uses the profiling data as feedback. Because the data reordering is not aimed specifically at reducing cache misses, but only at increasing opportunities to optimize the instruction sequences, the data reordering itself had a negative effect on five of the ten benchmarks, a negligible effect on two others, and a positive effect on the other three benchmarks. The reductions in accesses to the GAT overcame these problems and produced an average improvement in execution time of three percent.

The post-link-time optimizations of Luk et al. on the Itanium processor included a large set of diverse optimizations, making it hard to separate the benefits of each from the rest. These optimizations included code placement, data placement, code prefetching, data prefetching, GAT addressing reduction, function inlining, dead-code elimination, branch forwarding, and store-load forwarding. The first four (code and data placement and prefetching) were considered the most significant by the authors. In one pathological case, a hot spot for cache thrashing in consecutive accesses to heap-allocated variables was corrected by inserting prefetch instructions into the SPECint2000 benchmark 181.mcf. This reduced execution time by forty percent. Even with this improvement, the geometric mean across the benchmarks tested was about eight percent, with most benchmarks in the two to four percent improvement range. This research is notable for its use of performance counters to gain a statistical profile, which involves much less overhead than the typical dynamic profiling by code instrumentation. The data placement was done to reduce cache misses, and the GAT access reductions were then obtained from the final data layout. The data placement was shown to increase the opportunities for GAT addressing optimizations, but the placement was not tuned specifically for that purpose.

Chapter 2: Related Work Heap Optimizations 17

# 2.7 Heap Optimizations

Grunwald, Zorn and Henderson demonstrated the cache and paging inefficiencies of memory allocators that concern themselves only with space efficiency [Grunwald et al. 1993]. More recent work has measured the improvements in various locality-sensitive allocation algorithms [Chilimbi and Larus 1998, Boehm 2000].

Kistler and Franz observed that many operations on recursive data structures that reside in the heap, such as linked lists, involve nothing more than accessing the key field of a list item, comparing it to some value, and then following a pointer to the next item in the list [Kistler and Franz 2000]. Given that fact, it would be very advantageous to have the key field and the pointer to the next element in the list reside in the same cache line, regardless of how the data structure was defined by the programmer. Furthermore, they claimed that it is faster to access the words within a cache line approximately in order, avoiding the pathological case in which the n-th word is accessed, and then immediately the (n-1)-st word is accessed, on a cache miss. In this case, the load-forwarding hardware will return the cache line from memory in the wrapped around order that starts with the *n*-th word and concludes with the (n-1)-st word, and the request for the (n-1)-st word will have to wait for the cache line fill operation to complete, creating stall cycles. Using a dynamic path profiling and dynamic (i.e. run-time) optimizer for the language Oberon-2, they profiled the fields within structures (i.e. heterogeneous data objects) and created a temporal relationship graph (TRG) for each structure. Using the TRG, recursive graph bipartitioning (i.e. bisecting) is used to divide each structure into smaller and smaller clusters of data fields until the size of a cache line is reached. Fields are arranged within cache lines to avoid penalties in cache-line-fill hardware, as well as to reduce memory bank conflicts. No measurements of the effectiveness of these rearrangings within the cache lines are provided. Six benchmarks that intensively allocate heap objects are optimized and measured, with execution speedups ranging from 1.03, 1.04, and 1.15 at the low end, to 1.30, 1.69 and 1.96 (i.e. almost a 50%) reduction in execution time) at the high end. When considering the runtime cost of continual path profiling and optimization, the numbers worsened only slightly, with one speedup dropping into the negative range and the others coming close to their original improvements. Work similar to this research was also performed by Chilimbi and Larus et al. [Chilimbi et al. 1999a, Chilimbi et al. 1999b].

#### 2.8 Cache Conscious Data Placement

Panda, Dutt, and Nicolau examined the placement of global scalar and array variables to reduce cache misses in the CW4001 embedded processor from LSI Logic [Panda et al. 1997]. The data cache for typical configurations of this embedded CPU core are only 256 bytes, and extremely small and simple benchmarks were used. A simple greedy algorithm is used to cluster scalars together into cache lines, and then all cache-line-sized clusters are placed relative to each other to minimize cache conflicts. Finally, arrays are placed with a greedy method that uses gaps between arrays as needed to minimize conflicts. Nothing is said about placing the clusters of scalar variables in order to minimize conflicts with the arrays, or vice versa. The embedded processor used has no TLBs or virtual memory paging behavior to be addressed. Both a direct-mapped and a two-way associative data cache are measured. The benchmarks measured were tight loops and kernels with single-digit numbers of array variables and a similar number of scalar variables. Execution time speedups ranged from zero to almost a 50% time reduction for the direct-mapped 256 byte data cache, and from zero to almost a 40% reduction for the two-way associative data cache. Average speedup factors were 1.34 and 1.21 for these two caches. All measurements were from a simulator of the embedded CPU running on a workstation.

Calder, Krintz, John, and Austin published the most comprehensive approach to data placement to date [Calder et al. 1998]. Their work was a successor to a portion of Austin's dissertation [Austin 1996]. In that dissertation research, Austin modified executable code to create unique global names for all stack, global, and heap variables, profiled these variables during execution, and then used straightforward greedy algorithms to place the global data objects relative to each other to reduce cache conflicts. Then, the entire stack frame was treated as a single large object (no rearranging of data within stack frames was done), and placed at a starting offset to minimize conflicts between stack and global data. Finally, heap objects, identified by the line number of their creation and the procedure stack backtrace at the time of their creation (to model different paths to the same allocation points), were placed to reduce intra-heap conflicts. This placement was accomplished with a custom heap allocator that would accept cache offset hints inserted by the compiler. This work was extended by Calder et al. to use a TRG (temporal relationship graph) as the profiling data structure, and to place the stack relative to the global constants only, while placing the global and heap variables in one final integrated step. Small globals were grouped together on the basis of temporal locality to create spatial locality within cache lines. A 23.75% reduction in data cache misses (in an 8KB direct mapped first level cache) was measured, with 70% of the reduction coming within global variables and 25% from stack variables while only a little over 3% came from heap variables and 1% from global constants. Page locality worsened slightly. Execution time results were not given, although it was mentioned that the custom heap allocator that must take cache hints into account at run time might not be worth the price that is paid, given the small reduction in heap object cache misses on most of the benchmarks used. Increased spatial locality within cache lines was not measured.

Petrank and Rawitz recently proved that cache conscious data placement is in "the small family of extremely inapproximable optimization problems" [Petrank and Rawitz 2002]. That is, "if  $P \neq NP$ , then one cannot efficiently approximate the optimal solution even up to a very liberal approximation ratio." They demonstrate that, even if all profiling and accompanying data structure problems were solved to perfection, so that the placement algorithm had a complete ordered list of the memory references that will be made, a polynomial time placement algorithm still cannot approximate the optimal placement within any positive  $\varepsilon$ . Furthermore, they demonstrate that, given the kind of profiling information usually available (i.e. pairwise conflict metrics between pairs of data items), not even an exponential time algorithm can find a solution that is within an factor of k- $\beta$  of the optimal cache miss reduction, where k is the number of blocks in the cache. Thus, the best that can be hoped for is to find good heuristics that will work well for a large number of benchmark programs.

# 2.9 The Potential for Improvement on Prior Work

Having reviewed the relevant work, we can find the motivation for new research that improves upon these efforts in several ways:

- The fact that the memory-to-cache bus is an element of the memory hierarchy to be used more efficiently has received little or no attention in most data placement work.

- Placing data to minimize use of the expensive addressing operations that are needed for data located far from the value held in an address register has only been addressed at link time or later, and only as a by-product of data placement, or even in the absence of data placement. Data placement has not been designed during compilation to maximize the effectiveness of the later address cost minimization. Architectures such as the Sun UltraSparc family [Weaver and Germond 2000], which does not use a global address table, will not benefit from past research efforts without considerable tailoring of the optimizations.

- The best code and data placement efforts have relied upon profiling runs that take an impractically long time to run, discouraging adoption of this research into commercial compilers.

- Many published results have targeted very small caches. The benefits of various cache miss reduction efforts have been known to lessen dramatically as cache sizes increase, calling into question just how useful some of the prior optimizations are for modern cache hierarchies. Measurements on first-level caches larger than 8KB are needed, along with measurements of second-level cache misses.

- Prior data placement research has targeted direct-mapped caches, with descriptions of (often complicated) extensions that could be implemented to target caches with higher associativity.

- Minimizing conflicts between code and data in unified levels of cache has been talked about as "future work" for years but never studied, or even measured for its potential impact throughout the cache hierarchy.

- Prior data placement algorithms have been fairly simple greedy algorithms, generally starting with the most used data item, then placing the next most used data item

in relation to the first item, etc. Global optimization algorithms, such as grouping data items by mutual temporal affinity before final placement, have not been studied.

This research addresses these deficiencies.

# Chapter 3

## **Data Affinity Analysis**

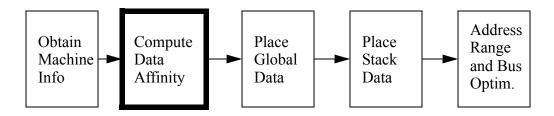

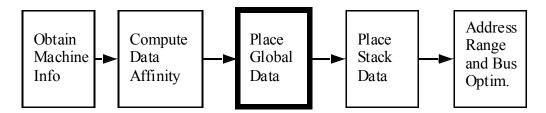

Before discussing the topic of this chapter in depth, it will be helpful to have an overview diagram of the entire research. This diagram will be repeated in later chapters as a reminder of where each chapter's subject fits into the overview.

The first box in the diagram indicates that there are certain items of information about the cache hierarchy, such as size, line size, associativity, etc., that are needed for the other stages of the research. Discussion of how to obtain this information, along with discussion of the effort needed to retarget the analyses and optimizations from one machine to another, is deferred until Chapter 6.

Once this information is obtained, analyzing the user program that is being compiled can begin. This box is highlighted as it is the subject of the current chapter. The affinity information for global data that is computed in this stage is used in the next stage to place all global data. A much simplified data affinity computation is performed within the following box, in order to provide the information needed to place stack data (i.e. reorder local variables within each function in the program). Finally, the reordered local and global data enables the optimization of address computations and the minimization of bus cycles through memory access coalescing in the last box.

It should be noted that there are large time gaps in this diagram. The first box represents an offline process that takes place as part of the design of the compiler, not at com-

5/6/04 22

pilation time. A program is described in Chapter 6 to automatically provide most of the data needed.

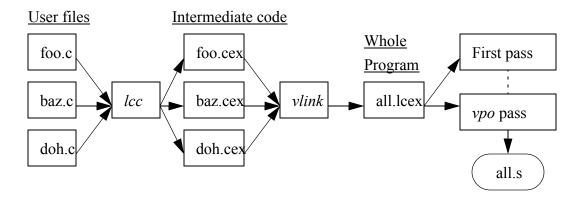

When performing any whole-program optimizations, the compiler used in this research, *vpo* [Benitez 1994], is used in a multi-stage sequence, as shown in the diagram below:

The processing of the application program can be described at a high level, as follows:

- 1. The *lcc* compiler front end is used to check the correctness of the source code and translate each source code file into the corresponding intermediate code file.

- 2. A separate tool, called *vlink*, collects the intermediate code form of all files in the user program and merges them into a single intermediate code file. This tool is described later in this chapter.

- 3. A first pass over the intermediate code for the whole program builds a call graph for the program, builds a global variables symbol table, and annotates the intermediate code with lists of the loads and stores made in each basic block of the program. The latter operation is the first part of the data affinity analysis stage.

- 4. As the end of each function is reached in this first pass, a simplified representation of the function is produced, containing little besides the lists of loads and stores made by each basic block. A call graph node for the function is created, and the simplified representation of the function is attached to the call graph node.

- 5. After the end of the last function in the whole program is reached in this first pass, the call graph is processed for use by other optimizations besides the ones in this research. For example, arcs between call graph nodes indicate which nodes call other nodes. When this processing

is finished, the simplified representations of each function are inlined into their callers until eventually only the main() function remains. This function now contains a representation of the global data accesses for the whole program.

- 6. The whole-program simplified representation is now traversed in numerous paths, with each path used to record the temporal affinity of data items on the path.

- 7. Data placement takes place after data affinity analysis.

- 8. A second pass (the *vpo* pass) over the intermediate code for the whole program now takes place, after rewinding the whole program intermediate code file (all.lcex) to the beginning. This pass is the same as the only pass that normally takes place when no whole-program optimizations are performed. *vpo* applies all of its optimizations to each function in isolation during this pass. The dotted line connecting the first pass to the *vpo* pass indicates that data structures, such as the global symbols list, can be passed from the first pass to the *vpo* pass if they are useful in optimizations performed in the *vpo* pass.

- 9. At the end of each function in this second pass, *vpo* sets up the prologue and epilogue code in a machine-dependent way for the function, and then generates the assembly language form of the function into the output file (all.s). Just before the generation of assembly language, the placing of stack data, addressing range optimization, and bus cycle (coalescing) optimization are performed, as shown in the final two boxes of the diagram above.

10. The linker is called to translate the assembly language into an executable form (not shown).

In summary, the first box in the first diagram at the beginning of the chapter, *Obtain Machine Info*, is done offline. The second box, *Compute Data Affinity*, is done in pieces during the first pass over the whole-program intermediate code file. The third box, *Place Global Data*, is done at the end of the first pass over the intermediate code file. The final two boxes, *Place Stack Data* and *Address Range and Bus Optimizations*, are done at the end of the processing of each function in the second (*vpo*) pass over the intermediate code file for the whole program.

Now that the diagrams have been described and the analysis stage placed in the proper temporal context, the subject of this chapter, data affinity analysis, will be discussed in detail.

## Introduction

In order to reduce conflict misses and compulsory misses in the memory hierarchy, the data placement algorithms will require a profile of the application program's data access pattern as input. This data profile must accurately reflect the temporal affinity of each data object for other data objects; that is, given that object A has just been accessed in the application program's execution, what other data objects will be accessed within a short period of time in the future? These other objects could evict object A from one or more levels of the memory hierarchy if their addresses cause a conflict. In order to place data so as to minimize cache and TLB conflicts, the temporal data reference pattern of the application program must be characterized. The goal is to produce an affinity array, in which an entry in row i and column j indicates that, after accessing the data object whose profile-assigned index is i, the application program accessed the object with index j a certain number of times within a given time and space window. Thus, the sum of the (i, j) and (j, i) entries in the array will depict the magnitude of the cost of assigning addresses to these two objects that conflict in the level of the cache hierarchy that is being profiled. Because different levels of cache have different capacities and possibly different policies on dealing with misses on data writes (e.g. the first-level data cache could have a write-through policy and not allocate a cache line when a write miss occurs, while the second-level cache could allocate a cache line on each write miss), an affinity array will be maintained for each level of cache. Data affinity analysis, hereafter referred to as data analysis for brevity, is the examination of the application program in such a way as to enable the building of the affinity array for each level of the cache hierarchy.

In this research, the focus will be on the placement of global variables. Placement of local variables will also be performed, but experience shows that few functions have enough local variables to exceed the capacity of the first-level data cache. Also, the original first-level cache research described by Calder et al. reported very little benefit from profiling stack (local) variables and trying to place the starting address of the stack to minimize conflict between global variables and stack variables [Calder et al. 1998].

Profiling of both code execution and data access patterns has been performed in various ways in prior research. These approaches will be summarized briefly in order to motivate the original approach taken in the present research.

# 3.1 Code and Data Profiling in Prior Work

Code profiling attempts to characterize the execution pattern of the application program at either the function level or the basic block level. Code profiling at the function level is exemplified by the tool *gprof* from the Free Software Foundation [Fenlason and Stallman 1992]. When requested by a command-line option, the gcc compiler instruments the executable code by inserting a call to a counter function at the beginning of each function. When the program runs, the counters keep a total of the number of times each function is executed and produce an output file of raw data counts. These counts are summarized by the gprof tool into a readable report. The raw counts file can be read by a compiler during a second compilation pass over the application program; for example, certain expensive optimizations could be targeted only to the most frequently executed functions.

At the basic block level, analysis is more difficult. Both *static* (i.e. during a single compilation) and *dynamic* analysis methods have been developed in past research. Some dynamic methods (i.e. methods that use instrumentation of the executable code, and hence require a profiling run of the application program to produce profiling data) simply extend the basic idea of *gprof* by inserting counters at the beginning of each basic block. At the end of the profiling run, the counters are written into a report file, which can then be related to the basic blocks in the original source code using debugging symbols in the executable file. The Quantify tool from Rational Software uses this method [Pure Software 1995]. Within our own vpo infrastructure, EASE (Environment for Architecture Simulation and Evaluation) provides efficient means to profile at the basic block level [Davidson and Whalley 1991].

It can be more useful for some compiler optimizations to know the sequences of basic blocks (i.e. the paths) that are executed most frequently, rather than a simple basic block execution count. The temporal relationship graph (TRG) that was discussed in Section 2.1 is a means of providing path information at the function level and is useful for code placement optimizations. At the basic-block level, path profiling has been studied in recent years [Ball and Larus 1996, Ammons and Larus 1998, Larus 1999]. The path profiling techniques have been refined to a practical level of efficiency, i.e. the profiling run takes 4-8 times as long as a normal program run. However, only a portion of the program is profiled,

and the results have not been applied to code or data placement. The TRG profiling run, as noted earlier, takes about 25 times as long as a normal program run, which reduces its practicality for most optimization clients. Recent work in Whole Program Streams [Chilimbi 2001] directly address data profiling for data placement and related optimizations by extending the previous path profiling methods to record streams of data references. Presumably profiling runs to generate Whole Program Streams are somewhat slower than the previous path profiling runs, but timings are not reported.

Our understanding of program behavior has been advanced by these dynamic profiling experiments, but they suffer a certain lack of practicality. Not only are the profiling runs quite lengthy for the methods that are useful in placement optimizations, but few software engineers have compiled, at any point in their careers, an application program with feedback from a prior profiling run used to guide optimizations. It is unclear that compiler optimizations that are dependent on any form of dynamic profiling feedback will ever have a widespread impact in the world of computing. As a result, the present research includes the development of novel *static* methods of profiling data access patterns.

Past research in static analysis has centered on the determination of basic block execution frequencies within a function. The compiler used in this research, vpo, has a static analysis subroutine that computes basic block execution frequencies as follows:

- 1. The entry block in the function is given a frequency value of 1.0; that is, it is executed once per call of the function. (All blocks have a value that correspond to the number of times they are expected to be executed on each call to their function.)

- 2. Any block with only one child block simply passes its frequency estimate to its child.

- 3. A block with more than one child evenly divides its estimated frequency value among its children. This means that it is assumed that the two branches in an if-else construct are equally likely to be taken, each case within a switch statement is equally likely to be executed, etc.

- 4. An estimated number of iterations for each loop is factored into each block within that loop as a final step. Nested loops thus have their blocks scaled up by a product of several iteration counts.

Research efforts in static analysis have focused on attaining greater precision than these "rules of thumb" provide. Making a prediction for a non-loop branch that is more precise than the 50-50 rule for an if-else statement has been achieved by developing heuristics based on instrumented observations of a large body of real application programs. Ball and Larus developed heuristics primarily based upon the two possible basic block successors of a branch [Ball and Larus 1993]. For example, if one block started a loop, while the other block avoided the loop, it was observed to be far more common to execute the loop rather than avoid it, so the 50-50 split between the two destinations of the branch statement should be altered to predict a far greater likelihood of entering the target loop. On the other hand, both calls and returns are more often avoided by branches than reached by branches, as they tend to happen often to handle errors and other exceptional conditions. The various heuristics were then combined into a single heuristic decision procedure. While not as accurate as the perfect branch prediction that could be provided by using the same input data for a dynamic profiling training run and the final measured run, their heuristic procedure was far superior to the 50-50 rule. This work was extended to predict the frequency of calls over the whole call graph of a program by Wagner et al. ([Wagner et al. 1994]), in addition to developing new intraprocedural branch prediction heuristics (e.g. if one arm of a conditional branch writes to a variable that is used elsewhere, that arm of the branch is more likely to be taken). Intraprocedural branch prediction was improved further by Patterson using data value range propagation to better determine which branches are likely to be taken [Patterson 1995]. Rather than simply trying to predict which branch is taken more than half the time, as in the other works discussed above, a probability is assigned to each direction of a branch.

In the present research, the existing *vpo* subroutine that uses rather simple rules for non-loop branches has been used. One enhancement was an analysis of the exact iteration count of each loop, where the iteration count is dependent on constants, as is often the case. This enhancement reduces the number of occasions on which the iteration count must be assigned the default value (presently set at 10).

# 3.2 Interprocedural Static Data Analysis

Where most prior research in static analysis has been intraprocedural (and the exception, by Wagner et al., did not attempt to profile data accesses), our static data analysis must be interprocedural. There are several reasons for this requirement: