## **Pre-RTL On-Chip Power Delivery Modeling and Analysis**

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science University of Virginia

> In partial fulfillment of the requirements for the degree Doctor of Philosophy Computer Engineering

> > by

**Runjie Zhang**

May 2015

### Approvals

This dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

**Computer Engineering**

Runjie Zhang

Approved:

Kevin Skadron (Advisor)

Joanne Bechta Dugan (Chair)

Mircea R. Stan (Advisor)

Mary Lou Soffa

David Brooks

Accepted by the School of Engineering and Applied Science:

James H. Aylor (Dean)

May 2015

© Copyright April 2015 Runjie Zhang All rights reserved

### Abstract

The Power delivery network (PDN) is the electrical system that provides supply voltage to the transistors within a silicon chip. Due to the PDN's intrinsic resistance, capacitance, and inductance, the supply voltage can become noisy (drop or fluctuate) and cause timing errors, threatening program correctness. While CMOS technology scaling has resulted in exponentially greater transistor densities, threshold and supply voltages no longer decrease fast enough to prevent exponential growth in on-chip power density. Although the technology of three-dimensional integrated circuit (3D-IC) provides an alternative path toward the continued historical trend of device integration growth, it further increases the aggregated power density by stacking active silicon layers on top of each other.

As a result, power-delivery-related reliability issues are increasing, creating higher demands for the already scarce physical resources like controlled collapse chip connection (C4) pads and silicon area for the integrated on-chip decoupling capacitors. Unfortunately, there often exists a contention between power delivery needs and processor computation needs. Under these rising challenges, it becomes increasingly important to consider PDN design and optimization at early design stages, both to ensure an optimal design point selection in the complicated tradeoff space, and to prevent costly redesign due to power delivery issues.

In this dissertation, we build and validate a pre-RTL PDN model, called VoltSpot, to (1) identify the power-delivery difficulties for contemporary and near-future microprocessors; (2) understand the impact of the PDN's physical resource allocations on voltage noise, and explore the resulting tradeoff space considering the processor's performance and lifetime under electromigration stress; (3) design and evaluate both static and dynamic solutions to mitigate power delivery constraints; (4) assess the benefits and costs of novel power delivery schemes for 3D-IC.

### Acknowledgments

I would like to thank my advisors Prof. Kevin Skadron and Prof. Mircea Stan for guiding me through my journey in graduate school. They taught me how to build and defend an argument, how to present work to peer researchers, and how to make improvements based upon feedback/criticisms. I have learnt much from them, not only about how to become an independent researcher, but also the spirit of professionalism and the art of balancing life and work. I owe a substantial amount of gratitude to their support and trust for allowing me to work remotely during my final semesters, so that I could put an end to my long-lasted two-body problem in much advance.

I wish to thank the members of my Ph.D. committee: Prof. Mary Lou Soffa, Prof. Joanne Bechta Dugan, and Prof. David Brooks for their valuable suggestions and comments. Prof. Brooks' earlier work on architecture-level power noise modeling and management not only helped me to paint the big picture in my mind, but also inspired an important branch of my research work. Through the past several years, Prof. Brett Meyer from McGill University has been continuously helping us with brainstorming new ideas and writing papers. As a UVa research scientist and a numerical expert, Dr. Ke Wang played a key role in the development of VoltSpot's circuit solver, and also brought many novel thoughts into our PDN research. A non-trivial portion of VoltSpot's source code was directly inherited from an existing thermal model HotSpot, which was developed by Dr. Karthik Sankaranarayanan, Dr. Wei Huang, and many others. Dr. Wei Huang also provided many valuable suggestions to us in the early-stage of VoltSpot development. My UVa colleague Kaushik Mazumdar and I collaborated closely in the 3D-IC-related projects. I learned a great deal of IC design and fabrication from our industrial collaborators, which include, but not limited to: Dr. Pradip Bose, Dr. Dale Becker, Dr. Sungjun Chun, Dr. Pritish Parida, Dr. Guoqing Chen, and

Dr. Cheng Zhuo. I want to express my sincere gratitude to all of them. This dissertation would not have been possible without their help.

I am grateful for having so many friends both inside and outside the CS/ECE departments. The members of Kevin's LAVA lab and Mircea's HPLP group have helped me in numerous ways. Especially, I thank Liang Wang, Shuai Che, Jack Wadden and Michael Boyer for their generous help in teaching me software development basics, debating research ideas, and sharing the location of free food. Also, I want to thank my fellow graduate students Yuchen Zhou, Yanqing Zhang, Wei Wang and Yan Huang for setting examples of excellent researchers and motivating me with peer-pressure.

I also want to express my gratitude to Prof. Xueqing Lou from Zhejiang University, China. As an undergraduate student, I took his computer organization class in 2007. That class and his vivid lectures made me discover my interest in computer architecture and decide to pursue a career in this area.

Finally, I want to thank my family for their unconditional love and support. As dedicated engineers themselves, my parents not only inspired my curiosity for the world, but also taught me everything I need to know about how to become a good person. Although my wife Chuhan and I spent the majority of the past six years living in separate cities, states, or even time zones, her wisdom and love could always travel through distance to share my joy and lead me through the most stressful, depressing, and even desperate times in my life. I dedicate this dissertation to all of them.

This work was supported by SRC grant 2009-HJ-2042, NSF grant no. CRI-0551630, NSF grant CNS-0916908 and MCDA-0903471, and DARPA MTO under contract no.HR0011-13-C-0022.

## Contents

| A | Acronym List xvi |             |                                                 |    |  |

|---|------------------|-------------|-------------------------------------------------|----|--|

| 1 | Intr             | ntroduction |                                                 |    |  |

|   | 1.1              | Overvi      | iew                                             | 1  |  |

|   | 1.2              | Power       | Delivery Network and Supply Voltage Noise       | 3  |  |

|   | 1.3              | PDN F       | Resource Scarcity and Optimization              |    |  |

|   | 1.4              | PDN S       | Simulation and Modeling                         | 7  |  |

|   | 1.5              | Run-ti      | me Voltage Noise Mitigation Techniques          |    |  |

|   | 1.6              | Electro     | omigration and Long-term PDN Reliability Issues | 10 |  |

|   | 1.7              | 3D-IC       | and Voltage-Stacked Power Delivery              | 12 |  |

|   | 1.8              | Disser      | tation Organization                             | 14 |  |

| 2 | Volt             | Spot: A     | pre-RTL Power Delivery Network Model            | 15 |  |

|   | 2.1              | Overvi      | iew                                             | 15 |  |

|   | 2.2              | Relate      | d Work                                          | 16 |  |

|   | 2.3              | Model       | ing Methodology                                 | 17 |  |

|   |                  | 2.3.1       | Input/Output                                    | 17 |  |

|   |                  | 2.3.2       | Structure                                       |    |  |

|   |                  | 2.3.3       | Numerical Engine                                | 20 |  |

|   | 2.4              | Improv      | vements Beyond State-of-the-Art Models          | 20 |  |

|   |                  | 2.4.1       | Modeling Granularity                            | 20 |  |

|   |                  | 2.4.2       | Explicit Multi-layer Model                      | 22 |  |

#### Contents

|   | 2.5  | Valida   | tion                                                           | 23 |

|---|------|----------|----------------------------------------------------------------|----|

|   | 2.6  | Interfa  | cing with Other Architecture Level Tools                       | 25 |

|   | 2.7  | Summ     | ary                                                            | 27 |

| 3 | Arcl | hitectur | re Implications of Pads as a Scarce Resource                   | 28 |

|   | 3.1  | Overvi   | iew                                                            | 28 |

|   | 3.2  | Backg    | round and Related Work                                         | 30 |

|   | 3.3  | Simula   | ation Setup                                                    | 32 |

|   |      | 3.3.1    | Multicore Scaling, Power Modeling and Floorplanning            | 32 |

|   |      | 3.3.2    | Power Trace Sampling and Stressmark                            | 33 |

|   |      | 3.3.3    | PDN Parameters and Pad Location Optimization                   | 34 |

|   | 3.4  | Transi   | ent Voltage Noise: Scaling and Effects of C4 Pad Configuration | 35 |

|   |      | 3.4.1    | IR Drop vs. Transient Noise                                    | 35 |

|   |      | 3.4.2    | Scaling Trends of Supply-Voltage Noise                         | 35 |

|   |      | 3.4.3    | Voltage Noise and Pad Configuration Effects                    | 37 |

|   |      | 3.4.4    | Sensitivity Study                                              | 39 |

|   | 3.5  | Run-ti   | me Voltage Noise Mitigation                                    | 41 |

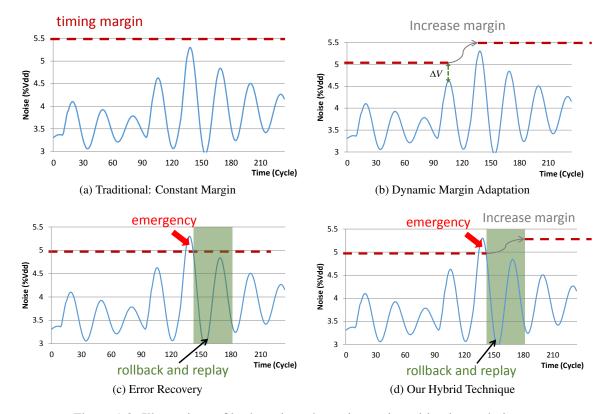

|   |      | 3.5.1    | Dynamic Margin Adaptation                                      | 41 |

|   |      | 3.5.2    | Recovering From Noise-Induced Errors                           | 43 |

|   |      | 3.5.3    | A Hybrid Technique                                             | 44 |

|   |      | 3.5.4    | Trading Power Pads for Performance                             | 45 |

|   |      | 3.5.5    | Impact of I/O routing                                          | 46 |

|   | 3.6  | Chip I   | /O Bandwidth and C4 EM Lifetime                                | 47 |

|   |      | 3.6.1    | Whole-Chip Electromigration MTTF Calculation                   | 48 |

|   |      | 3.6.2    | Tolerating Pad Failures with Runtime Mitigation                | 49 |

|   |      | 3.6.3    | EM Lifetime Considering Pad Failure Tolerance                  | 51 |

|   |      | 3.6.4    | Impact of On-Chip Metal                                        | 52 |

|   | 3.7  | Summ     | ary                                                            | 52 |

viii

#### Contents

| 4 A | St | atistica | l Analysis of EM-induced C4 Bumps Wearout                              |  |

|-----|----|----------|------------------------------------------------------------------------|--|

| 4.  | .1 | Overvi   | ew                                                                     |  |

| 4.  | .2 | Backg    | round and Related Work                                                 |  |

|     |    | 4.2.1    | Single Bump EM Failure                                                 |  |

|     |    | 4.2.2    | Consequences of Power-Supply Bump Failures                             |  |

|     |    | 4.2.3    | Related Work on Statistical EM Analysis                                |  |

| 4.  | .3 | Statisti | cal Simulation of Bump Failures                                        |  |

|     |    | 4.3.1    | Monte Carlo Simulation and Results Confidence Level                    |  |

|     |    | 4.3.2    | Capturing the Impact of Current Re-distribution                        |  |

|     |    | 4.3.3    | MCS Framework for Bump Failure Study                                   |  |

|     |    | 4.3.4    | Supporting Other Random Failures                                       |  |

| 4.  | .4 | Simula   | tion Methodology                                                       |  |

|     |    | 4.4.1    | PDN Modeling                                                           |  |

|     |    | 4.4.2    | Multicore Processor Power, Area and Floorplan Modeling                 |  |

| 4.  | .5 | Result   | s and Discussions                                                      |  |

|     |    | 4.5.1    | The Avalanche Effect: How Bad Is It?                                   |  |

|     |    | 4.5.2    | Achieving Target MTTF with Reduced Bump Count                          |  |

|     |    | 4.5.3    | Impact of Multiple On-Chip Power Domains                               |  |

|     |    | 4.5.4    | Using Graceful Performance Degradation Schemes to Extend Chip Lifetime |  |

|     |    | 4.5.5    | Transient Noise Evaluation                                             |  |

| 4.  | .6 | Summ     | ary                                                                    |  |

| 5 A | Cr | oss-La   | yer Exploration of Voltage-Stacked PDN in Many-Layer 3D-IC             |  |

| 5.  | .1 | Overvi   | ew                                                                     |  |

| 5.  | .2 | Backg    | round and Related Work                                                 |  |

|     |    | 5.2.1    | Power Delivery Challenges and Solution in the Era of 3D-IC             |  |

|     |    | 5.2.2    | Voltage Regulation in V-S PDN                                          |  |

|     |    | 5.2.3    | System-level Evaluation of V-S                                         |  |

ix

| 5.3       Modeling Methodologies       80         5.3.1       SC Converter Modeling       80         5.3.2       PDN Modeling for 3D-IC       82         5.3.3       EM-induced System Lifetime Calculation       83         5.4       Simulation Setup       84         5.4.1       Many-core Processor Modeling       84         5.4.2       PDN Modeling and TSV Configurations       85         5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93 <b>7 transient Noise in Voltage-Stacked PDNs</b> 95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Regulation in V-S PDN       97         6.2.3       System-level Supply Voltage Noise Modeling       97         6.3.1       A Transient Model for SC Converters       99         6.3.1       A Transient Model for SC Converters       99         6.3.2 <th></th> <th></th> <th></th> <th></th> <th></th> |   |     |                                                                                   |                                            |                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------|

| 5.3.2       PDN Modeling for 3D-IC       82         5.3.3       EM-induced System Lifetime Calculation       83         5.4       Simulation Setup       84         5.4.1       Many-core Processor Modeling       84         5.4.2       PDN Modeling and TSV Configurations       85         5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Regulation in V-S PDN       97         6.3.2       Voltage Regulation in V-S PDN       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4.1       Many-                                                         |   | 5.3 | Model                                                                             | ing Methodologies                          | 80                                                                   |

| 5.3.3       EM-induced System Lifetime Calculation       83         5.4       Simulation Setup       84         5.4.1       Many-core Processor Modeling       84         5.4.2       PDN Modeling and TSV Configurations       85         5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Regulation in V-S PDN       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                            |   |     | 5.3.1                                                                             | SC Converter Modeling                      | 80                                                                   |

| 5.4       Simulation Setup       84         5.4.1       Many-core Processor Modeling       84         5.4.2       PDN Modeling and TSV Configurations       85         5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.3       System-level Supply Voltage Noise Modeling       97         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                              |   |     | 5.3.2                                                                             | PDN Modeling for 3D-IC                     | 82                                                                   |

| 5.4.1       Many-core Processor Modeling       84         5.4.2       PDN Modeling and TSV Configurations       85         5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                      |   |     | 5.3.3                                                                             | EM-induced System Lifetime Calculation     | 83                                                                   |

| 5.4.2       PDN Modeling and TSV Configurations       85         5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.3.3       System-level Supply Voltage Noise Modeling       97         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                     |   | 5.4 | Simula                                                                            | ation Setup                                | 84                                                                   |

| 5.5       Results and Discussions       86         5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         5       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                 |   |     | 5.4.1                                                                             | Many-core Processor Modeling               | 84                                                                   |

| 5.5.1       Heat Removal and Power Delivery in 3D-IC       86         5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                       |   |     | 5.4.2                                                                             | PDN Modeling and TSV Configurations        | 85                                                                   |

| 5.5.2       EM-Induced TSV/C4 Pad Lifetime       88         5.5.3       Load-Imbalance-Induced Voltage Noise       89         5.5.4       System Power Efficiency       92         5.6       Summary       93 <b>7</b> Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.2.3       System-level Supply Voltage Noise Modeling       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                            |   | 5.5 | Result                                                                            | s and Discussions                          | 86                                                                   |

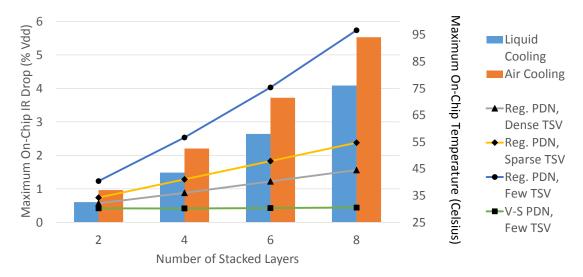

| 5.5.3Load-Imbalance-Induced Voltage Noise895.5.4System Power Efficiency925.6Summary937Transient Noise in Voltage-Stacked PDNs956.1Overview956.2Background and Related Work966.2.1Voltage Noise and Timing Margin in 3D-IC966.2.2Voltage Regulation in V-S PDN976.2.3System-level Supply Voltage Noise Modeling976.3V-S PDN Modeling Methodologies996.3.1A Transient Model for SC Converters996.3.2Validation1006.3.3Whole-system Model1026.4Simulation Setup1026.4.1Many-core Processor Modeling1026.4.2PDN Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     | 5.5.1                                                                             | Heat Removal and Power Delivery in 3D-IC   | 86                                                                   |

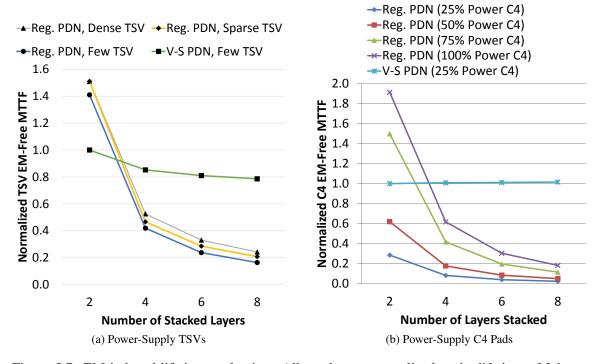

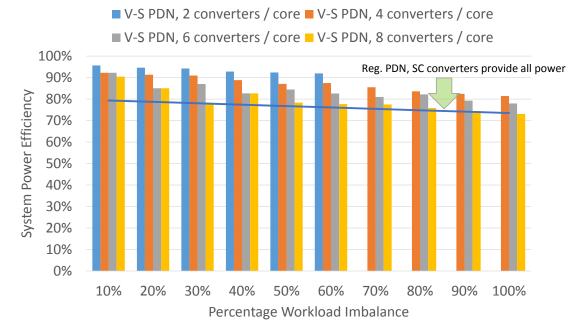

| 5.5.4       System Power Efficiency       92         5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.2.3       System-level Supply Voltage Noise Modeling       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                   |   |     | 5.5.2                                                                             | EM-Induced TSV/C4 Pad Lifetime             | 88                                                                   |

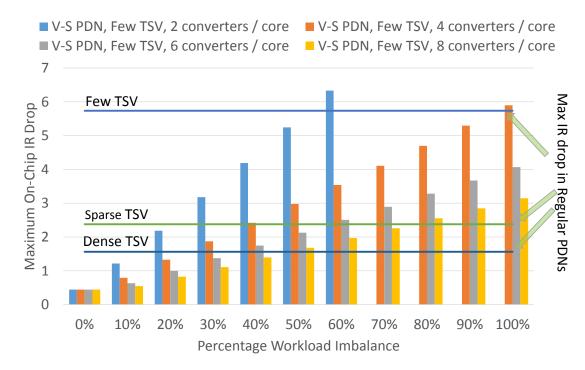

| 5.6       Summary       93         7       Transient Noise in Voltage-Stacked PDNs       95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.2.3       System-level Supply Voltage Noise Modeling       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     | 5.5.3                                                                             | Load-Imbalance-Induced Voltage Noise       | 89                                                                   |

| <b>Transient Noise in Voltage-Stacked PDNs</b> 95         6.1       Overview       95         6.2       Background and Related Work       96         6.2.1       Voltage Noise and Timing Margin in 3D-IC       96         6.2.2       Voltage Regulation in V-S PDN       97         6.2.3       System-level Supply Voltage Noise Modeling       97         6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | 5.5.4                                                                             | System Power Efficiency                    | 92                                                                   |

| 6.1Overview956.2Background and Related Work966.2.1Voltage Noise and Timing Margin in 3D-IC966.2.2Voltage Regulation in V-S PDN976.2.3System-level Supply Voltage Noise Modeling976.3V-S PDN Modeling Methodologies996.3.1A Transient Model for SC Converters996.3.2Validation1006.3.3Whole-system Model1026.4Simulation Setup1026.4.1Many-core Processor Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 5.6 | Summ                                                                              | ary                                        | 93                                                                   |

| 6.1Overview956.2Background and Related Work966.2.1Voltage Noise and Timing Margin in 3D-IC966.2.2Voltage Regulation in V-S PDN976.2.3System-level Supply Voltage Noise Modeling976.3V-S PDN Modeling Methodologies996.3.1A Transient Model for SC Converters996.3.2Validation1006.3.3Whole-system Model1026.4Simulation Setup1026.4.1Many-core Processor Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | T   | •                                                                                 |                                            | 07                                                                   |

| 6.2Background and Related Work966.2.1Voltage Noise and Timing Margin in 3D-IC966.2.2Voltage Regulation in V-S PDN976.2.3System-level Supply Voltage Noise Modeling976.3V-S PDN Modeling Methodologies996.3.1A Transient Model for SC Converters996.3.2Validation1006.3.3Whole-system Model1026.4Simulation Setup1026.4.1Many-core Processor Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6 |     |                                                                                   |                                            |                                                                      |

| 6.2.1Voltage Noise and Timing Margin in 3D-IC966.2.2Voltage Regulation in V-S PDN976.2.3System-level Supply Voltage Noise Modeling976.3V-S PDN Modeling Methodologies996.3.1A Transient Model for SC Converters996.3.2Validation1006.3.3Whole-system Model1026.4Simulation Setup1026.4.1Many-core Processor Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 6.1 | Overv                                                                             | iew                                        | 95                                                                   |

| 6.2.2Voltage Regulation in V-S PDN976.2.3System-level Supply Voltage Noise Modeling976.3V-S PDN Modeling Methodologies996.3.1A Transient Model for SC Converters996.3.2Validation1006.3.3Whole-system Model1026.4Simulation Setup1026.4.1Many-core Processor Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 6.2 | Backg                                                                             | round and Related Work                     | 96                                                                   |

| 6.2.3 System-level Supply Voltage Noise Modeling976.3 V-S PDN Modeling Methodologies996.3.1 A Transient Model for SC Converters996.3.2 Validation1006.3.3 Whole-system Model1026.4 Simulation Setup1026.4.1 Many-core Processor Modeling1026.4.2 PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     | 6.2.1                                                                             | Voltage Noise and Timing Margin in 3D-IC   | 96                                                                   |

| 6.3       V-S PDN Modeling Methodologies       99         6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     | 6.2.2                                                                             | Voltage Regulation in V-S PDN              | 97                                                                   |

| 6.3.1       A Transient Model for SC Converters       99         6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     | 6.2.3                                                                             | System-level Supply Voltage Noise Modeling | 97                                                                   |

| 6.3.2       Validation       100         6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 6.3 | V-S PI                                                                            | DN Modeling Methodologies                  | 00                                                                   |

| 6.3.3       Whole-system Model       102         6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     |                                                                                   |                                            | "                                                                    |

| 6.4       Simulation Setup       102         6.4.1       Many-core Processor Modeling       102         6.4.2       PDN Modeling       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     |                                                                                   |                                            |                                                                      |

| 6.4.1Many-core Processor Modeling1026.4.2PDN Modeling102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     | 6.3.1                                                                             | A Transient Model for SC Converters        | 99                                                                   |

| 6.4.2 PDN Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |     | 6.3.1<br>6.3.2                                                                    | A Transient Model for SC Converters        | 99<br>100                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 6.4 | <ul><li>6.3.1</li><li>6.3.2</li><li>6.3.3</li></ul>                               | A Transient Model for SC Converters        | 99<br>100<br>102                                                     |

| 6.4.3 Workload Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 6.4 | <ul><li>6.3.1</li><li>6.3.2</li><li>6.3.3</li><li>Simula</li></ul>                | A Transient Model for SC Converters        | 99<br>100<br>102<br>102                                              |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6.4 | <ul> <li>6.3.1</li> <li>6.3.2</li> <li>6.3.3</li> <li>Simulation 6.4.1</li> </ul> | A Transient Model for SC Converters        | <ul><li>99</li><li>100</li><li>102</li><li>102</li><li>102</li></ul> |

|    | 6.5    | Result   | s and Discussions                                | 104 |

|----|--------|----------|--------------------------------------------------|-----|

|    |        | 6.5.1    | Cross-layer Noise Interference                   | 104 |

|    |        | 6.5.2    | Allocating On-Chip Capacitance: A Tradeoff Study | 106 |

|    |        | 6.5.3    | Impact of 3D Scaling                             | 108 |

|    |        | 6.5.4    | Impact of Package Impedance                      | 109 |

|    | 6.6    | Summ     | ary                                              | 110 |

| 7  | Con    | clusions | s and Future Work                                | 112 |

|    | 7.1    | Disser   | tation Summary                                   | 112 |

|    | 7.2    | Future   | Directions                                       | 114 |

|    |        | 7.2.1    | Pre-RTL Power Delivery Network Modeling          | 114 |

|    |        | 7.2.2    | Statistical Analysis of PDN Wearout              | 115 |

|    |        | 7.2.3    | 3D-IC and Voltage Stacking                       | 116 |

|    |        | 7.2.4    | Other Directions                                 | 116 |

| Bi | bliogı | raphy    |                                                  | 117 |

# **List of Figures**

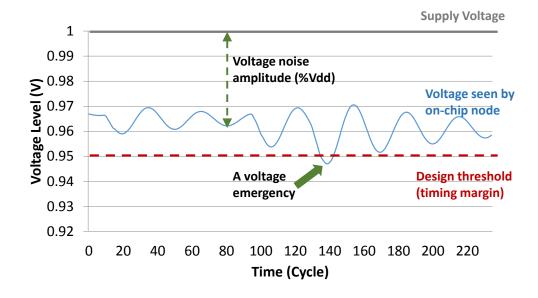

| 1.1 | An illustration of voltage noise and the evaluation metrics.                         | 5  |

|-----|--------------------------------------------------------------------------------------|----|

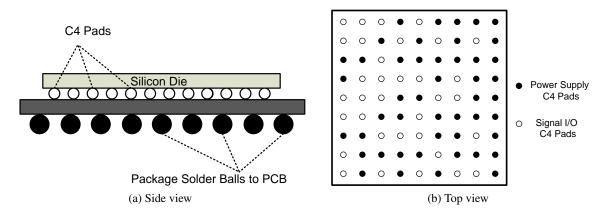

| 1.2 | (a) Side view of a chip showing its connection to the package through C4 pads. (b)   |    |

|     | Top view of a C4 array showing an example allocation of power pads and I/O pads      |    |

|     | (real processors have many more C4 pads than illustrated here)                       | 6  |

| 1.3 | Illustrations of both static and run-time noise mitigation techniques                | 10 |

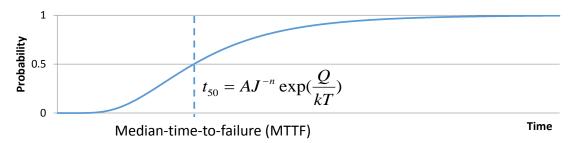

| 1.4 | The log-normal CDF of a single conductor's EM-induced failure time. The y-axis       |    |

|     | shows the conductor's failure probability, or $Prob[Lifetime] \le t. \ldots \ldots$  | 11 |

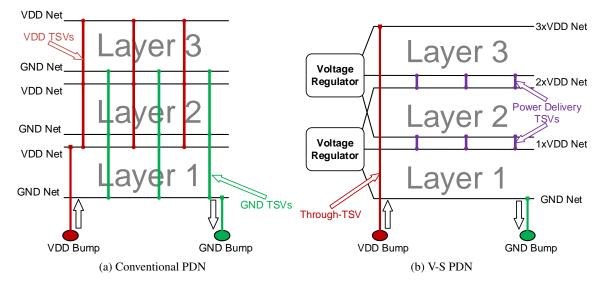

| 1.5 | Conventional and V-S power-delivery scheme for 3D-IC                                 | 13 |

| 0.1 |                                                                                      | 10 |

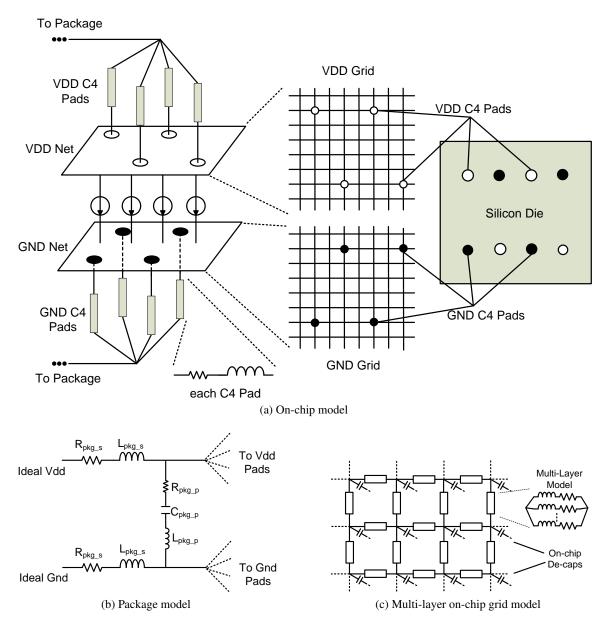

| 2.1 | VoltSpot model structure                                                             | 18 |

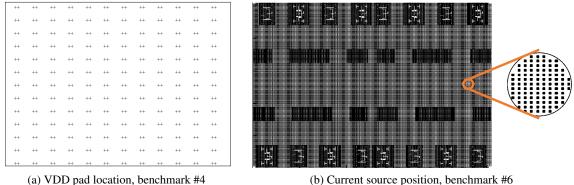

| 2.2 | IBM power grid analysis benchmark: A snap shot                                       | 23 |

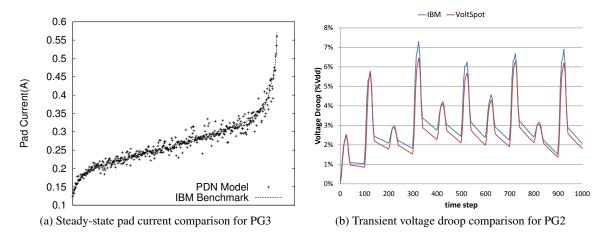

| 2.3 | Current/Voltage comparison between IBM data and VoltSpot results                     | 24 |

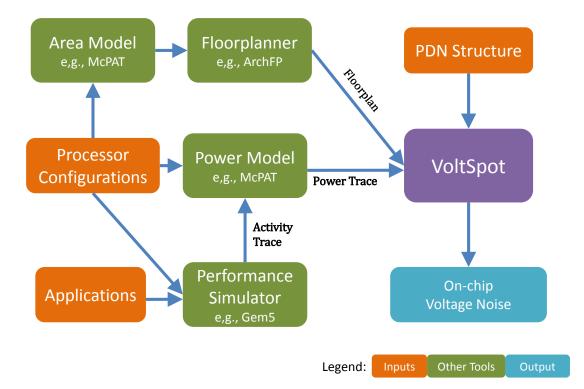

| 2.4 | How VoltSpot interacts with other architecture level tools                           | 26 |

| 3.1 | Voltage-emergency maps for different pad configurations for a 16nm, 16-core chip.    |    |

|     | A total of 1914 C4 locations are available. All three graphs have the same color     |    |

|     | scale; areas with warmer colors indicate more voltage violations                     | 30 |

| 3.2 | Floorplan of the Penryn-like 16core processor.                                       | 32 |

| 3.3 | Comparison of transient voltage noise and static IR drop over a 1K cycle window      |    |

|     | in the benchmark ferret. Periodic oscillation implies that LC resonance is the major |    |

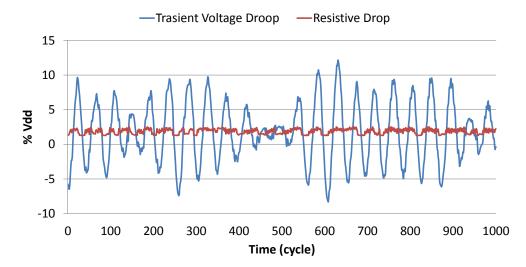

|     | cause. We build our noise-inducing stressmark based on this segment                  | 36 |

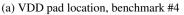

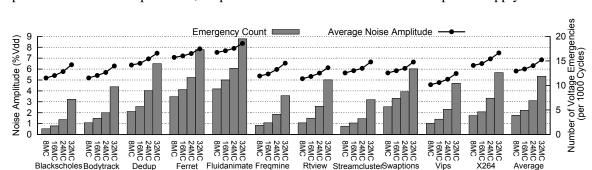

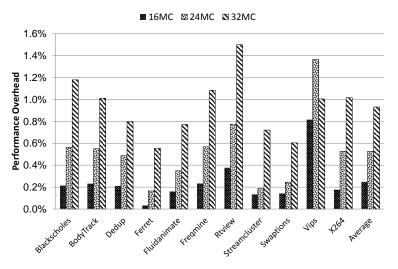

| 3.4  | Voltage noise change across different pad configurations. Each MC needs 30 I/O      |    |

|------|-------------------------------------------------------------------------------------|----|

|      | pads                                                                                | 38 |

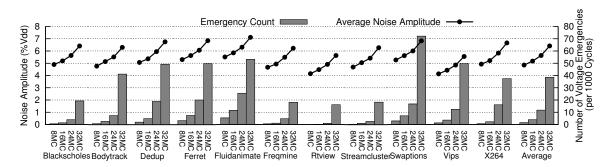

| 3.5  | Voltage noise change across different pad configurations under a different set of   |    |

|      | package parameters                                                                  | 40 |

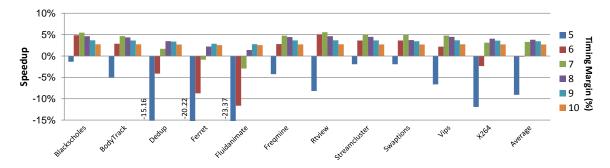

| 3.6  | Speed up of recovery-based techniques with different timing margin settings. We     |    |

|      | evaluate our 16nm, 16core processor with 24MCs here. The baseline case enforces     |    |

|      | a 13% timing margin and thus guarantees timing is error-free                        | 43 |

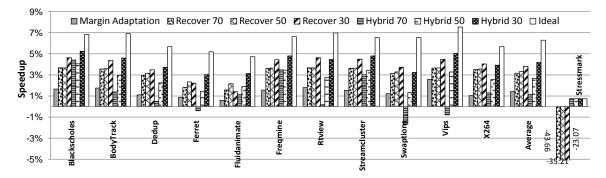

| 3.7  | Performance comparison between different noise mitigation techniques. Numbers       |    |

|      | after recover/hybrid in legend represent the cost (in cycles) of each recover, from |    |

|      | error. The baseline case enforces a 13% constant timing margin.                     | 45 |

| 3.8  | Performance penalty of mitigating extra voltage noise caused by reduced             |    |

|      | power/ground pads. We use the hybrid technique with a conservative assumption       |    |

|      | of 50-cycle rollback-and-replay penalty per error. Each benchmark uses its own      |    |

|      | performance with 8MC case as baseline.                                              | 46 |

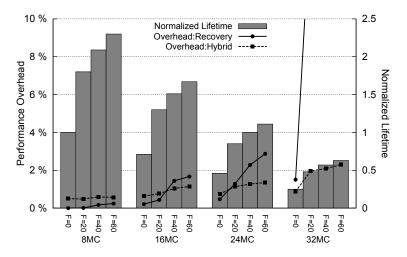

| 3.9  | PDN pad failure's effect on noise mitigation performance overhead and expected      |    |

|      | EM lifetime. $F$ indicates the number of failed pads. The baseline is an 8 MC chip  |    |

|      | with no failed pads. For Recovery, the performance overhead with 32 MC goes         |    |

|      | off-chart to 15% if 20 pads fail (25% if 60 pads fail).                             | 50 |

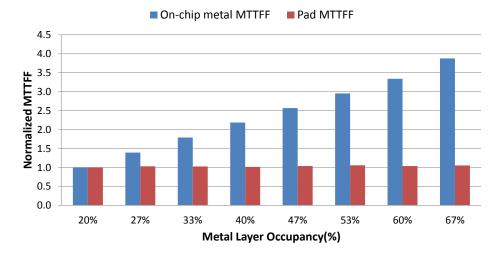

| 3.10 | Impact of on-chip metal occupancy on the EM lifetime of both C4 pads and on-chip    |    |

|      | wires.                                                                              | 52 |

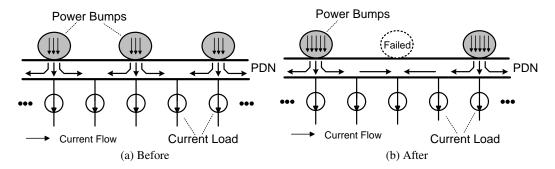

| 4.1  | The consequence of a power bump failure                                             | 58 |

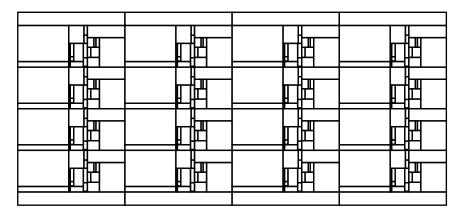

| 4.2  | Floorplan of our example multi-core processor.                                      | 64 |

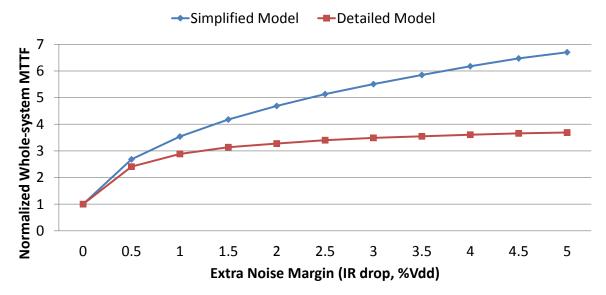

| 4.3  | Normalized whole-system MTTF under different noise margin settings. The differ-     |    |

|      | ences between the two sets of results are caused by the avalanche effect            | 66 |

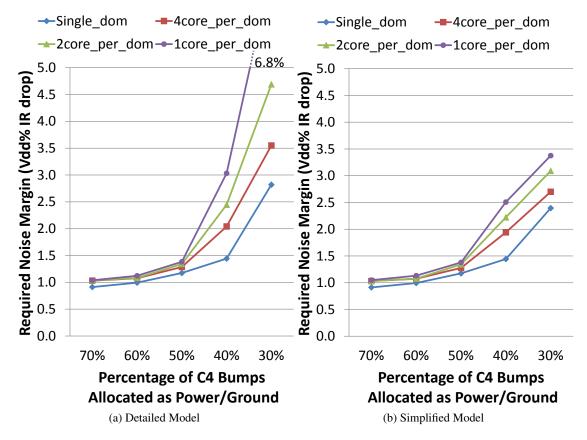

| 4.4  | The required noise margin (in terms of absolute Vdd% IR drop) to achieve target       |    |

|------|---------------------------------------------------------------------------------------|----|

|      | MTTF for different bump allocations and multiple on-chip power domain settings.       |    |

|      | We assume that the target MTTF equals the EM-failure-free time of the single-         |    |

|      | domain chip with 70% bumps as power/ground                                            | 68 |

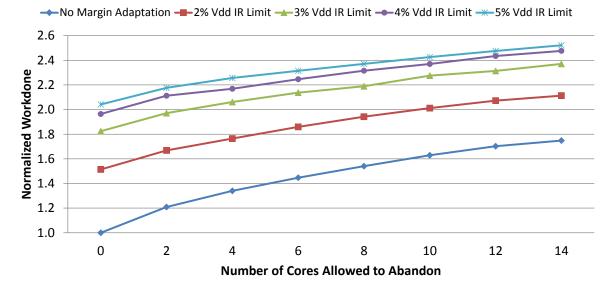

| 4.5  | Evaluation of two graceful performance degradation mechanisms. Margin adapta-         |    |

|      | tion technique gradually relax noise margin until a designated limit (different lines |    |

|      | with 2-5% Vdd). Core desertion scheme abandons a core if its noise exceed the         |    |

|      | design target. All values are normalized to the amount of workdone by the baseline    |    |

|      | chip without any graceful degradation mechanisms enabled                              | 71 |

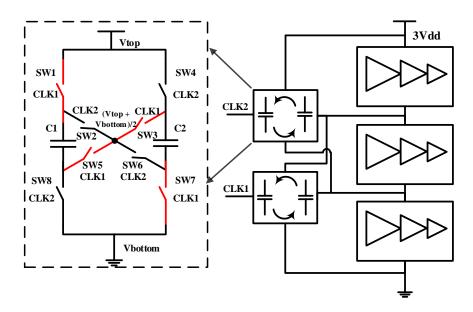

| 5.1  | Stacked loads (three layers) with stacked SC converters (two), ideally providing      |    |

|      | Vdd voltage headroom to each load. Zoomed up single cell of 2:1 push-pull SC          |    |

|      | converter shown on the left.                                                          | 79 |

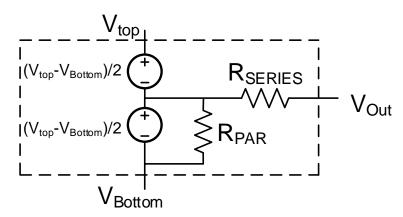

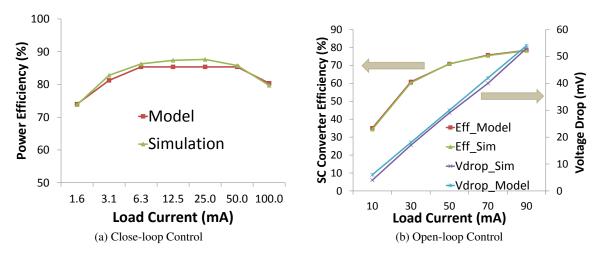

| 5.2  | Power efficiency and voltage drop model for SC converters                             | 80 |

| 5.3  | Model validation results.                                                             | 82 |

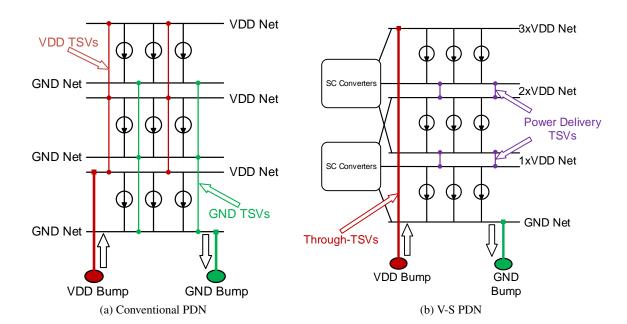

| 5.4  | Conventional and Charge-recycled power-delivery scheme for 3D-IC                      | 83 |

| 5.5  | Floorplan of our single-layer 16-core processor.                                      | 84 |

| 5.6  | Temperature and voltage noise evaluation of our example many-core 3D processors.      |    |

|      | For voltage noise, we tested different power-supply TSV topologies described in       |    |

|      | Table 5.2.                                                                            | 87 |

| 5.7  | EM-induced lifetime evaluation. All results are normalized to the lifetime of 2-layer |    |

|      | V-S PDN 3D-IC.                                                                        | 88 |

| 5.8  | Voltage noise evaluation of our 8-layer processor. For 3D-ICs without V-S, the        |    |

|      | worst-case IR drop happens when all layers are fully active. Therefore the assump-    |    |

|      | tion about workload-imbalance does not affect those evaluations                       | 90 |

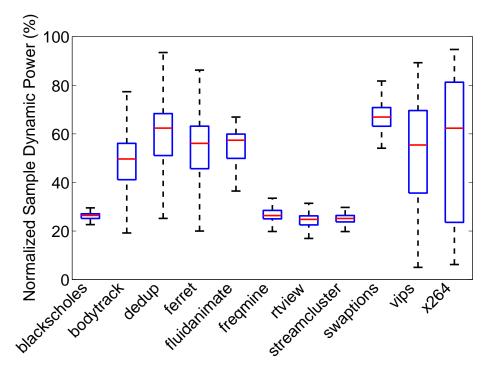

| 5.9  | A box-plot that shows the distributions of workload imbalance within and across       |    |

|      | different applications                                                                | 92 |

| 5.10 | Power efficiency of 3D processors with V-S PDN                                        | 93 |

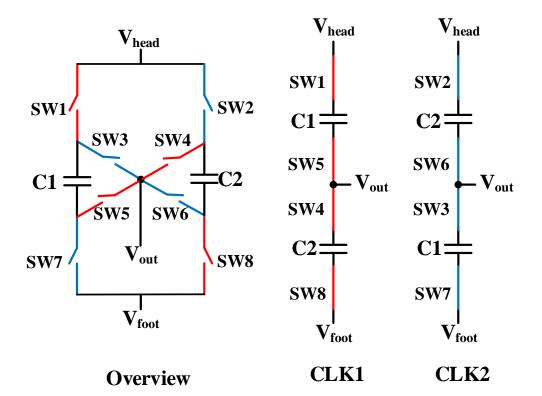

| 6.1 | A single cell of our 2:1 push-pull SC converter and its equivalent circuits in the two |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | different clock phases.                                                                | 98  |

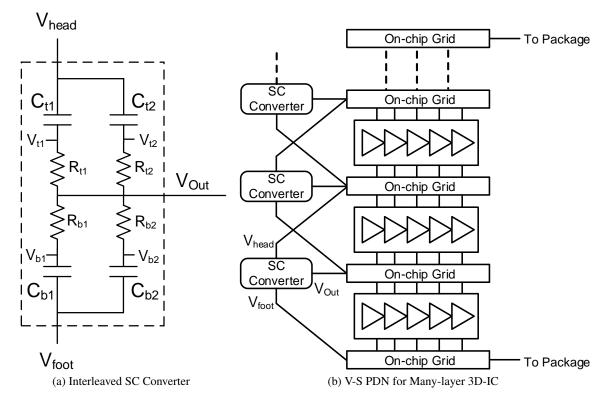

| 6.2 | An RC model for the interleaved SC converters and a whole-system view of a V-S         |     |

|     | PDN in a many-layer 3D-IC                                                              | 99  |

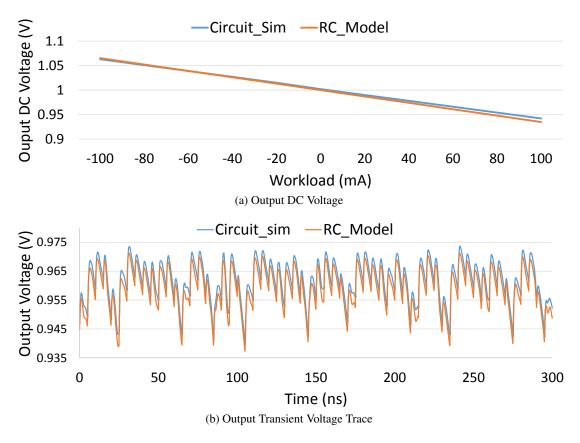

| 6.3 | Validation results.                                                                    | 101 |

| 6.4 | A plot of per-layer maximum noise amplitude over time. Only layer 3 has a noisy        |     |

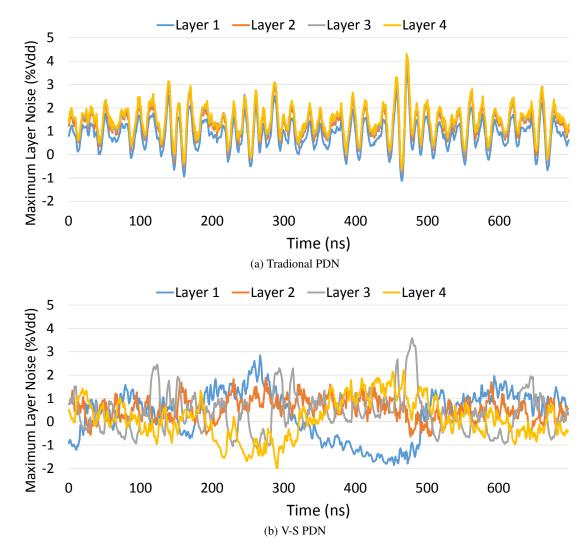

|     | workload                                                                               | 105 |

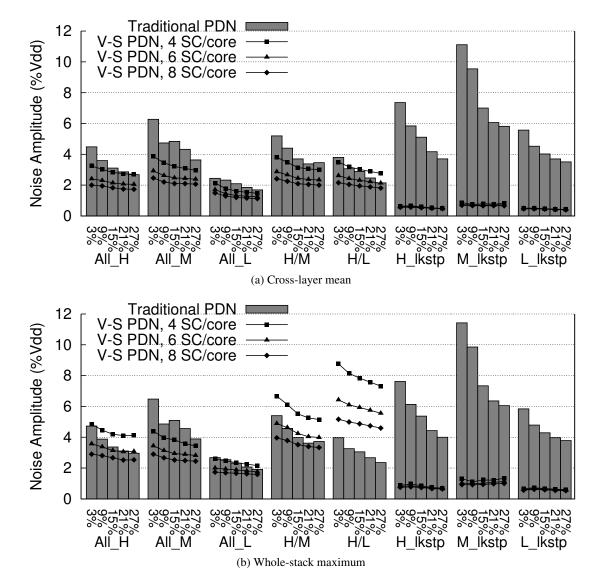

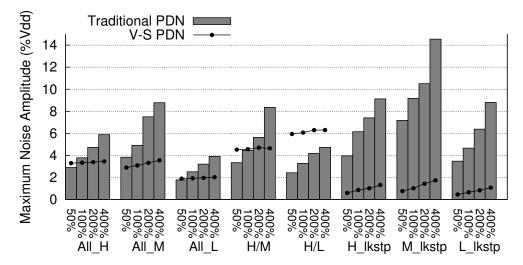

| 6.5 | A 4-layer 3D stack's voltage noise amplitude under different PDN configurations        |     |

|     | and workload conditions. The x-axis numbers within each data cluster represent the     |     |

|     | percentage of die area allocated for explicit decap. The size of each SC converter     |     |

|     | equals 3% of an ARM core                                                               | 107 |

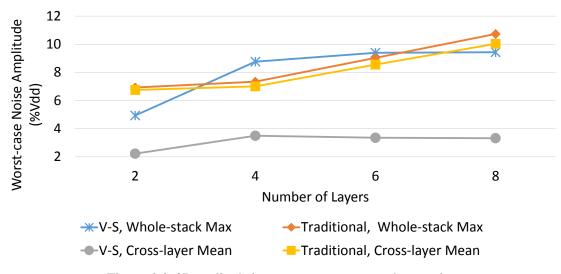

| 6.6 | 3D scaling's impact on worst-case voltage noise.                                       | 109 |

| 6.7 | Package impedance's impact on 3D-IC's whole-stack maximum noise. The x-axis            |     |

|     | of each data group shows the normalized package impedance                              | 110 |

# List of Tables

| 2.1 | Impact of on-chip modeling granularity. At 25:1, the number of rows and columns      |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | in the on-chip grid roughly matches the number of top-level metal wires in the PDN   |    |

|     | stack. Among 1914 total C4 pads, 1254 pads were allocated to P/G                     | 21 |

| 2.2 | Impact of modeling multiple metal layers.                                            | 22 |

| 2.3 | Static and transient validation results against IBM benchmark                        | 25 |

| 3.1 | Characteristics of Penryn-like Multicore Processors                                  | 33 |

| 3.2 | PDN Parameters                                                                       | 34 |

| 3.3 | Voltage Noise Scaling Trend, Ideal (all pads allocated to power/ground), in fluidan- |    |

|     | imate benchmark                                                                      | 37 |

| 3.4 | I/O pad breakdown for commercial processors.                                         | 37 |

| 3.5 | Package parameters extracted from Intel Xeon 5500 series processor [29]              | 39 |

| 3.6 | Supply voltage change due to metal layer occupancy. The majority of this chapter     |    |

|     | assumes a 33.3% layer occupancy. The evaluation platform is our 16core, 8MC          |    |

|     | processor.                                                                           | 40 |

| 3.7 | Dynamic Margin Adaptation and Scaling                                                | 43 |

| 3.8 | Impact of package impedance. We increase the serial portion of package impedance     |    |

|     | as an emulation to the consequence of more complicated I/O routing in chip package.  | 47 |

| 3.9 | C4 Pad EM Lifetime ScalingTrend                                                      | 49 |

| 4.1 | PDN Parameters used in this study.                                                   | 64 |

| 4.2 | Whole system's expected EM-failure-free time under different bump allocations.       | 67 |

|     |                                                                                      |    |

| 4.3 | Evaluation of EM-induced system MTTF under different transient noise margin           |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | settings. A 1k cycle stressmark is used to evaluate chip transient voltage noise. All |     |

|     | results are normalized to the EM-failure-free time of the baseline processor with     |     |

|     | 40% bumps assigned as power supply                                                    | 73  |

|     |                                                                                       |     |

| 5.1 | Major PDN modeling parameters                                                         | 85  |

| 5.2 | TSV configurations used in this study.                                                | 86  |

|     |                                                                                       |     |

| 6.1 | Primary PDN modeling parameters                                                       | 103 |

| 6.2 | Maximum voltage noise (%Vdd) per layer for different workloads on 3D-ICs with         |     |

|     | different PDN schemes. The "cross-layer mean" value averages all layers' maxi-        |     |

|     | mum noise amplitude                                                                   | 104 |

|     |                                                                                       |     |

## **Acronym List**

Definitions are collected here for easy reference. In general, the accepted definitions for terms are used, although some terms are used in a more restricted sense than their usual interpretation.

- **3D-IC** Three-dimensional integrated circuits.

- AC/DC Alternate current/Direct current.

- ALU Arithmetic logic unit.

- **C4 pad/bump** Controlled collapse chip connection. A method for interconnecting silicon dies to package.

- **CDF** Cumulative distribution function, which defines the probability distribution of a random parameter.

- CMOS Complementary metal-oxide-semiconductor.

- **CPM** Critical path monitor. A structure proposed by Lefurgy et al. [51] to detect the critical path's available timing margin during run-time.

- DRAM/SRAM Dynamic random-access memory/Static random-access memory.

- ECC error-correcting code.

- decap Decoupling capacitor.

- **DPLL** Digital phase-lock loop.

- DVFS Dynamic voltage and frequency scaling. A power management technique.

- **EM** Electromigration. Refers to the gradual mass transportation in metal conductors induced by momentum transfer from electrons to atoms.

- FBDIMM Fully buffered dual in-line memory module.

- **KoZ** Keep-out zone for TSVs, allocated to prevent the thermal stress generated by TSVs from impacting the electrical performance of the nearby transistors.

- **LU decomposition** A method to factor matrix as the product of a lower triangular matrix and an upper triangular matrix. 'LU' stands for 'lower upper'.

- I/O Input/Output.

- IR drop One type of voltage noise. Refers to the resistive drop across PDN wires.

- **ITRS** International Technology Roadmap for Semiconductors.

- **IVR** Integrated voltage regulators.

- LdI/dt One type of transient voltage noise. Caused by the PDN's inductance and the change of circuit current consumption.

- MC Memory controllers.

- MCS Monte Carlo Simulation.

- MIM capacitors Metal-insulator-metal capacitor.

- MTTF Median time to failure.

- **MTTFF** Median time to first failure. A metric we defined the show a group of conductors' expected lifetime until the first EM-induced failure.

- NoC Network on chip.

- PCB Printed circuit board.

- P/G Power/Ground.

#### Acronym List

- PDN Power delivery network.

- **RC/RLC** Resistor and capacitor/Resistor, inductor, and capacitor.

- RTL Register-transfer level. A design abstraction.

- SC converter Switched-capacitor converter. A type of integrated voltage regulator.

- **SPICE** Simulation Program with Integrated Circuit Emphasis. A general-purpose, open source analog electronic circuit simulator.

- **TDDB** time-dependent gate oxide breakdown. A long-term failure mechanism for integrated circuit.

- **TOF** Time of failure.

- **TSV** Through-silicon-vias. TSVs vertically connect all layers in 3D-ICs and provide both interlayer power delivery and I/O communication channels.

- **V-S** Voltage-stacking. A power delivery arrangement that electrically connects circuit blocks in series.

- VRM Voltage regulator modules.

# **Chapter 1**

### Introduction

#### 1.1 Overview

In the past decades, the scaling of CMOS technology allowed the semiconductor industry to successfully keep an exponential growth rate in device integration. However, even though Moore's Law continues to bring exponentially greater transistor densities, threshold and supply voltages no longer decrease fast enough to prevent exponential growth in on-chip power density [58]. Although the technology of three-dimensional integrated circuits (3D-IC) provides an alternative path toward continued growth of device integration, it further increases the aggregated density of both current consumption and heat generation. Consequently, it is becoming increasingly challenging to deliver sufficient current to switching transistors as well as to remove the massive heat generated by silicon chips. Among these physical constraints, thermal issues have been recognized as a critical barrier to utilize transistors effectively [81]. However, power *delivery* may be an even more serious constraint, especially as research and development efforts focus on aggressive cooling technologies such as liquid and microchannel cooling ( [78]), ameliorating if not eliminating the so called "temperature wall."

The power delivery network (PDN) is the electrical system that provides supply voltage to the underlying transistors within the silicon chip. A modern PDN usually consists of several levels of voltage regulator modules (VRM) and decoupling capacitors. Metal traces on both the printed circuit board (PCB) and in the chip package deliver supply current from off-board or off-chip VRMs

to controlled collapse chip connection (C4) pads, and on-chip metal layers further distribute current to the transistors [69].

Due to the power delivery network's intrinsic resistance, capacitance and inductance, the supply voltage will become noisy (drop or fluctuate) after traveling through the PDN. Since transistor delay is directly related to the voltage between its source and drain [74], any voltage variation outside the assumed design margin can cause a timing error, threatening program correctness. Furthermore, the PDN also suffers from long-term reliability issues like electromigration (EM). EM refers to gradual mass transport in metal conductors induced by momentum transfer from electrons to atoms. Under high current stress, EM can cause permanent damage to PDN wires, and degrade power delivery quality with increased voltage noise and voltage-noise-induced soft errors.

To guarantee power supply stability during silicon chip's entire lifetime, circuit designers and researchers have developed sophisticated methods to allocate and optimize a PDN's physical structure for both 2D and 3D chips (e.g. metal layer geometry [35, 36], decoupling capacitor distribution [67, 69], C4 pad location [99, 102, 106], and though-silicon-via, or TSV topology [23, 86]). These techniques help to reduce supply noise, and to date, noise can generally be handled with modest guardbands. However, power delivery difficulties arise and will get worse for several reasons. First, despite advances that have produced sophisticated on-chip PDN, the intrinsic resistance and inductance of the PDN circuit cannot be fully controlled with reasonable cost. This makes voltage fluctuation on the supply rails inevitable. Second, as current density increases with technology scaling and 3D scaling (i.e., stacking more layers of active silicon on top of each other), PDN reliability issues are exacerbated, creating higher demands for the already scarce physical resources like C4 pads and on-chip decaps. Finally, there is a contention between power delivery needs and processor computation needs. For example, C4 pads are the only connections between a silicon chip and the outside world thus both power supply and chip I/O signal links must utilize C4 pads exclusively. Under theses rising challenges, it becomes increasingly important to consider PDN design and optimization at early design stages, both to ensure an optimal design point selection in the complicated tradeoff space, and because a later redesign due to power delivery issues is costly.

This dissertation focuses on making cross-layer power delivery improvements in order to facil-

itate continued performance scaling. Our approach consists of the following major research tasks:

- Design, implement, and validate a pre-RTL PDN model that is capable of both modeling PDN's physical structure in detail and simulating whole-application power supply noise. Integrate this model with other architecture-level performance, power, and floorplan tools.

- 2. Analyse the impact of different C4 configurations on power delivery quality. Quantitatively evaluate the resulting performance impacts with different run-time noise mitigation techniques.

- Provide a statistical estimation for whole-chip's EM-induced lifetime that considers the failure possibility of all pads and the sequence of pad failures. Analyse the noise impact of multiple pad failures and explore the feasibility of tolerating failures with increased noise margin.