# Accelerating Sampled Microarchitecture Simulation:

### Rapid Warm Up for Simulated Hardware State

A Dissertation

Presented to

the Faculty of the School of Engineering and

Applied Science at the University of Virginia

in Partial Fulfillment for the Degree

Doctor of Philosophy

Computer Science

John W. Haskins, Jr.

Department of Computer Science

University of Virginia

Charlottesville, VA 22904

### Approvals

| degree of Doctor of Philosophy Computer Science  John W. Haskins, Jr. Approved:  Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan Accepted by the School of Engineering and Applied Science: | This dissertation is submitted in partial fulfillment of the requirements for the |                    |                                  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------|----------------------------------|--|--|--|

| John W. Haskins, Jr.  Approved:  Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan                                                                                                            | degree of                                                                         |                    |                                  |  |  |  |

| John W. Haskins, Jr.  Approved:  Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan                                                                                                            | Doctor of Philosophy                                                              |                    |                                  |  |  |  |

| Approved:  Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan                                                                                                                                  | Computer Science                                                                  |                    |                                  |  |  |  |

| Approved:  Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan                                                                                                                                  |                                                                                   |                    |                                  |  |  |  |

| Approved:  Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan                                                                                                                                  |                                                                                   |                    |                                  |  |  |  |

| Kevin Skadron (Advisor)  John C. Knight (Chair)  John A. Stankovic  Marty A. Humphrey  Mircea R. Stan                                                                                                                                             |                                                                                   | John W.            | . Haskins, Jr.                   |  |  |  |

| John A. Stankovic Marty A. Humphrey  Mircea R. Stan                                                                                                                                                                                               |                                                                                   | Ap                 | proved:                          |  |  |  |

| John A. Stankovic Marty A. Humphrey  Mircea R. Stan                                                                                                                                                                                               |                                                                                   |                    |                                  |  |  |  |

| John A. Stankovic Marty A. Humphrey  Mircea R. Stan                                                                                                                                                                                               |                                                                                   |                    |                                  |  |  |  |

| Mircea R. Stan                                                                                                                                                                                                                                    | Kevin Skadron (Advisor)  John C. Knight (Chair)                                   |                    |                                  |  |  |  |

| Mircea R. Stan                                                                                                                                                                                                                                    |                                                                                   |                    |                                  |  |  |  |

| Mircea R. Stan                                                                                                                                                                                                                                    | Iohn A Sta                                                                        | ankovic            | Marty A Humphrey                 |  |  |  |

|                                                                                                                                                                                                                                                   | JUIII 11. Due                                                                     | #IIKO VIC          | wardy 11. Hampiney               |  |  |  |

|                                                                                                                                                                                                                                                   |                                                                                   |                    |                                  |  |  |  |

| Accepted by the School of Engineering and Applied Science:                                                                                                                                                                                        | Mircea R.                                                                         | Stan               |                                  |  |  |  |

|                                                                                                                                                                                                                                                   | $egin{array}{c} 	ext{Accepted} \end{array}$                                       | by the School of E | Engineering and Applied Science: |  |  |  |

|                                                                                                                                                                                                                                                   | •                                                                                 | U                  |                                  |  |  |  |

|                                                                                                                                                                                                                                                   |                                                                                   |                    |                                  |  |  |  |

| Richard W. Miksad (Dean)                                                                                                                                                                                                                          |                                                                                   | Richard W.         | Miksad (Dean)                    |  |  |  |

May 2003

#### Abstract

This dissertation introduces techniques for quantitatively reasoning about cache capacity and accelerating sampled microarchitecture simulation. By reducing the time spent warming up the simulated hardware state, Minimal Subset Evaluation warm up (MSEwarmup) and its successor, Memory Reference Reuse Latency (MRRL) are able to substantially reduce overall simulation running times. Warm up is commonly used prior to modeling cycle-accurate simulation sample clusters to prevent cold-start bias from compromising the accuracy of simulated state in large structures like caches and branch predictor, and thereby preserve simulation accuracy. Unfortunately, warm up can be very time consuming, often representing 50% or more of total simulation time. Previous simulation strategies have warmed up the entire pre-cluster interval (i.e., modeled all cache and branch predictor interactions prior to each actual sample cluster) to obtain accurate hardware state; this is the full-warmup approach. While accurate, this time-consuming alternative may be prohibitive for large parameter-space searches. Other techniques have chosen a short but ad-hoc warm up length that reduces simulation time but may sacrifice accuracy.

Minimal Subset Evaluation (MSE) is a novel framework for quantitatively assessing the minimally sufficient number of unique memory references that must be handled within the cache in order to touch a certain proportion of the cache blocks with some user-chosen

probability. (The aforementioned MSEwarmup technique adapts MSE to forge a solution to the problem of accurately warming up L1 cache state.) This dissertation describes the mathematical underpinnings of MSE and demonstrates MSEwarmup's use for quickly and accurately warming up both single-large-cluster and multiple-cluster simulation styles for small L1 caches. My experiments show that MSEwarmup yields errors of less than 1% in IPC measurements with cycle-accurate simulation.

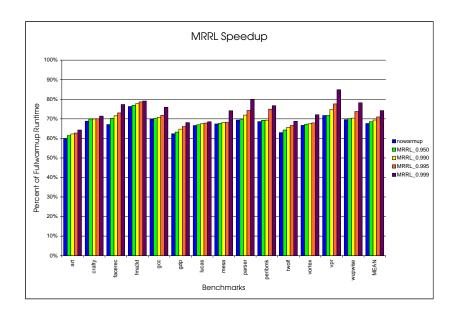

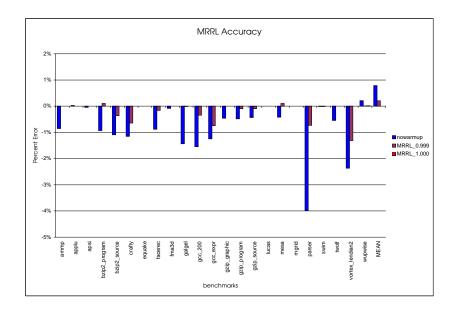

MRRL builds upon MSE and MSEwarmup, but rather than using statistical methods, MRRL analyzes the lag time between consecutive references to each unique memory address in each pre-cluster-cluster benchmark partition. With this data MRRL is able to choose a point during the pre-cluster instructions to engage cache warm up (at all levels in the hierarchy, regardless of block size, associativity, or separation) and branch predictor warm up. Because of MRRL's applicability to all levels of the cache hierarchy regardless of organization as well as dynamic branch prediction, it supersedes MSEwarmup as a method for achieving accurate state quickly and accurately. MRRL yields an average error of less than 1% in IPC measurements relative to fullwarmup simulation, and reduces warm up by an average of 90% of the maximum potential speed up.

Starting cache and branch predictor modeling late in the pre-cluster instruction stream allows both MSEwarmup and MRRL to capitalize upon the observation that only the branch predictor and cache interactions that occur nearest to a cluster are germane to simulation activity during the cluster itself.

# Chapter 1

# Introduction, Background and

### Motivation

This dissertation introduces Minimal Subset Evaluation (MSE) [17, 20] and Memory Reference Reuse Latency (MRRL) [18, 19]. MSE is a rigorous analytical framework for assessing cache occupancy based entirely upon the cache dimensions and the count of unique reference addresses handled within the cache. By calculating the number of unique references necessary to touch a certain proportion of L1 cache blocks, MSE can be used to accelerate sampled microarchitecture simulation. Rather than making a probabilistic determination of occupancy, MRRL attempts to measure the "amount of temporal locality." MRRL uses this information to accelerate sampled simulation by accelerating warm up in all levels of the cache hierarchy as well as the branch predictor.

Developing actual hardware is profoundly expensive. This practical consideration

makes experimentation with new ideas in hardware prohibitive. Through simulation on the other hand, ideas may be developed, tested, discarded or refined repeatedly with infinitely more ease, speed, and at a modicum of the cost of such experimentation with hardware prototypes. It is precisely this vastly superior flexibility offered by simulation that makes software simulators a fundamental tool for computer architecture research. Simulation is especially beneficial for exploring radically new ideas that may not be feasible to prototype [43, 44].

Unfortunately, the flexibility of software simulation trades away speed. Detailed software simulation is orders of magnitude slower than native hardware execution. Thus, rather than simulating the full execution of a program in detail, researchers typically estimate the performance of a simulated microarchitecture by simulating only a sample of program *clusters* (contiguous segments of the dynamic instruction stream) in detail. By reducing the amount of time spent warming up simulated processor state, *MSEwarmup* and MRRL achieve further acceleration, thereby enhancing the value of software simulation as a tool for microarchitecture research.

This chapter introduces software simulation, strategies for making it more tractable, performance evaluation, declares my research thesis, and concludes with an overview of the research presented in this dissertation.

#### 1.1 Software Simulation

Relative to native execution, simulation in software is very slow, introducing slowdown factors of hundreds or thousands even on today's fastest microprocessors. The amount

CHAPTER 1. INTRODUCTION, BACKGROUND AND MOTIVATION

of slowdown is inversely proportional to the level of detail captured by the simulation. Simple instruction-level simulation, for example, executes much more rapidly than highly detailed circuit-level simulation. This is because the ratio of native (i.e., host) instructions to simulated instructions increases along with level of detail. In other words, simulation imposes a trade-off between speed and detail.

In software simulation, execution is emulated in a fetch–decode–execute loop: one by one, instructions are read from the binary, their operands acquired, and their prescribed operation simulated. However, whereas the elements of this loop are handled automatically in native hardware, many hundreds or thousands of native instructions are required to emulate these elements in software. In the simplest case, functional simulators such as SPIM [34] and the sim-safe component of the SimpleScalar [2, 4] software suite, model only the architected state of the microprocessor. For load–store architectures such as the MIPS [46] and the Alpha [52] (modeled by SPIM and sim-safe, respectively), this state consists of the contents of the register file and main memory. By tracking only the bare-minimum state necessary to execute a binary, functional simulation is one of the fastest software simulation methods. Functional simulators are excellent tools for compiler research, allowing developers to construct experimental compiler technology for non-native or unrealized hardware.

For more detailed simulation, it is necessary to maintain state beyond the register file and main memory. Experiments with cache or translation look-aside buffer (TLB) organization, for instance, require tracking cache and TLB state (i.e., sim-cache [2]). Maintaining this state adds several hundreds more native instructions per simulated

instruction beyond the aforementioned fetch-decode-execute loop for implementing lookup, detecting and rerouting misses, choosing a victim and performing evictions. Tracking branch predictor state (i.e., sim-bpred [2]) introduces similar complexities and further augments the number of native instructions required per simulated instruction. An example of a simulator that models cache and branch predictor state in addition to architected state is the Mipsy component of the SimOS software suite [23].

Detailed studies that attempt to estimate the overall performance of an experimental microprocessor require cycle-accurate simulation. Cycle-accurate simulation models the step-by-step flow of instructions through a synchronous microprocessor pipeline. In synchronous microprocessors, instruction flow occurs discretely, synchronized by the pulse of an on-chip clock distribution network. Each pulse of the clock occurs at a constant rate (e.g., 3.06GHz = 3,060 cycles/second) and is counted as one cycle. Hence for synchronous microprocessors, a key performance metric—instruction throughput—is measured in units of instructions per cycle (IPC) (i.e., average number of committed instructions per on-chip clock pulse). (Other, less desirable metrics will be discussed in 1.3, and a case will be made for instruction throughput.) The research described in this dissertation studies the simulation of synchronous microprocessors.

Cycle-accurate simulation is terribly slow. With cycle-accurate simulations, running many of the SPEC95 benchmarks to completion with reference inputs takes days or weeks [54], and running some of the SPEC 2000 benchmarks takes many weeks even with today's fastest systems [29]. Because cycle-accurate simulation models the movement of individual instructions through the pipeline, the state of many more

CHAPTER 1. INTRODUCTION, BACKGROUND AND MOTIVATION

on-chip structures beyond the register file, main memory, cache, TLB and branch predictor must be maintained. In a wide-issue out-of-order pipeline, these structures include the instruction reorder buffer, issue logic, result forwarding network, register renaming hardware, functional units, store queue, and commit logic, to name just a few.

The apex of simulation detail is to model the flow of signals along wires to interconnected logic elements that compose on-chip structures and pipeline elements. For this level of detail, VHDL [45, 73] (Very High-speed Integrated Circuit Hardware Design Language) is the language of choice for coding the actual hardware description; and TyVIS [63] is an example of a software package that can simulate a microprocessor design coded in VHDL. Its cost is prohibitive for microarchitecture research; hence it is used for circuit-level work. The research discussed in this dissertation does not perform simulation in such detail; it is mentioned here for completeness.

To summarize, a microprocessor can be simulated at varying levels of detail, each more suitable to specific types of research. Functional simulation does not model any of the details of a specific processor organization beyond the architected state. This makes instruction-level simulators well-suited, for instance, to compiler research, enabling experimentation with non-native or even unrealized instruction sets. Microarchitectural simulators model the inner workings of all or part of an actual processor, including the pipeline, cache hierarchy, and branch predictor at the component level. These simulators are appropriate for estimating the performance of actual hardware components (individually and in collaboration), and are suitable for architecture and

pipeline organization research. Finally, circuit-level simulators model the low-level implementation details of hardware components. Used in concert with the VHDL specification language, these simulators are useful for the development, analysis, and verification of architectural components.

#### 1.2 Simulation Strategies: Sampling versus Reduced Inputs

To combat cycle-accurate simulation's long running times, most simulation strategies either take samples of multiple short *clusters* of contiguous groups of instructions from the dynamic instruction stream, "fast-forwarding" between clusters [8, 51], or else fast-forward to a single, large simulation cluster of 50–100 million instructions [50, 54]. Both techniques save time by executing in cycle-accurate detail only those instructions contained in the sample clusters. In contrast, during the pre-cluster phase (*i.e.*, during the emulation of instructions prior to each cluster) cycle-by-cycle modeling of individual instructions through the pipeline is not performed. The result is a much faster-running simulation.

Another approach to reduce simulation times is to use reduced inputs [20, 29, 30]: a shrunken input set based upon a benchmark's reference inputs, intended to execute in less time while exhibiting behavior similar to the full reference inputs. Reduced inputs however, raise the question of the reduced input's accuracy. In joint research with the KleinOsowski and Lilja at the University of Minnesota [20], we compare the accuracy of simulations with their MinneSPEC reduced inputs against sampled simulations using the original reference inputs for several SPEC CPU2000 benchmarks.

| benchmark_input | $\mathrm{IPC}_{true}$ | $\mathrm{IPC}_{sampling}$ | $\mathrm{IPC}_{reducedinput}$ |

|-----------------|-----------------------|---------------------------|-------------------------------|

| art_110         | 0.5984                | -0.45%                    | -9.09%                        |

| art_470         | 0.5974                | 0.64%                     | -8.94%                        |

| gzip_graphic    | 1.3645                | -1.69%                    | 3.79%                         |

| gzip_log        | 1.4620                | -1.41%                    | 7.91%                         |

| gzip_program    | 1.3884                | 0.44%                     | -1.52%                        |

| $gzip\_random$  | 1.3187                | 1.39%                     | 0.18%                         |

| gzip_source     | 1.3609                | 0.71%                     | 1.06%                         |

| vortex_lendian1 | 1.0918                | 0.24%                     | -14.81%                       |

| vortex_lendian2 | 1.0573                | -0.52%                    | -12.58%                       |

| vortex_lendian3 | 1.0890                | -0.59%                    | -14.62%                       |

| vpr_place       | 0.8460                | 0.50%                     | 11.42%                        |

| vpr_route       | 1.0232                | 1.73%                     | 39.28%                        |

| MEAN            |                       | 0.86%                     | 10.43%                        |

Table 1.1: Accuracy: Sampling versus reduced inputs [20]. Percent-error in IPC  $(100\% \cdot \frac{(IPC-IPC_{true})}{IPC_{true}})$  measures the deviation from end-to-end cycle-accurate simulation (IPC<sub>true</sub>). MEAN calculated from the absolute values of error measurements.

As Table 1.1 shows, sampling is more accurate, generating IPC values that are closer than reduced inputs to those obtained by complete, end-to-end cycle-accurate runs of the benchmarks on the reference inputs (IPC $_{true}$ ). The strategy of 50 equidistantly spaced samples of 10 million instructions apiece yielded a maximum error of 1.73% for  $vpr\_route$  and an average error of 0.86%. The reduced inputs, however, did not consistently yield such high fidelity, with a maximum error of 39.28% for  $vpr\_route$  and an average error of 10.43%. Table 1.2 shows that both reduced inputs and sampling significantly lessen simulation running time, with neither running for more than 4% of the time required for end-to-end cycle-accurate simulation. In terms of accuracy however, sampling is the clear victor; hence, my research focuses on this approach.

| benchmark_input | $\mathrm{t}_{true}$     | $\% t_{sampling}$ | $\% \mathrm{t}_{reducedinput}$ |

|-----------------|-------------------------|-------------------|--------------------------------|

| art_110         | $756507 \mathrm{sec}.$  | 1.36%             | 3.06%                          |

| art_470         | 801815  sec.            | 1.40%             | 2.89%                          |

| gzip_graphic    | $829097~{\rm sec.}$     | 0.49%             | 1.73%                          |

| gzip_log        | $380475~{ m sec.}$      | 1.24%             | 1.62%                          |

| $gzip\_program$ | 953154 sec.             | 1.36%             | 1.76%                          |

| $gzip\_random$  | $733661  \mathrm{sec.}$ | 1.17%             | 1.77%                          |

| gzip_source     | $673621~{ m sec.}$      | 1.15%             | 1.95%                          |

| vortex_lendian1 | $890519  \mathrm{sec.}$ | 3.04%             | 1.49%                          |

| vortex_lendian2 | $971445~{ m sec}.$      | 3.18%             | 1.37%                          |

| vortex_lendian3 | 954585 sec.             | 3.15%             | 1.39%                          |

| vpr_place       | $1050041~{\rm sec}.$    | 1.47%             | 1.53%                          |

| vpr_route       | $997469~{\rm sec.}$     | 1.18%             | 1.04%                          |

| MEAN            |                         | 1.68%             | 1.80%                          |

Table 1.2: Running time: Sampling versus reduced inputs [20]. Percentage of running time  $(100\% \cdot \frac{t}{t_{true}})$  measures the fraction of end-to-end cycle-accurate simulation running time  $(t_{true})$ .

Table 1.3 documents further experiments, where I compared the running time of end-to-end cycle-accurate simulation to end-to-end cold (i.e., modeling register file and main memory updates), and end-to-end warm (i.e., modeling register file, main memory and cache interactions), in addition to the running times of two sampling disciplines: 50 equidistantly-spaced at 1 million instructions apiece and 10 equidistantly-spaced at 5 million instructions apiece. (These experiments were run on different, faster hardware than those from Tables 1.1 and 1.2; hence, the shorter running times for  $t_{true}$ .) End-to-end cold simulation is unwaveringly the fastest, in all cases executing in less than 11% the time required for end-to-end cycle-accurate simulation. End-to-end warm performs well also, completing in less than 20% the time required

| benchmark_input | $\mathrm{t}_{true}$ | %t <sub>50×1</sub> | %t <sub>10×5</sub> | $\% \mathbf{t}_{warm}$ | $\%\mathrm{t}_{cold}$ |

|-----------------|---------------------|--------------------|--------------------|------------------------|-----------------------|

| art_110         | $153937~{\rm sec.}$ | 12.01%             | 11.88%             | 15.84%                 | 8.93%                 |

| art_470         | $169606~{\rm sec.}$ | 11.99%             | 11.89%             | 15.96%                 | 8.93%                 |

| gzip_graphic    | 192591 sec.         | 12.35%             | 12.33%             | 18.10%                 | 9.91%                 |

| gzip_log        | 72822 sec.          | 13.48%             | 13.78%             | 19.81%                 | 10.70%                |

| $gzip\_program$ | $252959~{\rm sec.}$ | 13.10%             | 13.11%             | 19.07%                 | 10.27%                |

| $gzip\_random$  | $152678~{\rm sec.}$ | 12.30%             | 12.29%             | 17.91%                 | 9.76%                 |

| gzip_source     | $138742~{\rm sec.}$ | 13.14%             | 13.14%             | 19.15%                 | 10.33%                |

| vortex_lendian1 | $401396~{\rm sec.}$ | 13.13%             | 13.11%             | 19.21%                 | 10.56%                |

| vortex_lendian2 | $460819~{\rm sec.}$ | 13.10%             | 14.37%             | 19.09%                 | 10.47%                |

| vortex_lendian3 | 448293 sec.         | 13.60%             | 13.53%             | 19.19%                 | 10.53%                |

| vpr_place       | $274529~{\rm sec.}$ | 11.94%             | 11.85%             | 17.09%                 | 9.51%                 |

| vpr_route       | $232330~{\rm sec.}$ | 11.17%             | 11.22%             | 16.84%                 | 9.34%                 |

| MEAN            |                     | 12.61%             | 12.71%             | 18.10%                 | 9.94%                 |

Table 1.3: Running time:  $50 \times 1$  and  $10 \times 5$  sampling versus end-to-end warm versus end-to-end cold. Percentage of running time  $(100\% \cdot \frac{t}{t_{true}})$  measures the fraction of end-to-end cycle-accurate simulation running time  $(t_{true})$ .

by end-to-end cycle-accurate simulation. Notice however, that experiments from the two sampling disciplines complete in even less time than end-to-end warm simulation. These experiments implement MSEwarmup, one of the simulation acceleration techniques discussed later in this dissertation.

The accuracy of simulation within each cycle-accurate sample depends on avoiding cold-start bias. Cold-start bias is the name given the phenomenon whereby sampled data tend to be skewed when environmental state is inaccurate or unrepresentative at the beginning of a sample cluster [8]. In a microprocessor, performance is deeply affected by cache and branch predictor performance [21]: if the requested data are in the cache(s) and the branch predictor makes accurate predictions, then the processor

| benchmark (suite)                   | fast-forward interval |

|-------------------------------------|-----------------------|

| bzip2 (SPEC CPU2000)                | 1,733                 |

| hydro (SPEC CPU95)                  | 36                    |

| tomcat (SPEC CPU95)                 | 144                   |

| vortex (SPEC CPU2000)               | 330                   |

| ${ m vpr}~({ m SPEC}~{ m CPU2000})$ | 746                   |

| wave (SPEC CPU95)                   | 1,036                 |

Table 1.4: Sample of pre-cluster intervals (in 100s of millions of instructions) used for simulations reported by Sherwood *et al.* [50].

will spend fewer clock cycles executing a program. Hence, to defeat cold-start bias the processor "environment" (i.e., the state contained in the cache hierarchy and the branch predictor) needs to be as close as possible to the state that would have resulted from executing the entire pre-cluster phase in cycle-accurate detail. In other words, cold-start bias can be defeated by allowing a period of warm up prior to each cycle-accurate cluster.

One warm up technique for achieving accurate pre-cluster processor environment involves modeling all pre-cluster cache and branch predictor interactions, in addition to the architected state. I call this technique fullwarmup because it defeats cold-start bias by "warming up" the simulated cache hierarchy and branch predictor state throughout the pre-cluster instructions. The accuracy of the cache and branch predictor state under fullwarmup is unimpeachable; just as would have occurred using cycle-accurate simulation during the pre-cluster phase, all cache and branch predictor interactions are modeled. Thus, for the remainder of this research fullwarmup is used as the baseline reference for all accuracy measurements.

Unfortunately, while much faster than cycle-accurate simulation, fullwarmup is still expensive. As described before, modeling all cache and branch predictor interactions adds many more hundreds or thousands of native instructions beyond those required to model only the architected state. This causes the simulator to run longer and makes fullwarmup prohibitive, especially for large state-space searches requiring multiple simulations with varying parameters. fullwarmup's expense is also a problem when the cycle-accurate clusters occur deep within a benchmark's dynamic instruction stream. To elucidate the latter point, consider Table 1.4 which shows the pre-cluster fast-forward distances prescribed by Sherwood et al. [50]. For each of these benchmarks, the target sample cluster begins many hundreds of millions of instructions from the start of execution.

#### 1.3 Processor Performance Evaluation

Before describing the tools and techniques commonly used to evaluate microprocessor performance, it is essential to establish a metric by which performance can be usefully measured. As mentioned in 1.1, the metric of choice for this research is instruction throughput, measured in units of completed instructions per clock cycle. Two less desirable metrics [21, 60] are millions of instructions per second (MIPS) and billions of floating-point operations per second (GFLOPS).

The former is calculated as the quotient of dynamic instruction count divided by wall-clock running time (in microseconds) of the benchmark. While straight-forward to calculate, MIPS is not meaningful because dynamic instruction count can vary widely between different instruction set architectures. Say, for instance, that some program's source is compiled for two unique CPUs from vendor A and vendor B into binaries,  $bin_A$  and  $bin_B$ . If vendor A's CPU uses a minimalist instruction set that emphasizes simplicity whereas vendor B's CPU uses a richer instruction set, featuring operations that atomically perform complex manipulations,  $bin_A$  will likely have a larger footprint than  $bin_B$ . Finally, suppose that  $bin_A$  and  $bin_B$  on the same input, execute in the same amount of time; while neither vendors' CPU finishes sooner than the other, vendor A's CPU—using MIPS—would be branded the clear victor because it executed more instructions per unit of time on average, than vendor B's CPU. Although contrived, this example vividly illustrates the deceptive nature of the MIPS performance metric [21].

GFLOPS is a deceptive metric for similar reasons. Programs do not all share the same proportion of floating-point operations and therefore cannot be meaning-fully compared. Software that calculates the stresses placed upon cables and anchor blocks in suspension bridges, for instance, will likely spend the overwhelming majority of its time performing numerous floating-point calculations; software that minimizes Boolean logic functions, however, will likely perform almost none. Hence, the bridge-modeling software will score much higher than the logic minimizer in GFLOPS units. Furthermore, back to the issue of instruction set architectures, the same source code compiled for two different CPUs may still yield two binaries with substantial differences in the count of floating-point operations if the two instruction sets do not implement the same floating-point operations. Those operations not implemented

as native hardware instructions may be doable as a combination of simpler floating-point operations, emulated in software, or passed to an off-chip coprocessor. In either case, it is difficult to develop a compelling argument that the two binary's GFLOPS performance ratings are comparable.

For these reasons, MIPS and GFLOPS have been largely abandoned for scientific, scholarly discussion of microprocessor performance. In the context of software simulation however, still more complications arise from their use. Specifically, these metrics calculate a rate per unit time. While it is possible to develop a framework for mapping cycle-accurate simulation events to equivalent real-time durations, this process is lengthy and the results contingent on a plethora of unimportant technological peculiarities (e.g., capacitance, feature size). Rather, software simulation requires a higher-level, more abstract notion of performance; instruction throughput meets this requirement nicely.

The average number of completed instructions per clock cycle measures performance by describing how fully a pipeline utilizes its maximum instruction retiring capacity. A superscalar pipeline design capable of retiring four instructions per cycle, for instance, has a theoretical maximum IPC of 4. By corollary, the minimum IPC of 0 indicates a CPU making no progress whatever. Instruction throughput is a very complete performance metric, well suited to software simulation. Particularly attractive is its independence from real-time considerations and that measurements of actual performance are tightly coupled to the theoretical maximum; the latter gives valuable context to all performance measurements, as the ratio of the measured IPC

and the theoretical maximum IPC gives the pipeline's operational efficiency.

Furthermore, for a given clock speed, a benchmark's true running time is easily calculated by dividing the number of instructions executed by the product of instruction throughput and clock frequency, *i.e.*,

$$t = \frac{\#instructions}{(cycles/second)(IPC)}$$

The second part of processor performance evaluation is choosing the binary or set of binaries that will be executed to gather the performance measurements. Hennessy and Patterson [21] describe several categories of these benchmark binaries, toy programs, kernels, synthetic programs, and real programs. Toy programs are very small executables that implement simple algorithms such as sorting algorithms and binary search. Hennessy and Patterson immediately dismisses toy programs, calling them most appropriate as programming assignments for beginning programmers. Their tiny size and simplistic nature prevent them from posing any serious challenge worthy of performance measurements.

Kernels and synthetic programs are held in slightly higher regard than toy programs. Kernels are small, key components of actual programs. The Lawrence Livermore Loops [38] were once widely used for processor performance evaluation. Dhrystone [71] and Whetstone [10] on the other hand, are two examples of synthetic benchmarks. Synthetic benchmarks are artificial programs whose instruction mix is intended to match the instruction mix profile characteristics (e.g., opcode frequency, basic-block size) of a large collection of real programs. Kernels are derived from

actual programs, but may fail to exhibit the same characteristics of their parent program. Synthetic benchmarks are only very loosely related to any real software; thus, their performance appraisal cannot be expected to yield useful measurements that are representative of real programs.

By far, the most respected class of benchmark programs are real programs. The reasoning behind this is simple. Most users will not spend money on computer systems merely to run toy programs, or synthetic programs, or to extract the innermost loops of real software and only execute them. Most users will want to run real programs; therefore, the most reliable source of truly representative performance measurements will come from real programs. The range of real programs is quite large and very diverse, ranging from compute-bound software such as ray tracers to I/O-bound word processors. The general consensus among computer architects is to make performance judgments from measurements made on a wide assortment of real benchmark programs or benchmark suites. These benchmark suites have the advantage of masking the weaknesses of any one of its members by the inclusion of the others [21].

One very popular benchmark suite for evaluating CPU performance on computeintensive (integer and floating-point) workloads is SPEC CPU [57, 58], from the Standard Performance Evaluation Corporation. The most recent edition, SPEC CPU2000, includes programs for compiling, combinatorial optimization, FPGA circuit layout and routing, chess playing, data compression, quantum chromodynamics modeling, shallow water simulation, image recognition, primality testing, computational chemistry, pollutant distribution, and several others. Earlier editions of the SPEC CPU CHAPTER 1. INTRODUCTION, BACKGROUND AND MOTIVATION

benchmark suite were introduced in 1995, 1992, and inarguably in 1989 in response to the growing need for a realistic, uniform, performance evaluation standard.

As Hennessy and Patterson [21] describes, a particular set of benchmarks will likely not remain valid gauges of performance indefinitely. In their quest to address precisely this caveat of all benchmark suites, SPEC released these incarnations of SPEC CPU in an attempt to address several specific issues [9] including: running time, application size, and application type. The dynamic instruction count of several SPEC CPU95 benchmarks, while impressive at their introduction, were very tiny on more recent hardware, sometimes running for less than a minute. Such brief executions provided no challenge for contemporary microprocessor technology. In the five years since SPEC CPU 95, there had also been advances in software sophistication and complexity in addition to the advances made in hardware. This made it necessary to include programs with larger resource requirements as well as programs from new application areas.

As in earlier generations, SPEC CPU2000 programs are loosely grouped into two categories: integer and floating-point. Together, these two categories establish the aforementioned balance afforded by using a collection of multiple programs in the benchmark suite. The floating-point intensive programs keep balance by correcting the integer programs' inability to stress a pipeline's floating-point functional units. Secondly, since there are numerous special-purpose compiler optimizations geared toward floating-point computations, the integer programs maintain balance by preventing the performance evaluation from being unduly skewed in favor of these very

| benchmark          | $\mathrm{t}_{user}$ | $\mathbf{t}_{system}$ | %-system |

|--------------------|---------------------|-----------------------|----------|

| art_110            | 246.700             | 0.188                 | 0.076%   |

| crafty             | 276.432             | 0.188                 | 0.068%   |

| equake             | 730.058             | 0.609                 | 0.083%   |

| facerec            | 482.358             | 0.693                 | 0.143%   |

| mgrid              | 665.514             | 1.871                 | 0.280%   |

| twolf              | 886.918             | 0.609                 | 0.069%   |

| $vortex\_lendian2$ | 208.693             | 0.462                 | 0.221%   |

| vpr_route          | 407.248             | 0.393                 | 0.096%   |

Table 1.5: Code execution time (in seconds) for several SPEC CPU2000 benchmarks executed on an Alpha 21264 running OSF/1. System code accounts for less than 0.3% of the overall execution time in all cases; therefore, system code is often ignored in software microprocessor simulation and performance evaluation.

specialized optimizations. Because of the good mix of real programs that stress floating-point and integer performance—both of which rely heavily on accurate branch prediction and good cache hit rates—I chose SPEC CPU95 and SPEC CPU2000 for my experiments.

The third part of microprocessor performance evaluation is operating system performance, but this piece of the performance puzzle is often ignored. While operating system code efficiency does impact the execution time of programs running on real hardware, for compute-intensive code this impact is usually insignificant. Table 1.5 shows the wall-clock running time of several SPEC CPU2000 benchmarks executed on an Alpha 21264 running OSF/1, for the user code ( $t_{user}$ ), and the system code ( $t_{system}$ ) as reported by the *time* UNIX utility, as well as the percentage of system code from the overall execution time (%-system).

The benchmark with the largest system time component is mgrid, but of the more

than 11 minutes that this program executed, the 1.871 seconds of system time account for only 0.28% of the overall running time. This is the chief reason that the operating system contribution to the pipeline performance evaluation is largely ignored in microprocessor simulations; such a tiny contribution is safely ignored. (This is analogous to approximating the binomial distribution by the Poisson or Gaussian distribution.) It is difficult to justify the overhead of porting an operating system kernel, memory management infrastructure, and device drivers for such a small amount of additional precision. Even if operating system performance were significant however, meaningful comparative analysis would require that the operating system performance among various studies be nearly identical. Furthermore, inclusion of system-level performance would make the performance analysis more "impure" by making it subject to the influence of an additional source of noncomplicity outside the agreed upon suite of benchmark programs.

# 1.4 The Importance of Adequate Warm Up to Measurement Accuracy

The role of error and uncertainty in sampled microprocessor simulation is critical to establishing the significance of this research. Sampling produces error because only a subset of a population is measured rather than the entire population. As Conte at el. [8] show, however, random cluster sampling is a useful tool for microprocessor simulation, that is amenable to statistical methods which allow one to rigorously gauge the amount of error and to quantitatively express confidence in the result,

based on the assumption that all members of the population had equal probability of being selected for inclusion in the sample. Specifically, random cluster sampling establishes a confidence interval  $[IPC-\alpha,IPC+\alpha]$  within which the true IPC can be assumed to exist with X% certainty (where  $\alpha$  is a function of X).

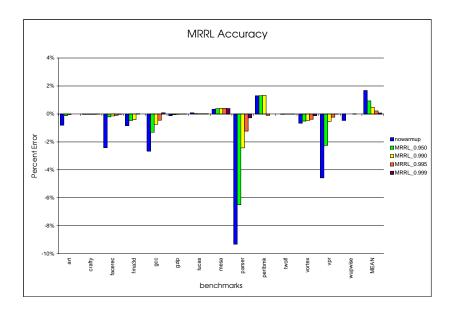

For a well-chosen sample, a benchmark's true IPC—as would have resulted if the benchmark were simulated to completion in cycle-accurate detail—will fall inside the confidence interval computed by fullwarmup simulation. This is because modeling all cache and branch predictor interactions renders fullwarmup impervious to cold-start bias. As will be shown in Chapter 5, MRRL does well at mimicking the behavior of fullwarmup, deviating by a statistically insignificant amount. On the other hand, for the exact same sample, an ineffective warm up technique can yield an estimated IPC that significantly deviates from the fullwarmup estimation, and whose confidence interval does not contain the benchmark's true IPC.

#### 1.5 Research Preview

Checkpointing simulation state at the beginning of each sample cluster is one solution for accelerating sampled simulation while conquering cold-start bias; fullwarmup simulation would incur a one-time cost for each benchmark—input pair and the checkpoint would be loaded at simulator initialization. Unfortunately, separate checkpoints would be required for each desired combination of cache and branch predictor configurations, and for each set of simulation sample clusters for each benchmark program.

$<sup>^{1}</sup>$ I prove claims of statistically (in)significant deviation from *fullwarmup* by application of the matched-pairs t-test to actual benchmark simulations.

To avoid this unattractive alternative, my techniques make use of information about the branch-, instruction- and data reference streams. This will be discussed at length in Chapter 3 and Chapter 4.

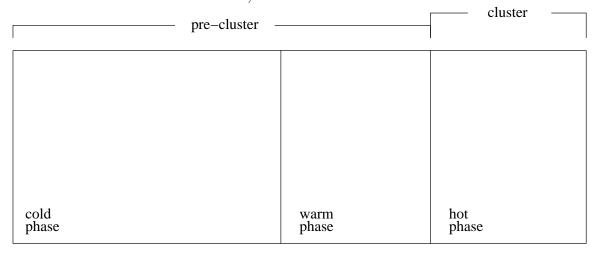

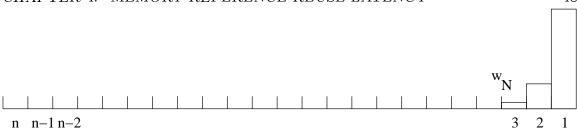

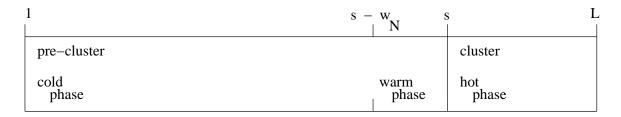

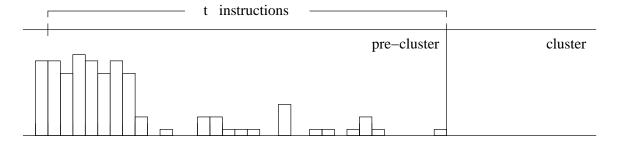

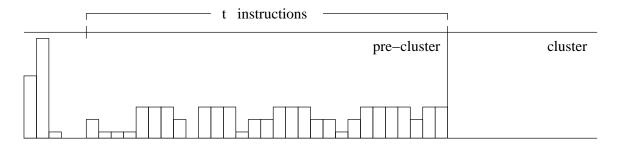

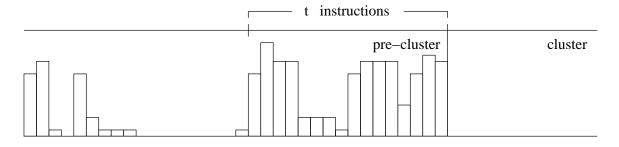

While very reliable, modeling all pre-cluster cache and branch predictor interactions is unnecessary because of the principle of temporal locality [21, 27]. The chief observation, which makes both MSE and MRRL useful for warm up acceleration, is that only the latest pre-cluster cache and branch predictor interactions will be relevant during the cluster itself. Determining a contiguous subset of the pre-cluster instruction stream—bounded from above by the last instruction of the pre-cluster phase—whose branch predictor, data cache and instruction cache accesses are likely to impact the subsequent cluster allowed me to accelerate sampled simulation relative to fullwarmup by splitting the pre-cluster instruction stream into two distinct phases. In the first phase, the simulator only performs functional simulation, updating only the architected state for each instruction. In the second phase, the simulator additionally models cache and branch predictor interactions. Then, during the cluster itself, the simulator switches to cycle-accurate simulation. This is the three-phase simulation strategy used in numerous previous works [8, 17, 18, 19, 20, 28, 42]. The first, aggressively fast phase can be considered the "cold" phase; this is followed by the "warm" phase, where cache and branch predictor interactions are modeled; and concluded by the "hot" phase where cycle-accurate simulation of the processor pipeline takes place. This is illustrated in Figure 1.1.

Current pre-cluster acceleration approaches [8, 28, 42] use crude heuristics or cum-

Figure 1.1: Pre-cluster-cluster pair subdivided into cold, warm, and hot phases. Cold phase models only architected state; warm phase models architected state, plus cache hierarchy, plus branch predictor; hot phase models pipeline in cycle-accurate detail.

bersome methods to decide the size (measured in completed instructions) of the warm phase. This motivates my

Thesis: Temporal locality suggests that those references occurring far from sample clusters are diminishingly useful for cache and branch predictor warm up. MSE can be adapted to mitigate cold-start bias by rigorously assessing a minimally sufficient number of unique memory references that must be handled within a cache in order to touch a proportion of cache blocks with probability  $p \in (0,1)$ , thereby ensuring accurate warm up for large enough p. Similarly, MRRL ensures accurate cache hierarchy and branch predictor state by engaging warm up early enough to model the effect of references that fall within the reuse distance established by the measurement of temporal locality. The capacity of both to reduce overall running time by accelerating warm up while preserving accuracy will enable MSE and MRRL to render

sampled microarchitecture simulation more efficient and therefore a more valuable tool for microarchitecture research.

The rest of this dissertation is organized as follows. The next chapter presents related work. Chapter 3 presents MSE; Chapter 4 presents the MRRL approach. Chapter 5 presents the experimental methodology and results. A detailed description of the software tools that were developed in the course of this research are described in Chapter 6. Finally, research contributions are summarized, the dissertation concludes, and potential avenues for future work are discussed in Chapter 7.

# Chapter 2

## Related Work

#### 2.1 Benchmark Sampling Strategy

Because simulating benchmarks end-to-end in cycle-accurate detail is prohibitive, several studies have explored ways to simulate only portions of the program's overall execution in cycle-accurate detail. Skadron et al. [54] used a sequence of heuristics to find a single, short but representative simulation window of 50 million instructions. The most important component of their approach is to exclude unrepresentative startup behavior from early in the benchmark's execution; Skadron et al. [54] go on to present a table of fast-forward instruction counts for the SPECInt95 benchmarks.

Lafage and Seznec [31] modify the sampling approach by using statistical classification methods to characterize the entire benchmark and provide a more rigorous guarantee of the chosen sample's representativeness. A potential problem with this approach is that finding configuration-independent metrics for representativeness is difficult.

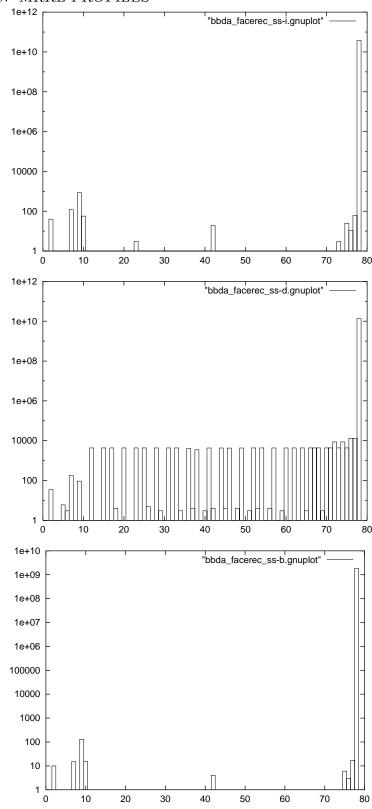

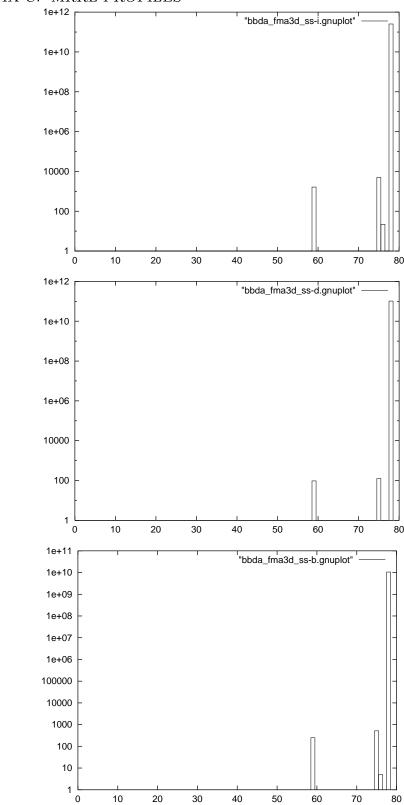

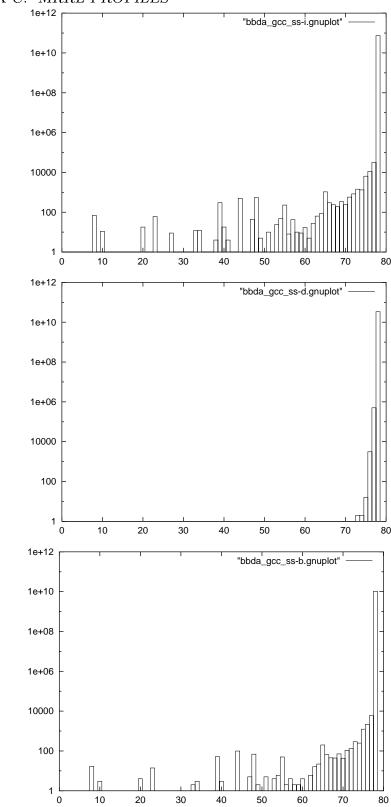

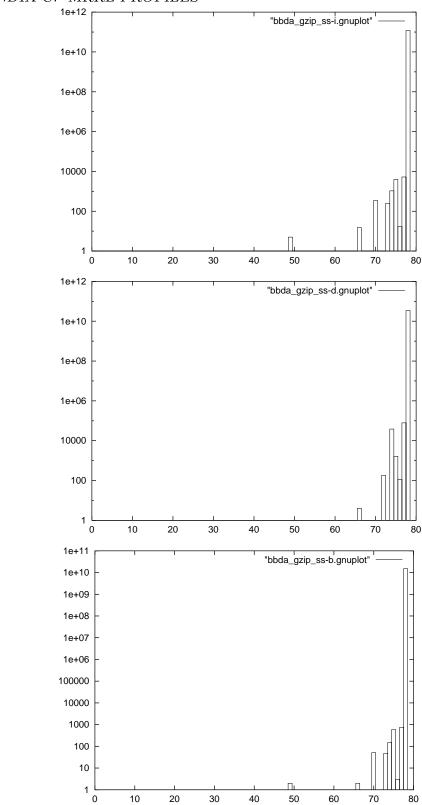

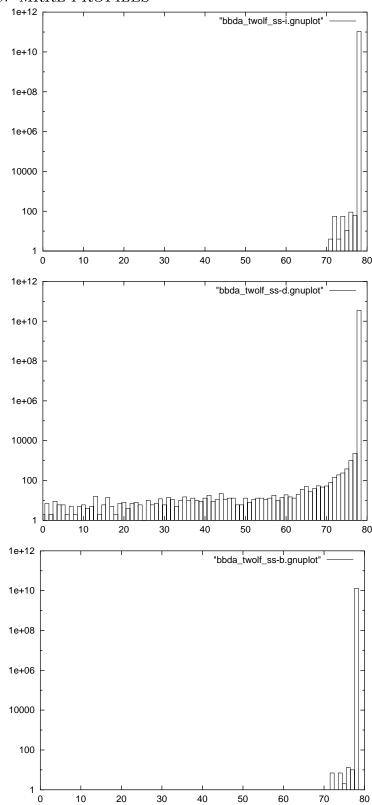

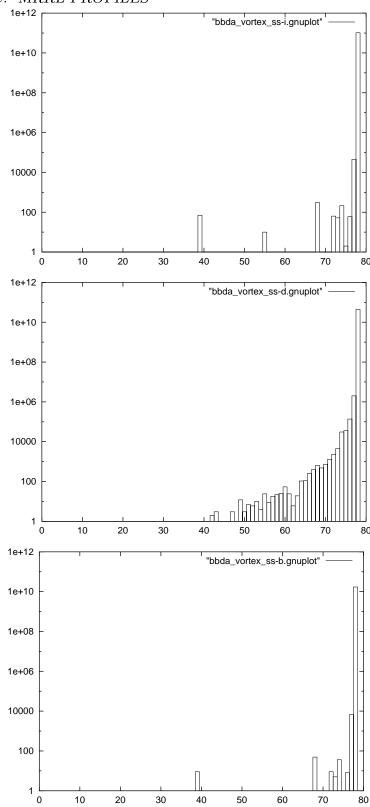

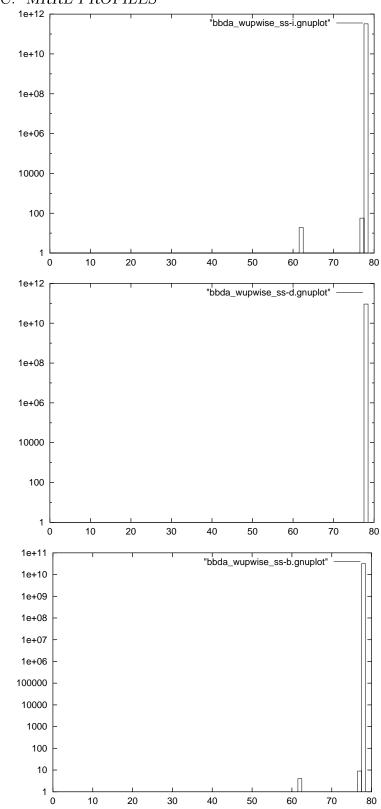

Sherwood et al. [50] propose Basic Block Distribution Analysis (BBDA). Their technique profiles the execution frequency characteristics of a benchmark's basic blocks in order to isolate a continuous subset of the dynamic instruction stream whose execution characteristics closely mimic the complete, end-to-end cycle-accurate execution of the benchmark. BBDA's key insight is that periodic basic block execution frequency reflects the periodicity of various architectural metrics such as IPC, cache miss rate, and branch predictor accuracy in cycle-accurate simulation. In subsequent work, Sherwood et al. [51] build upon the BBDA concept to create a technique that automatically isolates multiple contiguous subsets of the dynamic instruction stream since some benchmarks' behavior is too complex to be characterized by a single instruction stream slice. In both cases, their aim is to reduce simulation running times by only executing in cycle-accurate detail, a small representative subset of the dynamic instruction stream.

Conte et al. [8] take a different approach, and instead simulate multiple fixed-length clusters of instructions selected randomly from the dynamic instruction stream. Because the execution clusters are chosen randomly (i.e., such that all parts of the dynamic instruction stream have equal probability of being chosen), random cluster sampling is amenable to statistical analysis and allows the determination of a confidence interval. If one can safely assume that cold-start bias does not adversely impact simulation accuracy, then with X% confidence, the true benchmark IPC is within the confidence interval.

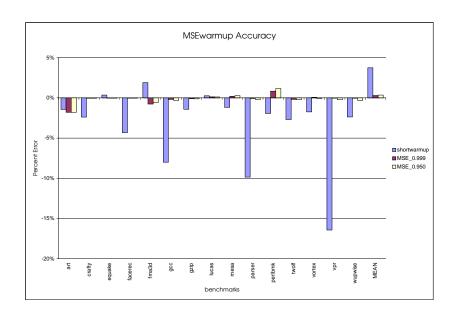

#### 2.2 Solutions to Cold-start Bias

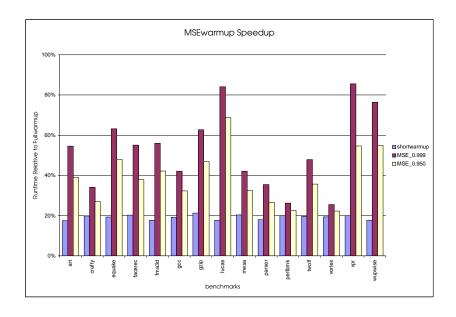

Key to Conte et al.'s [8] technique is ensuring the accuracy of the state in large structures like the caches and branch predictor. Their work addresses branch prediction structures (assuming a perfect cache) and suggests that recycling stale predictor state<sup>1</sup> from the previous cluster plus a short warm up interval [32] of at least 7,000 instructions prior to the next sample cluster is sufficient to minimize cold-start bias in the branch predictor and achieve very small errors of a few percent between the mean estimated IPC and the true IPC. Conte's warm up approach is referred to as shortwarmup in Chapter 5. Incidentally, because Conte does not treat cache effects, assuming a perfect cache in the experiments presented, MSE and MRRL address exactly the problem that Conte's method does not.

Co and Skadron [7] revisit the problem of warming up the branch predictor, but in a more modern scenario, addressing context switching. They investigated whether a process's performance could be hindered by branch predictor state loss resulting from a second (or more) process's acquisition of the CPU when the initial process reclaims the CPU and is allowed to resume. Their data show that due to the high clock speeds of modern CPUs, enough instructions are executed per quantum to reestablish branch predictor state, rendering the adverse effects of context switching induced state loss negligible. Specifically, they show that even large branch predictors train in as little as 128K instructions—a mere fraction of the instructions executed per quantum in a

<sup>&</sup>lt;sup>1</sup>By "stale state," I mean that the hardware state as it appeared at the conclusion of the prior cluster is used as the starting state of the current cluster.

modern, fast CPU—even when a process's branch predictor state is completely lost prior to reclaiming the CPU.

As a part of their PARSIM parallel microprocessor simulation system, Nguyen et al. [42] develop an analytical technique for computing warm up length. Their formula calculates a function of the cache block width, associativity, the average population density of memory references throughout the instruction stream, and the average steady-state cache miss ratio, the latter of which unfortunately, implies a one-time fullwarmup run to measure it. MSE improves upon this by making calculations based only upon the cache dimensions (i.e., the number of sets, and degrees of associativity) and is therefore free from even a one-time fullwarmup cost. PARSIM is also a trace-driven system. In response to the much increased speed of microprocessors, however, the Standard Performance Evaluation Corporation (SPEC) massively increased the running length of the benchmarks chosen for the SPEC CPU2000 suite [9]. Generating, storing, and accessing the resultant enormous traces is unattractive in terms of storage and access cost. MSE and MRRL were purposefully designed to avoid this expensive requirement.

Other heuristics for reducing cold-start bias are studied by Kessler *et al.* [28]. They consider using half of the pre-cluster references for warm up purposes; tracking only entries that are known to contain good state; using stale state from the previous cluster; and flushing state but estimating how much error this introduces.

#### 2.3 Analytical Simulation Frameworks

Thiébaut [66] describes premier work on the analytical assessment of the memory reference stream and draws an insightful analogy between memory access patterns and fractal random walks on the one-dimensional lattice. In Thiébaut's model, the one-dimensional lattice is emulated by main memory, and the stride of next reference is described by random variable U; the "walk" of the memory reference stream is fractal if [37]:

$$P[U > u] = \left(\frac{u}{u_0}\right)^{-\theta}, u \ge u_0$$

where  $u_0$  and  $\theta$  are constants computed from an analysis of a program trace.  $\theta$  is called the fractal dimension of the random walk and describes whether the random walk tends to sparsely ( $\theta < 1$ ) or repetitively ( $\theta > 1$ ) visit cells of the one-dimensional lattice. From this framework, Thiébaut describes a method for accurately predicting the miss ratio of fully associative caches. In later work [68], Thiébaut et al. builds upon the fractal random walk framework to address the generation of purely synthetic memory reference traces which accurately mimic the miss ratio of real program traces. Finally Mendelson in collaboration with Thiébaut and Pradhan [39], describe an analytical model for predicting the proportion of live<sup>2</sup> cache lines. Once again, the authors build upon the fractal random walk using the hyperbolic probability distribution function given above to develop a model that estimates the cache's steady state

<sup>&</sup>lt;sup>2</sup>By *live* I mean a cache line that will be accessed at least once before being invalidated, evicted, and refilled.

behavior. All three of these works describe techniques that are dependent upon the simulated cache block width. MSE shares this dependence; MRRL improves upon this by being entirely independent of block width.

Strecker [62] extends the work of Easton et al. [11], who present a formal model for computing the cold-start miss ratio of a fully-associative cache from the steady state miss ratio. Strecker argues however, that in a multitasking environment a tumultuous relationship exists between cache blocks belonging to different processes. If it can be safely assumed that 100% of all cache blocks are valid, this results in numerous capacity misses when an interrupted process resumes execution. (Thiébaut [67], calls the collection of cache misses that occur when a process reacquires control of the CPU the cache-reload transient.) Strecker's model presents an analytical framework for estimating the miss ratios of direct-mapped caches for multiple programs in a multitasking environment based on each program's instantaneous miss ratio. Thiébaut et al. present the reload-transient model [67]. The reload-transient model probabilistically estimates the cache-reload transient of two processes in a multitasking environment as a function of the footprints<sup>3</sup> of the two competing processes and the dimensions of the cache (e.g., number of sets, degrees of associativity). MSE shares a dependence on the dimensions of the cache; MRRL is independent of the cache dimensions.

Wood et al [72] establish the concept of cache generations. Each cache generation begins immediately after a new line is brought into the cache and ends when the line

<sup>&</sup>lt;sup>3</sup>By footprint, I refer to the number of cache lines belonging to a process.

is evicted and replaced. Their notion of cache generations establishes a framework for analytically estimating the unknown or cold-start reference miss ratio,  $\mu$ . They further establish that  $\mu$  is substantially higher than the miss ratio of references chosen at random. Armed with reliable  $\hat{\mu}$ —estimated unknown reference miss ratio—they were able to accurately measure cache miss ratios in sampled trace-driven simulations. Rather than attempting to estimate cache miss ratios, MSE and MRRL more directly address the specific issue of determining how much warm up is necessary to preserve simulation accuracy. MRRL is furthermore applicable to branch predictor warm up.

#### 2.4 Important Insights from Cache Design

In their Cache Decay research, Kaxiras et al. [27] propose a technique of cutting power to (heuristically presumed) dead cache lines, thereby reducing leakage power. Their measurements show that for a 32KB L1 data-cache, the proportion of the cache lines' dead time ranges from 45% to as much as 99% for the SPEC CPU2000 benchmarks. Their work shows that most cache lines' active lifetime is significantly longer than their useful lifetime.

Lai et al. [33] describe a new hardware mechanism called the dead block predictor (DBP) which—as its name suggests—heuristically estimates a cache block's final reference prior to being invalidated, evicted, and refilled. The DBP's operation is somewhat analogous to dynamic branch prediction. Each cache block is paired with its own dead block signature: an encoded trace of the memory reference stream since the cache block was first fetched. A table of two-bit saturating counters is used

to gauge confidence in the dead block predictions. Their measurements show that predicting the useful lifespan of individual cache blocks and initiating new block prefetches well in advance of simple demand-fetching, results in substantial CPU performance improvements.

#### 2.5 Related Work Synopsis

In short, several techniques exist for sampling execution ([8, 31, 50, 51, 54]); these methods demonstrate the effectiveness of sampling in reducing simulation times while preserving accuracy, relative to end-to-end cycle-accurate simulation. Nevertheless, all these techniques are dependent on accurate warm up of the cache and branch predictor state prior to each sample. While some heuristics for determining the amount of the pre-cluster instruction stream to warm up have been described ([7, 8, 28, 42]), I am not aware of any efforts to develop a more formal approach to minimizing warm up lengths while preserving accuracy besides the cumbersome trace-driven technique described by Nguyen [42]. Analytical frameworks for reasoning about cache behavior have also been studied ([11, 39, 62, 66, 68, 72]), but these approaches only offer insight into steady-state behavior. Finally, recent developments ([27, 33]) in cache design propose insightful clues for determining the useful lifespan of individual cache blocks.

# Chapter 3

### Minimal Subset Evaluation

Minimal Subset Evaluation [17, 20] (MSE) seeks to quantitatively assess the probability of touching a certain fraction of cache blocks based only on the cache dimensions and the count of unique memory reference addresses. This capability can be exploited to determine warm phase length necessary to warm up a small L1 cache. Many fewer native instructions are executed per simulated instruction in the cold phase than in the warm phase (both of which combine to form pre-cluster phase); hence, accurate speedup is achieved by expanding the length (in instructions) of the cold phase while leaving enough of the warm phase to accurately establish L1 cache state, allowing the cycle-accurate hot phase to execute, confident that cold-start bias has been defeated.

#### 3.1 MSE Warm Up

The *MSEwarmup* technique is an adaptation of Minimal Subset Evaluation to the problem of deciding warm phase length. *MSEwarmup* makes this determination from probability computations and data about the memory reference streams for instruc-

tions and data. The MSE formula determines the probability that handling m cache accesses by unique reference addresses will touch a given proportion of cache blocks. The steps of the adaptation for MSE warmup is enumerated below:

- 1. First, the user chooses the location of simulation sample clusters within the benchmark. (Some approaches choose just a single cluster [31, 50, 54] whereas others choose several [8, 17, 18, 19, 42, 51].)

- 2. The user selects a desired probability of accuracy  $p \in (0, 1)$ . This is a goal value. Iteratively, calculations are performed to determine the minimal m necessary to achieve probability p of touching a given proportion of the cache blocks.

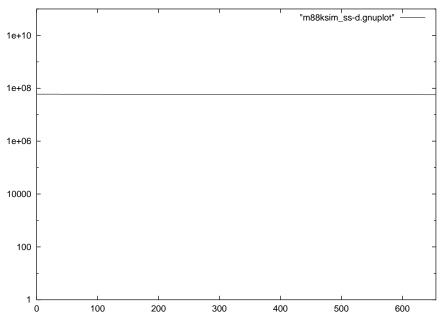

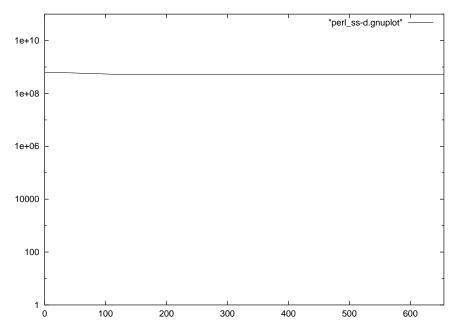

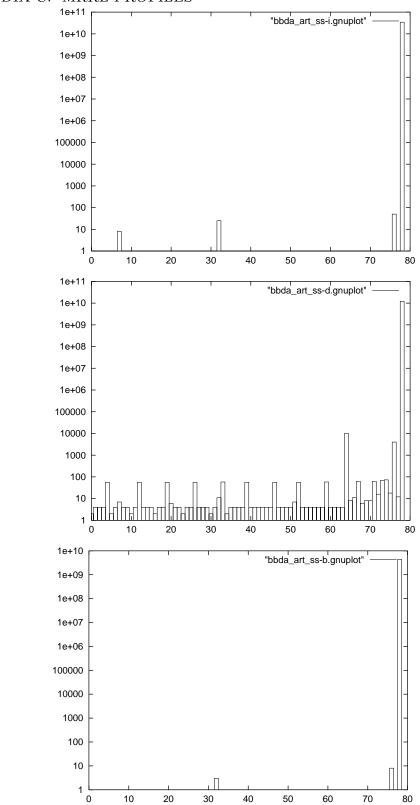

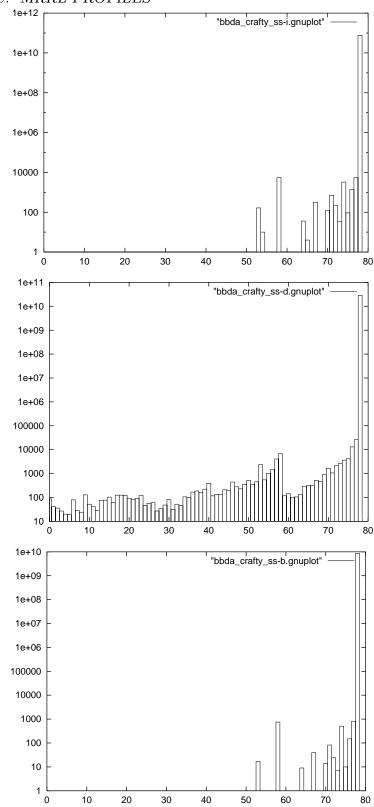

- 3. The user profiles the benchmarks to characterize the occurrence of unique<sup>1</sup> memory references. This is a one-time cost for each set of sample clusters from a benchmark-input pair; these profiles are valid for any p, and L1 cache configuration.

- 4. The user then examines the profile to determine, for each simulation sample cluster, how many total instructions, t, prior to the sample must be executed in order to observe the aforementioned MSE-prescribed m unique references.

- 5. The simulation can then be run in aggressive cold mode consisting of only functional simulation in which just architected state is simulated. At t instructions prior to the beginning of the cycle-accurate hot phase, the cold mode changes into warm mode, in which interactions with the L1 cache are also modeled.

<sup>&</sup>lt;sup>1</sup>By "unique" I mean that no two memory references access the same address.

Then, once the cluster is reached, the cache structures will with probability p have the desired proportion of blocks touched.

To thoroughly discuss MSE it is helpful to define several more variables. Let N be the number of sets in the cache and a be its associativity. (For direct-mapped caches, a = 1.) The MSE formula is then used to determine m for any p, a and N; that is, m = MSE(N, a, p).

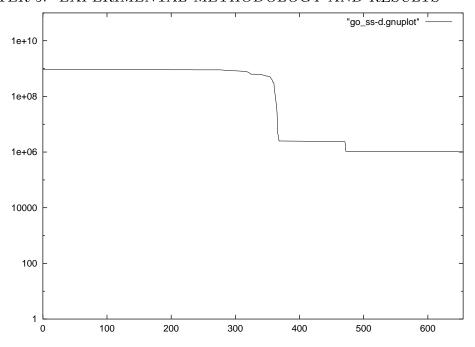

Once a probability of accuracy p has been selected, the MSE formula is calculated to arrived at the MSE-prescribed number of uniques (m). From this, t—the number of instructions to execute during the warm up interval that contains m uniques—is determined. t could be chosen, for instance, from a trace of the memory reference stream. Such traces, however, rapidly become large and unwieldy. Elnozahy [12] has addressed the cumbersome nature of traces and offers approaches that make their use more viable. Instead of dealing with full (or even compressed) traces however, I obtain t using data gathered from the MSEprofiles.

As enumerated above, *MSEwarmup* uses a two-pass process. First, I run software that I have developed which profiles the occurrence of unique memory references in the instruction- and data reference streams of each pre-cluster-cluster pair, packing that data into MSEprofiles. Second, when the cold-warm-hot simulator itself is launched, it reads the MSEprofile for the appropriate benchmark-input pair and begins simulation. The profiler works by maintaining an associative array for the stream of instruction memory references and for the stream of data memory references. Each associative array element operates like a single cache block of a fully-associative

cache whose cache block size is equal to the block size used by the cold-warm-hot simulator<sup>2</sup>. Each time a memory reference occurs, the corresponding associative array entry is logically time-stamped with the completed instruction count. At the conclusion of the profiling run, the set of timestamps are sorted in descending order; the timestamp occurring m-th in the list is the number of instructions (t) prior to the cycle-accurate sample that must be executed in order to encounter m unique memory references. In other words: t = MSEwarmup(N, a, p, MSEprofile).

In the Chapter 5 experiments, I make the assumption that the pre-cluster phase is long enough and accesses enough unique reference addresses that all Na cache blocks are touched at least once prior to the cluster. Hence, MSE is used to find the warm up interval t that touches all Na cache blocks. In general, this is not a good assumption. Some benchmarks will not touch all entries in a cache, especially a large cache, regardless of the length of the pre-cluster interval; this is what limits MSE to warming up only smaller primary (L1) caches. The problem is that for some fixed p, larger caches require larger m to touch the designated proportion of cache blocks. Thus, it becomes increasingly less likely that m or more unique references are accessed during the pre-cluster phase. If fewer than the MSE-prescribed m unique references exist among the pre-cluster instructions, a safe, conservative fallback is to let t=0. That is, when fewer than m uniques are available for the current pre-cluster-cluster 2n common block width among contemporary L1 instruction- and data caches is 32 bytes; this is the block size used for the experiments. Dependence on the cache block width is actually a limitation

of MSEwarmup that is remedied by MRRL.

pair, MSEwarmup reverts to fullwarmup. This dearth of unique references is common when attempting to warm up secondary (L2) caches which tend to be much larger than L1s. To accommodate this, MSE employs two more variables,  $\alpha$ ,  $\beta \in (0,1]$ . These parameters tune N and a in the following way:  $t = MSEwarmup(\alpha N, \beta a, p, MSEprofile)$ . Thus, if the user needs to calculate the number of unique references necessary to touch only a fraction of sets and a fraction of blocks within each set,  $\alpha < 1$  and  $\beta < 1$ .

The next section contains a thorough discussion of several important assumptions and the critically important uniformity assumption that implicitly underlies the MSE formula; the MSE formula itself, is discussed thereafter.

### 3.2 MSE Assumptions

The MSE formula  $(m = \text{MSE}(\alpha N, \beta a, p))$  calculates the probability that at least  $\alpha N$  sets of a cache will be touched at least  $\beta a$  times. The formula however, is based on the assumption that unique memory references are typically distributed uniformly throughout the cache. This assumption does not contradict the well-known, empirically demonstrated principle of locality. The critical difference is that the locality principle considers the entire stream of memory references, L. My assumption, by contrast, refers only to the subset of the memory reference stream that does not contain duplicates, unique(L).

Indeed, uniform distribution of unique memory reference addresses is exactly the ideal behavior for a cache because this would reduce the likelihood of conflicts (i.e.,

having two different references map to the same location within the cache). In an ideal direct-mapped cache, for instance, if all cache blocks are valid, data in any set would have a  $\frac{N-1}{N}$  chance of surviving a unique incoming reference address; the larger the N, the greater the chance of survival.

To verify the uniform distribution of unique(L) throughout the cache analytically, I employed the  $\chi^2$  goodness-of-fit test [13, 59, 64]. I developed software that counts (based on some assumed cache block width) the number of references to each cache set among the unique references only. From this, I first tallied the total number of unique memory accesses, |unique(L)|, and calculated a best estimate expected number of accesses per set

$$ar{x} = rac{|unique(L)|}{N}$$

Using  $\bar{x}$ , sets are grouped into bins such that the best estimate average number of accesses per bin is at least 5 [13, 64]. Finally, I used these data to compute  $\chi_o^2$ : the observed  $\chi^2$ . For all benchmarks and for every cache configuration tested, the raw profile data passes the  $\chi^2$  test of the null hypothesis that the distribution of cache accesses among the unique references is uniform at the 1% level of significance. Table 3.1 gives the  $\chi^2$  values computed for each benchmark, each cache configuration  $(N \in \{256,512,1024,2048\})$ , the degrees of freedom and the corresponding 1% critical value.

I also performed the same test on the profile data from the SPEC CPU2000 benchmarks. Experiments on these benchmarks use multiple-cluster simulation; thus I was

| $N=256;df=254,cv_{0.01}=309$ |                                         |                                      |  |  |  |  |  |

|------------------------------|-----------------------------------------|--------------------------------------|--|--|--|--|--|

|                              | $\chi_o^2$                              | $P(\chi_{0.01,254}^2 \ge \chi_o^2)$  |  |  |  |  |  |

| compress                     | 0.254                                   | 1.000                                |  |  |  |  |  |

| gcc                          | 149.098                                 | 1.000                                |  |  |  |  |  |

| go                           | 296.164                                 | 0.036                                |  |  |  |  |  |

| ijpeg                        | 135.636                                 | 1.000                                |  |  |  |  |  |

| m88ksim                      | 3.556                                   | 1.000                                |  |  |  |  |  |

| perl                         | 41.148                                  | 1.000                                |  |  |  |  |  |

|                              | 12; df = 5                              | $510, cv_{0.01} = 587$               |  |  |  |  |  |

|                              | $\chi_o^2$                              | $P(\chi^2_{0.01,510} \ge \chi^2_o)$  |  |  |  |  |  |

| compress                     | 0.000                                   | 1.000                                |  |  |  |  |  |

| gcc                          | 140.250                                 | 1.000                                |  |  |  |  |  |

| go                           | 0.000                                   | 1.000                                |  |  |  |  |  |

| ijpeg                        | 161.670                                 | 1.000                                |  |  |  |  |  |

| m88ksim                      | 11.220                                  | 1.000                                |  |  |  |  |  |

| perl                         | 149.940                                 | 1.000                                |  |  |  |  |  |

| N = 102                      | 24; df = 10                             | $022, cv_{0.01} = 1130$              |  |  |  |  |  |

|                              | $\chi_o^2$                              | $P(\chi_{0.01,1022}^2 \ge \chi_o^2)$ |  |  |  |  |  |

| compress                     | 3.066                                   | 1.000                                |  |  |  |  |  |

| gcc                          | 945.350                                 | 0.958                                |  |  |  |  |  |

| go                           | 0.000                                   | 1.000                                |  |  |  |  |  |

| ijpeg                        | 247.324                                 | 1.000                                |  |  |  |  |  |

| m88ksim                      | 0.000                                   | 1.000                                |  |  |  |  |  |

| perl                         | 357.700                                 | 1.000                                |  |  |  |  |  |

| N = 204                      | $N = 2048; df = 2046, cv_{0.01} = 2197$ |                                      |  |  |  |  |  |

|                              | $\chi_o^2$                              | $P(\chi_{0.01,2046}^2 \ge \chi_o^2)$ |  |  |  |  |  |

| compress                     | 0.000                                   | 1.000                                |  |  |  |  |  |

| gcc                          | 75.702                                  | 1.000                                |  |  |  |  |  |

| go                           | 0.000                                   | 1.000                                |  |  |  |  |  |

| ijpeg                        | 619.938                                 | 1.000                                |  |  |  |  |  |

| m88ksim                      | 0.000                                   | 1.000                                |  |  |  |  |  |

| perl                         | 716.100                                 | 1.000                                |  |  |  |  |  |

Table 3.1:  $\tilde{\chi}_0^2$  for SPECInt95 benchmarks and various N; df is the number of degrees-of-freedom;  $cv_{0.01}$  is the critical value of  $\chi_o^2$  at the 1% level of significance.

forced to perform the  $\chi^2$  test for each pre-cluster phase individually. The results were similar to those presented in Table 3.1: statistically close to uniform for the MSE formula to yield reliable results. This assessment is additionally supported by the successful application of MSEwarmup to multiple-cluster simulations (see Table 5.6).

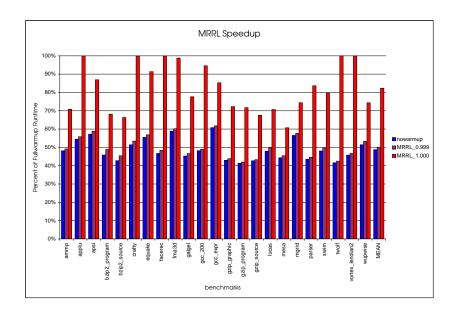

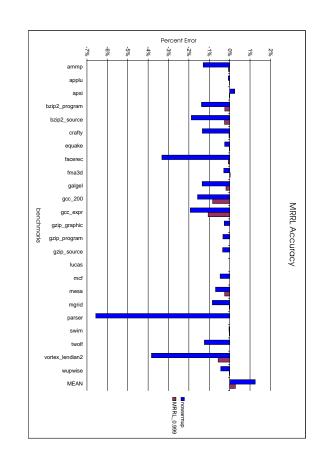

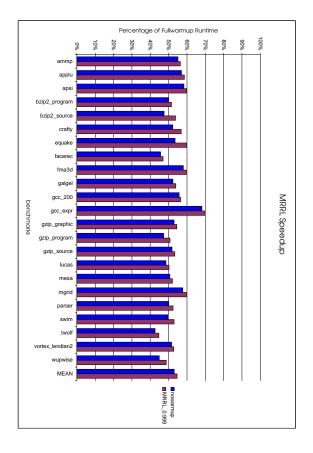

A possible hole in the uniformity assumption is second-level (L2) caches. L2 caches typically have a much larger volume and greater cache block capacity than L1 caches. L2s are furthermore, typically unified, hosting instructions and data. It is possible that some programs' instruction- and data reference streams will destructively interfere with each other in a unified L2, invalidating the assumed uniform distribution of unique memory references. Hence, a second assumption is that the MSE formula is performing calculations based on a non-unified cache.