## BREAKING THE MEMORY WALL FOR HIGHLY MULTI-THREADED CORES

THIS DISSERTATION IS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY COMPUTER SCIENCE

Jiayuan Meng

Aug. 10, 2010

Approvals:

Kevin Skadron (Advisor)

John Lach

Kim Hazelwood

Jason Lawrence

Nathan Binkert

Accepted by the School of Engineering and Applied Science:

James H. Aylor (Dean)

Aug. 10, 2010

## Abstract

**E** merging applications such as scientific computation, media processing, machine learning and data mining are commonly computation- and data- intensive [1], and they usually exhibit abundant parallelism. These applications motivate the design of throughputoriented many- and multi-core architectures that employ many small and simple cores and scale up to large thread counts. The cores themselves are also typically multi-threaded. Such organizations are sometimes referred to as Chip Multi-Threading (CMT). However, with tens or hundreds of concurrent threads running on a single chip, throughput is not limited by the computation resources, but by the overhead in data movement. In fact, adding more cores or threads is likely to harm performance due to contention in the memory system.

It is therefore important to improve data management to either reduce or tolerate data movement and associated latencies. Several techniques have been proposed for conventional multi-core organizations. However, the large thread count per core in CMT poses new challenges: much lower cache capacity per thread, nonuniform overhead in thread communication, inability of aggressive out-of-order execution to hide latency, and additional memory latency caused by SIMD constraints. To address the above challenges, we propose several techniques. Some reduce contention in either private caches or shared caches; some identify the right amount of computation to replicate to reduce communication, and some reconfigure SIMD architectures at runtime. Our objective is to allow CMTs to achieve scalable performance along with the thread count, despite limited energy budget for their memory system.

# Acknowledgments

I am fortunate to have Prof. Kevin Skadron as my Ph.D. advisor. His enlightening guidance and thorough training has led me through my Ph.D. study. But that is not all. He has also been a great high school English teacher and a great mentor — at the time that I was admitted to graduate school, I never thought I would devote my research to computer architecture and parallel computing. I have learned much from him, not only about how to research, but also about presenting ideas, debating with logic, collaborating with others, as well as time management. I am grateful about his tremendous support for my personal life, which gave time to visit my family and balance life with work. His patience has given me time to seek ideas without being blamed for nonproductivity. I am also deeply thankful for his continuous encouragement along the way, and his generous guidance on my career development.

I would also like to thank Dr. Dee A. B. Weikle, who has co-advised me during my first two years of graduate study. She has been a great mentor on scientific research and analysis, and her kindness helped me settle down at UVA and start my research. She has been immensely supportive.

I am indebted to the LAVA group and my outstanding colleagues for their tremendous help and enlightening discussions. They have generously shared their opinions and supported me greatly in both research and technical writing. They have also made my life at UVA more fun. Especially, I want to thank Jeremy W. Sheaffer, Karthik Sankaranarayanan, Yingmin Li, David Tarjan, Shuai Che, Michael Boyer, Mario D. Marino, Lukasz Szafaryn, and Greg Faust.

I would like to thank my Ph.D. committee, Dr. Nathan Binkert, Prof. Kim Hazelwood, Prof. John Lach, and Prof. Jason Lawrence for their valuable comments. I also enjoy exchanging thoughts with Prof. Sudhanva Gurumurthi, Prof. Marty Humphrey, Prof. Andrew Grimshaw, and Prof. Lieven Eeckhout. Their insightful suggestions have helped me clear many of my doubts.

I am also deeply thankful to my supervisor Dr. Srimat Chakradhar, Prof. Anand Raghunathan, and my colleague Dr. Surendra Byna during my internship at NEC Laboratories America. I have learned a great deal from them, and I enjoyed the time working together with them. I also appreciate their tremendous support for my career development.

I have also made many good friends at University of Virginia, too many to name here, but in particular I want to mention Rui Wang, Lingjia Tang, Yafeng Wu, Wei Le, Jiakang Lu, Jie Li, Jiawei Huang, Jason Mars, and Jiajun Zhu, all of whom provided valuable friendship and support. I also want to thank Kenneth Hoste from Ghent University, who has been a good friend and collaborator.

Moreover, to the staff members and computing facilities committee, I offer thanks for tolerating me and my hungry simulations: Andrew Grimshaw, Scott Ruffner, Essex Scales, Jessica Greer, and Rick Stillings. I cannot count how many times I have crashed the department's machines, and if it were not for their timely and skillful support, I would have halted the department. I would also like to thank their patience in teaching me how to use the resources in a right manner. I would also like to thank Brenda Perkins and Wendy Morris for their countless help. In addition, much of my work depends on the M5 simulator, and I thank the M5 team for their time and effort in answering my many questions, good or bad.

Last but not least, I would like to thank my family. Their unconditional love has been

granting me the strength and momentum to pursue excellence. Without the encouragement and inspiration from my fiancée, Wa Yuan, I would not have been able to complete my study. I also greatly appreciate the understanding and support from my parents, who always back me up they are on the other side of the globe. I dedicate this dissertation to all of them.

This work was supported in part by SRC grant no. 1607, NSF grant nos. IIS-0612049 and CNS-0615277, a grant from Intel Research, a professor partnership award from NVIDIA Research, and an NVIDIA Ph.D. fellowship.

# Contents

| Ał | ostract | t       |                                                       | 4  |

|----|---------|---------|-------------------------------------------------------|----|

| Ac | know    | ledgme  | nts                                                   | 6  |

| 1  | Intr    | oductio | n                                                     | 21 |

|    | 1.1     | Introd  | uction to Chip Multi-Threading                        | 21 |

|    | 1.2     | The M   | lemory Wall for Chip Multi-Threading                  | 23 |

|    | 1.3     | Challe  | nges in CMT Data Management                           | 24 |

|    | 1.4     | Data N  | Management for Multi-Threaded Cores                   | 26 |

|    |         | 1.4.1   | Background                                            | 26 |

|    |         | 1.4.2   | Uniform Data Distribution in Shared Cache             | 28 |

|    |         | 1.4.3   | Fine grained, Inter-Thread Data Sharing               | 29 |

|    |         | 1.4.4   | Replicating Computation to Reduce Communication       | 30 |

|    |         | 1.4.5   | Overcoming SIMD Constraints for Better Latency Hiding | 31 |

|    |         | 1.4.6   | Dynamically Adapted SIMD for Robust Performance       | 32 |

|    | 1.5     | Disser  | tation Organization                                   | 33 |

| 2  | Sim     | ulating | General Purpose Multi-Threaded Cores                  | 34 |

|    | 2.1     | Introd  | uction                                                | 34 |

|    | 2.2     | Summ    | ary of Available General Purpose Simulators           | 36 |

|   | 2.3 | The M     | V5 Simulator                                      | 38 |

|---|-----|-----------|---------------------------------------------------|----|

|   |     | 2.3.1     | Modules and their Extendability                   | 38 |

|   |     | 2.3.2     | Latency, Power, and Area Modeling and Validation  | 41 |

|   |     | 2.3.3     | System Reconfigurations and Data Collections      | 42 |

|   |     | 2.3.4     | Manageable, Interactive Design Space Exploration  | 44 |

|   | 2.4 | Major     | MV5 Simulation Parameters                         | 46 |

|   | 2.5 | Conclu    | usion                                             | 47 |

| 3 | Exp | loiting ] | Inter-thread Spatial and Temporal Locality        | 49 |

|   | 3.1 | Introd    | uction                                            | 49 |

|   | 3.2 | Backg     | round                                             | 52 |

|   |     | 3.2.1     | Affinity-Aware Task Scheduling                    | 53 |

|   |     | 3.2.2     | Contention Reduction among Threads                | 55 |

|   |     | 3.2.3     | Fine-grained Parallelism and Vector Processing    | 56 |

|   | 3.3 | Symbi     | otic Affinity Scheduling for Data-Parallelism     | 57 |

|   |     | 3.3.1     | Tiling for Symbiotic Threads                      | 57 |

|   |     | 3.3.2     | Case Study: HotSpot                               | 60 |

|   | 3.4 | Impler    | nentation                                         | 61 |

|   |     | 3.4.1     | Over-Decomposition and Load Balancing             | 64 |

|   | 3.5 | Metho     | dology                                            | 65 |

|   |     | 3.5.1     | Modeling and Configuration                        | 66 |

|   |     | 3.5.2     | Benchmarks                                        | 67 |

|   | 3.6 | Evalua    | tion                                              | 67 |

|   |     | 3.6.1     | Performance Speedup                               | 70 |

|   |     | 3.6.2     | Data Reuse and Contention Reduction               | 71 |

|   |     | 3.6.3     | Scalability through Reduced L1 D-cache Footprints | 73 |

|   |     | 3.6.4    | Sensitivity on Various Shared Cache Designs        | . 74  |

|---|-----|----------|----------------------------------------------------|-------|

|   |     | 3.6.5    | Applicability with Various Pipeline Configurations | . 76  |

|   |     | 3.6.6    | Energy Savings                                     | . 79  |

|   | 3.7 | Conclu   | usions and Future Work                             | . 79  |

| 4 | Avo | iding Ca | ache Thrashing in Shared Cache                     | 82    |

|   | 4.1 | Introd   | uction and Background                              | . 82  |

|   | 4.2 | Non-u    | niform Distribution of Private Data                | . 85  |

|   | 4.3 | Experi   | mental Setup                                       | . 88  |

|   |     | 4.3.1    | Simulation                                         | . 88  |

|   |     | 4.3.2    | Benchmarks                                         | . 90  |

|   | 4.4 | Appro    | aches to Reduce LLC Conflicts                      | . 90  |

|   |     | 4.4.1    | Randomly Offsetting Stack Bases                    | . 91  |

|   |     | 4.4.2    | LLC Replacement Policies                           | . 92  |

|   |     | 4.4.3    | Non-Inclusive, Semi-Coherent Cache Hierarchy       | . 92  |

|   | 4.5 | Evalua   | ation                                              | . 94  |

|   |     | 4.5.1    | Performance Scaling                                | . 96  |

|   |     | 4.5.2    | LLC Sensitivity                                    | . 97  |

|   | 4.6 | Conclu   | usions and Future Work                             | . 99  |

| 5 | Rep | licate C | computation to Reduce Communication                | 101   |

|   | 5.1 | Introd   | uction                                             | . 101 |

|   | 5.2 | Relate   | d Work                                             | . 104 |

|   | 5.3 | Ghost    | zones on GPUs                                      | . 107 |

|   |     | 5.3.1    | Ghost Zones in Distributed Environments            | . 107 |

|   |     | 5.3.2    | CUDA and the Tesla Architecture                    | . 108 |

|   |     | 5.3.3    | Implementing Ghost Zones in CUDA                   | . 109 |

|   | 5.4 | Model  | ling Methodology                                         | . 111 |

|---|-----|--------|----------------------------------------------------------|-------|

|   |     | 5.4.1  | Performance Modeling for Trapezoids on CUDA              | . 111 |

|   |     | 5.4.2  | Memory Transfers                                         | . 114 |

|   |     | 5.4.3  | Computation                                              | . 116 |

|   |     | 5.4.4  | Global Synchronization                                   | . 119 |

|   |     | 5.4.5  | Extension: Modeling Memory Fence                         | . 120 |

|   |     | 5.4.6  | Extensibility to Other Platforms                         | . 122 |

|   | 5.5 | Experi | iments                                                   | . 122 |

|   |     | 5.5.1  | Benchmarks                                               | . 124 |

|   |     | 5.5.2  | Model Validation                                         | . 125 |

|   |     | 5.5.3  | Sources of Inaccuracy                                    | . 127 |

|   |     | 5.5.4  | Performance Optimization                                 | . 129 |

|   |     | 5.5.5  | The Choice to Use Memory Fences                          | . 131 |

|   | 5.6 | Sensit | ivity Study                                              | . 133 |

|   |     | 5.6.1  | Component Analysis                                       | . 133 |

|   |     | 5.6.2  | Insensitive Factors                                      | . 136 |

|   |     | 5.6.3  | Application Sensitivity                                  | . 137 |

|   |     | 5.6.4  | System Sensitivity                                       | . 138 |

|   |     | 5.6.5  | Energy Consumption                                       | . 141 |

|   | 5.7 | An Au  | atomated Framework Template for Trapezoid Optimization   | . 142 |

|   | 5.8 | Conclu | usions and Future Work                                   | . 143 |

| 6 | D   | anda N | Vour Subdivision for Latency Hiding Unon SIMD Divergence | 144   |

| 6 | v   |        | Warp Subdivision for Latency Hiding Upon SIMD Divergence | 144   |

|   | 6.1 | Introd | uction                                                   | . 144 |

|   | 6.2 | Impac  | t of Memory Latency Divergence                           | . 148 |

|   | 6.3 | Metho  | odology                                                  | . 150 |

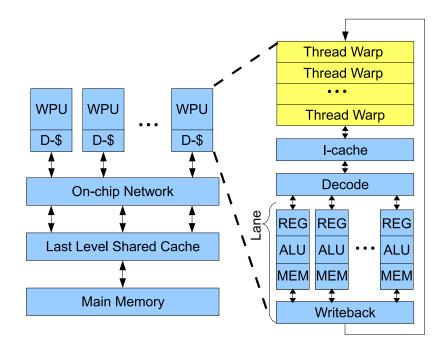

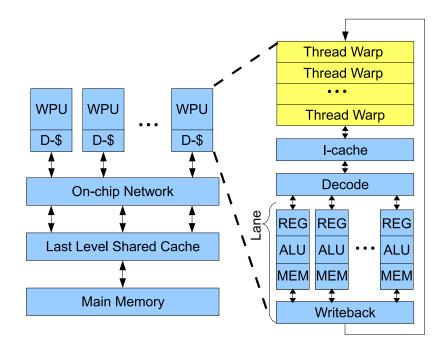

|   |     | 6.3.1   | Overall Architecture                                           |

|---|-----|---------|----------------------------------------------------------------|

|   |     | 6.3.2   | Benchmarks                                                     |

|   |     | 6.3.3   | Architecture Details                                           |

|   | 6.4 | Dynam   | nic Warp Subdivision Upon Branch Divergence                    |

|   |     | 6.4.1   | Branch Divergence, Memory Latency and MLP                      |

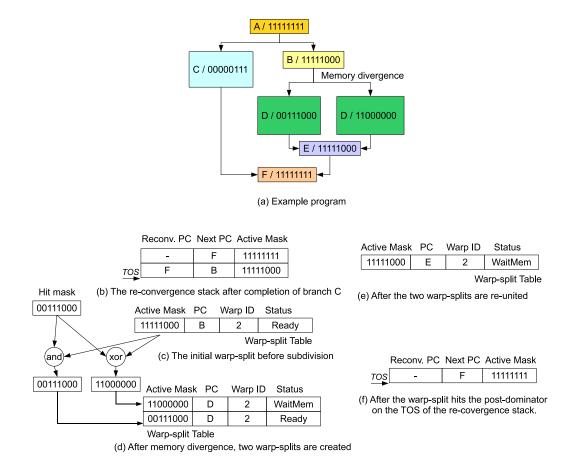

|   |     | 6.4.2   | Relaxing the Re-convergence Stack for Memory Throughput 158    |

|   |     | 6.4.3   | Over-subdivision                                               |

|   |     | 6.4.4   | Unrelenting Subdivision                                        |

|   |     | 6.4.5   | PC-based Re-convergence                                        |

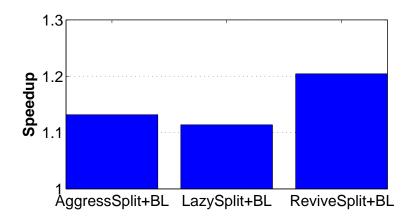

|   |     | 6.4.6   | Results                                                        |

|   | 6.5 | Dynam   | nic Warp Subdivision Upon Memory Divergence                    |

|   |     | 6.5.1   | Improve Performance upon Memory Divergence                     |

|   |     | 6.5.2   | Preventing Over-subdivision                                    |

|   |     | 6.5.3   | To Re-converge or To Run Ahead                                 |

|   |     | 6.5.4   | Implementation                                                 |

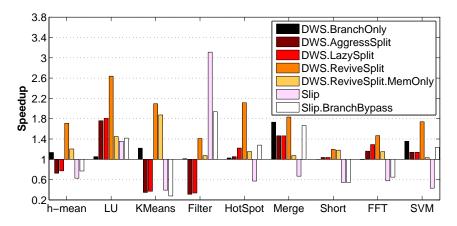

|   |     | 6.5.5   | Results                                                        |

|   |     | 6.5.6   | Hardware Overhead                                              |

|   |     | 6.5.7   | Comparison with Adaptive Slip                                  |

|   | 6.6 | Sensiti | vity Analysis                                                  |

|   |     | 6.6.1   | Cache Misses and Memory Divergence                             |

|   |     | 6.6.2   | Miss Latency                                                   |

|   | 6.7 | Related | d Work                                                         |

| 7 | Rob | ust SIM | D: Dynamically Adapted SIMD Width and Multi-Threading Depth183 |

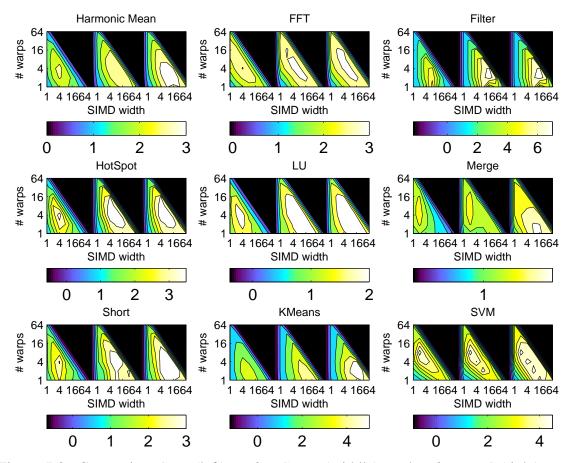

|   | 7.1 | Introdu | action                                                         |

|   | 7.2 | Related | d Work                                                         |

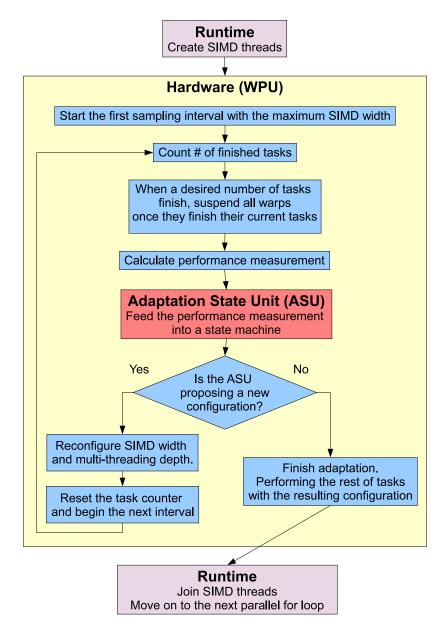

|   | 7.3 | An Ad   | laptive SIMD Architecture                                | . 191 |

|---|-----|---------|----------------------------------------------------------|-------|

|   |     | 7.3.1   | Software Support for Reconfigurable SIMD                 | . 192 |

|   |     | 7.3.2   | Hardware Support for An Adaptive SIMD Architecture       | . 193 |

|   | 7.4 | Metho   | odology                                                  | . 197 |

|   |     | 7.4.1   | Simulation Infrastructure                                | . 198 |

|   |     | 7.4.2   | Benchmarks                                               | . 200 |

|   |     | 7.4.3   | Data-Parallel Programming Models                         | . 200 |

|   |     | 7.4.4   | Load Balancing                                           | . 201 |

|   | 7.5 | Adapta  | ation Strategies                                         | . 202 |

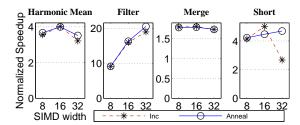

|   |     | 7.5.1   | Exploring Various Strategies                             | . 204 |

|   |     | 7.5.2   | Convergence Robustness                                   | . 205 |

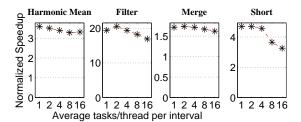

|   |     | 7.5.3   | Length of Sampling Intervals                             | . 206 |

|   |     | 7.5.4   | Hardware Overhead                                        | . 207 |

|   | 7.6 | Evalua  | ation                                                    | . 209 |

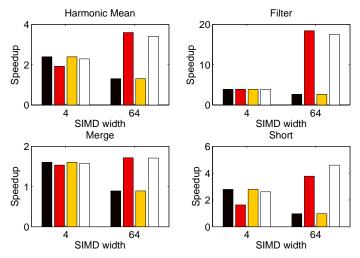

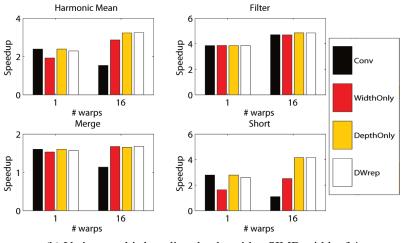

|   |     | 7.6.1   | Robustness Across Various Benchmarks                     | . 209 |

|   |     | 7.6.2   | Robust SIMD Combined with Dynamic Warp Subdivision       | . 211 |

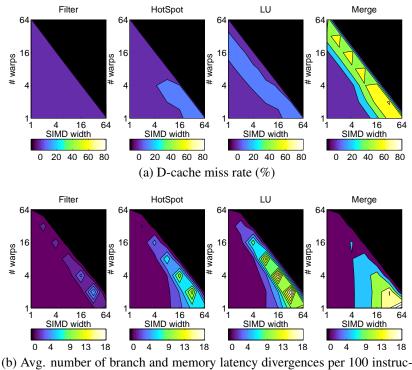

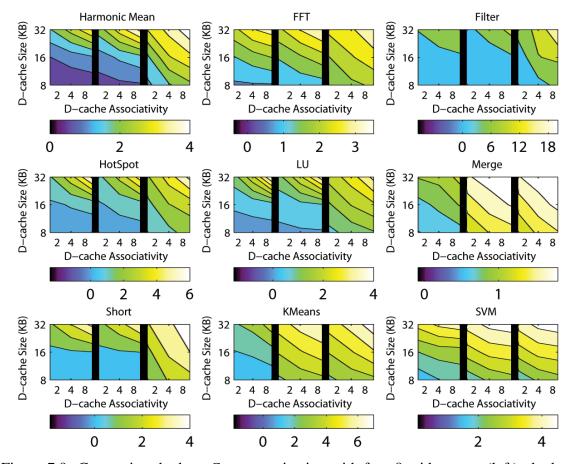

|   |     | 7.6.3   | Robustness Across Various D-Cache Settings               | . 214 |

|   |     | 7.6.4   | Effectiveness in Latency Hiding and Contention Reduction | . 216 |

|   | 7.7 | Conclu  | usions and Future Work                                   | . 217 |

| 8 | Con | clusion | s and Future Work                                        | 219   |

|   | 8.1 | Thesis  | Summary                                                  | . 219 |

|   | 8.2 | Lessor  | ns Learned                                               | . 221 |

|   | 8.3 | Future  | Directions                                               | . 222 |

|   |     | 8.3.1   | Memory System Organization for CMT                       | . 223 |

|   |     | 8.3.2   | Better Latency Hiding for SIMD Architecture              | . 224 |

### Bibliography

# **List of Figures**

| 1.1  | Trends for area breakdown of a chip                                          | 22 |

|------|------------------------------------------------------------------------------|----|

| 2.1  | Various system configurations: (a) dual core; (b) tiled cores; (c) heteroge- |    |

|      | neous cores.                                                                 | 43 |

| 3.1  | Comparing I-tile and S-tile in the context of HotSpot                        | 58 |

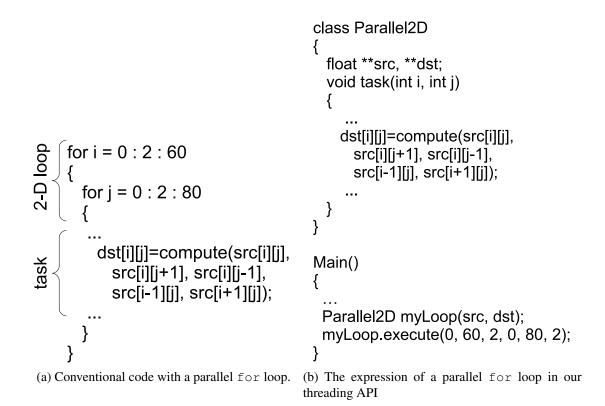

| 3.2  | Representation of a parallel for loop.                                       | 63 |

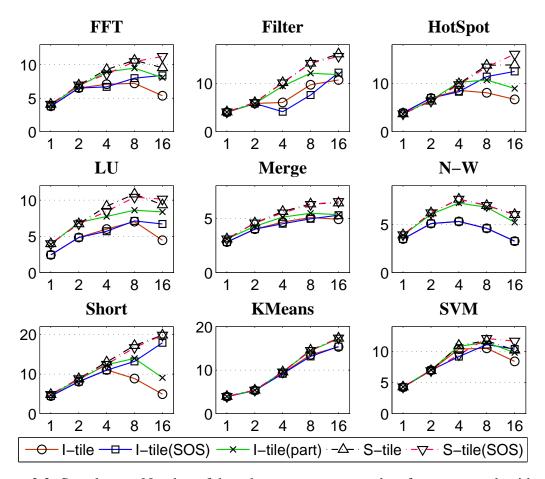

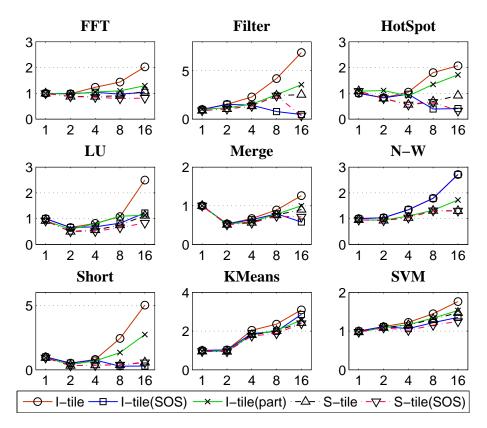

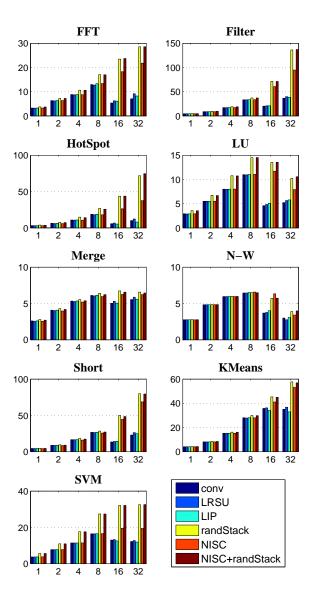

| 3.3  | Speedup vs. Number of threads per core                                       | 69 |

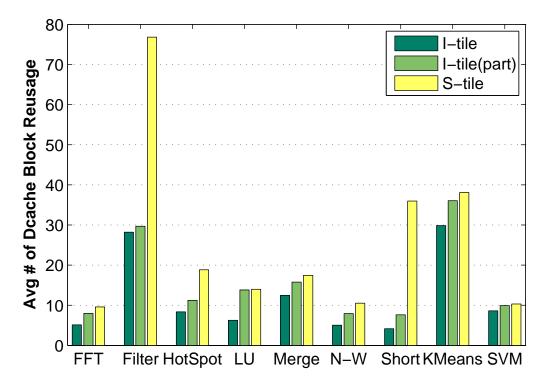

| 3.4  | The average number of reuses for D-cache blocks                              | 70 |

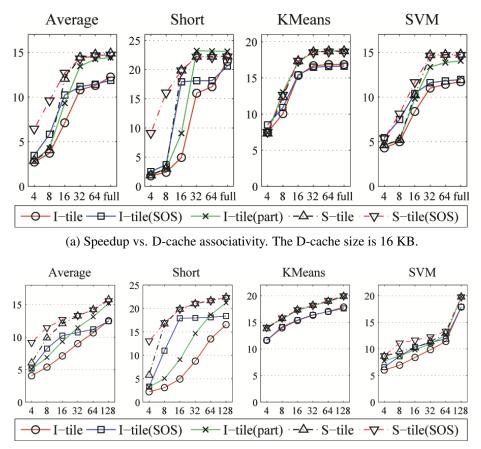

| 3.5  | D-cache sensitivity study conducted over a 16-way CMT                        | 73 |

| 3.6  | Number of D-cache first misses vs. Number of threads per core                | 75 |

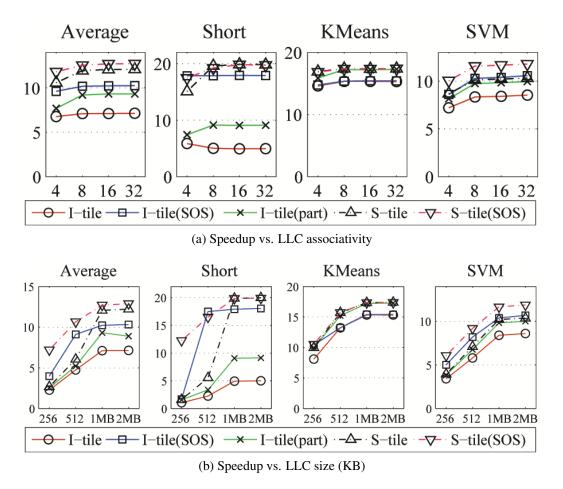

| 3.7  | Sensitivity to the LLC cache design on a 16-way CMT                          | 76 |

| 3.8  | Performance comparison of S-tile and I-tile over various multi-threaded      |    |

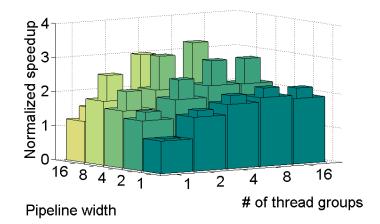

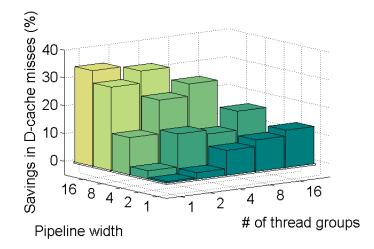

|      | cores                                                                        | 77 |

| 3.9  | S-tile's average savings in D-cache misses                                   | 77 |

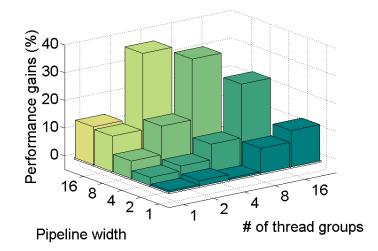

| 3.10 | S-tile's average performance gains compared to I-tile(part). Data is aver-   |    |

|      | aged across all benchmarks.                                                  | 78 |

| 3.11 | Energy savings of S-tile.                                                    | 80 |

| 4.1  | The OS and the cache interpret the same physical address differently         | 86 |

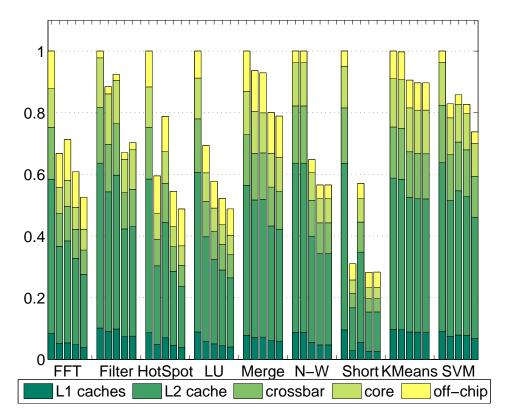

| 4.2  | Effect of non-uniform data distribution in LLC                              |

|------|-----------------------------------------------------------------------------|

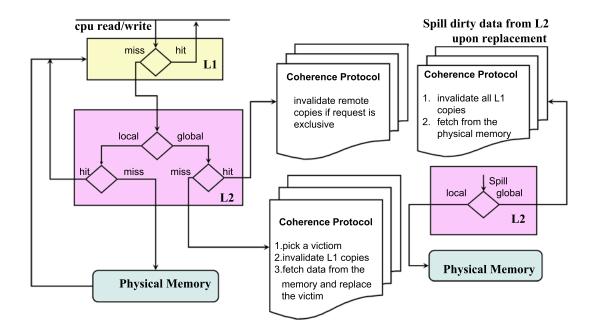

| 4.3  | The NISC protocol based on MESI                                             |

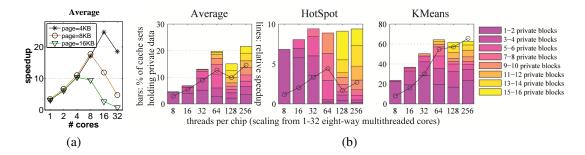

| 4.4  | Speedup vs. Number of eight-way multithreaded cores                         |

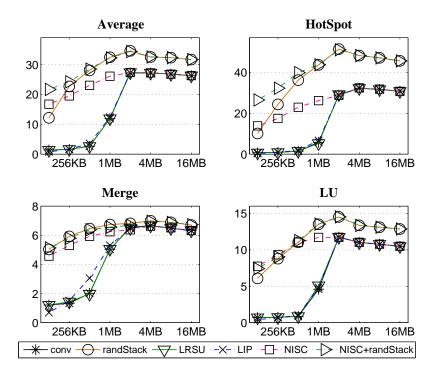

| 4.5  | Speedup vs. LLC sizes                                                       |

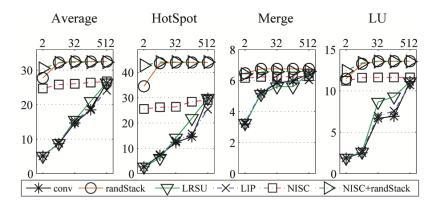

| 4.6  | Speedup vs. LLC associativity                                               |

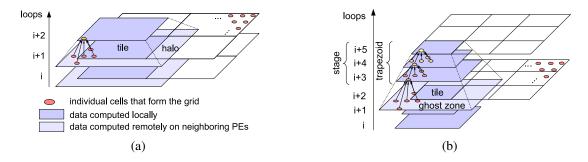

| 5.1  | Iterative stencil loops and ghost zones                                     |

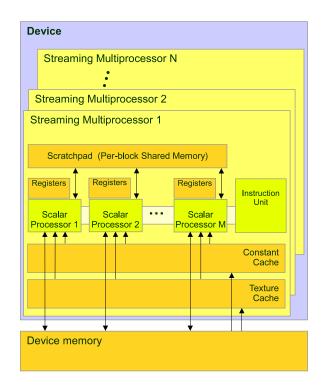

| 5.2  | CUDA's shared memory architecture. Courtesy of NVIDIA                       |

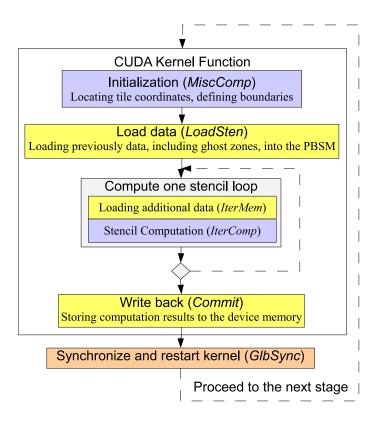

| 5.3  | Abstraction of CUDA implementation for ISLs with ghost zones 113            |

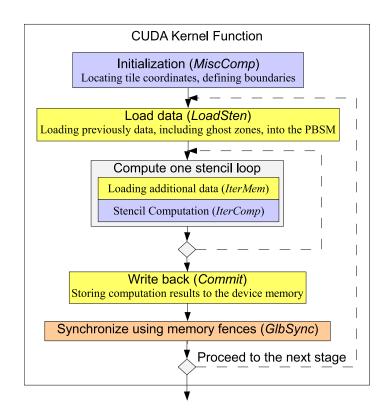

| 5.4  | Abstraction of CUDA implementation for ISLs with ghost zones 121            |

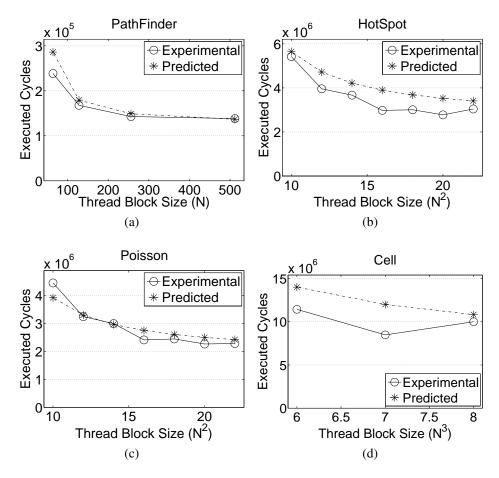

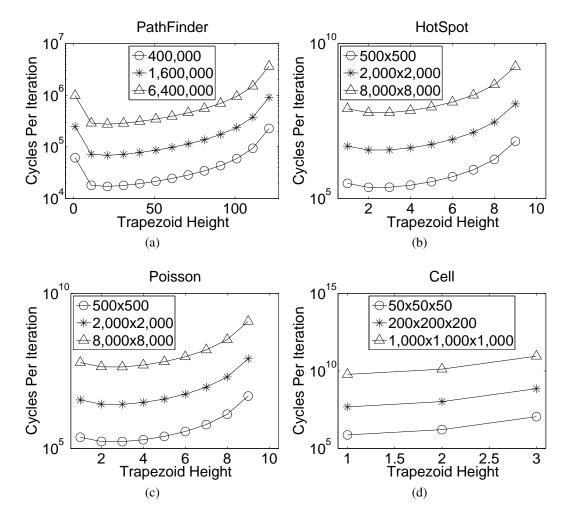

| 5.5  | Model verification by scaling the thread block size                         |

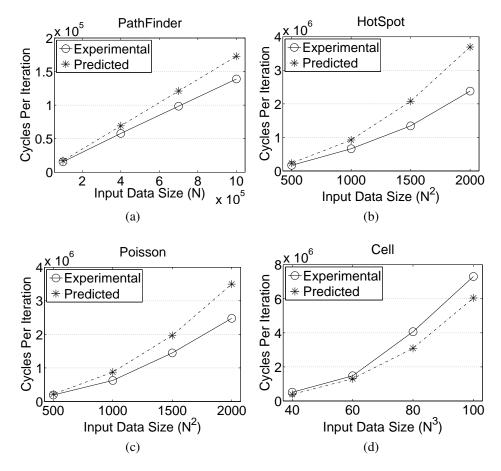

| 5.6  | Model verification by scaling the input size                                |

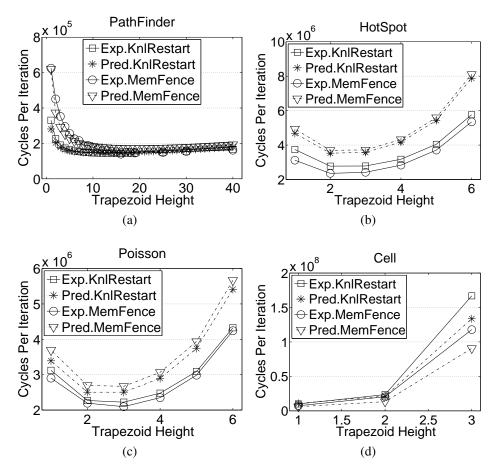

| 5.7  | Evaluating the performance optimization by scaling the trapezoid height 132 |

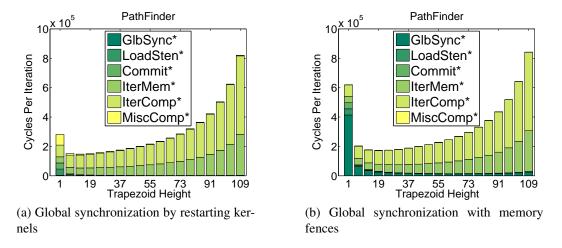

| 5.8  | Estimated performance breakdown for PathFinder                              |

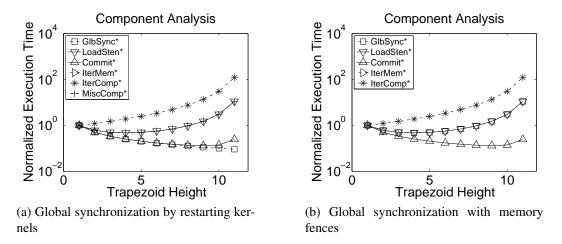

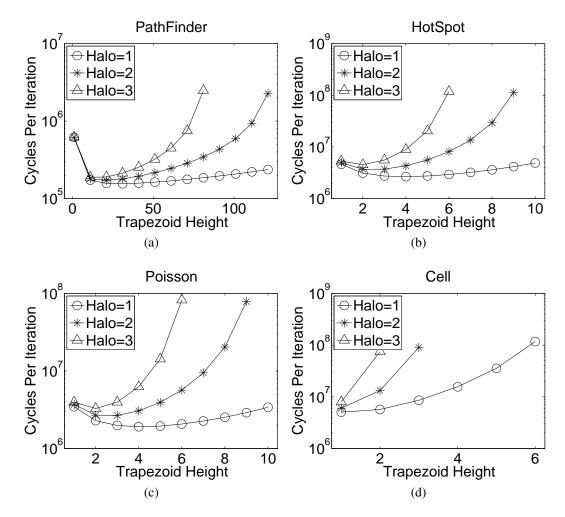

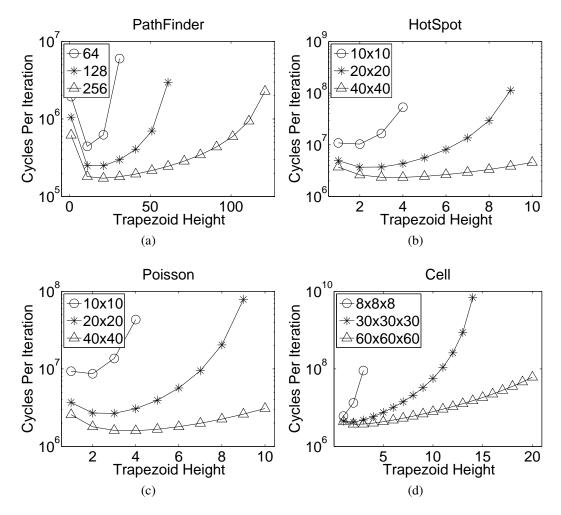

| 5.9  | Detailed study of the effects of trapezoid's height                         |

| 5.10 | Effect of various input sizes on performance speedup                        |

| 5.11 | Effect of various halo widths on performance speedup                        |

| 5.12 | Effect of various block sizes on performance speedup                        |

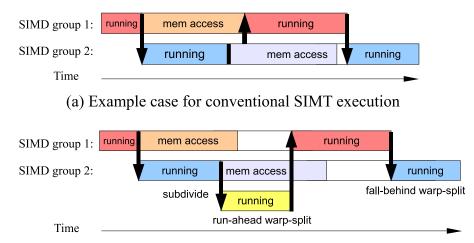

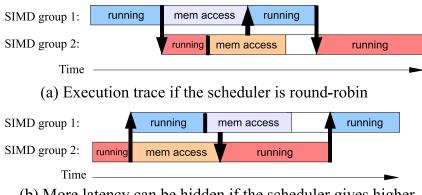

| 6.1  | Motivation of intra-warp latency hiding                                     |

| 6.2  | The baseline SIMD architecture                                              |

| 6.3  | Conventional mechanism to handle SIMD branch divergence                     |

| 6.4  | DWS upon branch divergence hides more latency                               |

| 6.5  | DWS upon branch divergence improves memory level parallelism 158            |

| 6.6  | An example of dynamic warp subdivision upon branch divergence 159           |

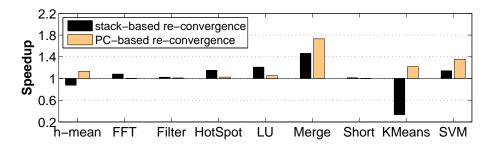

| 6.7  | Performance gained by dynamic warp subdivision upon branch divergence. 163  |

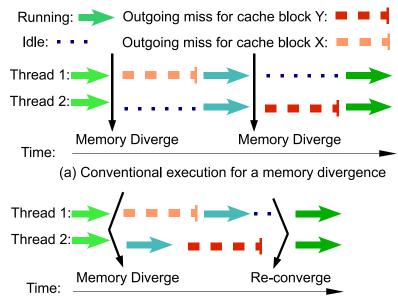

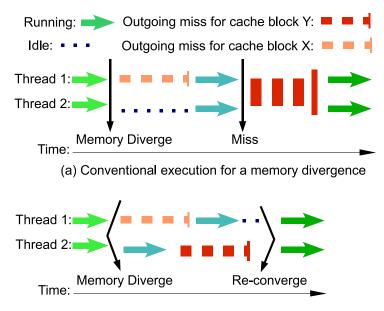

| 6.8  | DWS upon memory divergence reduces pipeline stalls and improve MLP. 165     |

| 6.9  | Dynamic warp subdivision upon memory divergence allows run-ahead threads  |

|------|---------------------------------------------------------------------------|

|      | to prefetch cache blocks for the fall-behind                              |

| 6.10 | Hazards of DWS upon memory divergence                                     |

| 6.11 | Speedups for DWS upon memory divergence alone                             |

| 6.12 | An example of dynamic warp subdivision upon memory divergence 172         |

| 6.13 | Comparing various DWS schemes                                             |

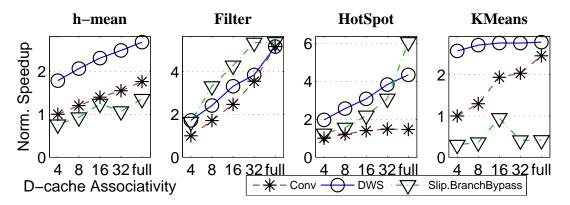

| 6.14 | Speedup of DWS vs. D-cache associativity                                  |

| 6.15 | Speedup of DWS vs. L2 lookup latency                                      |

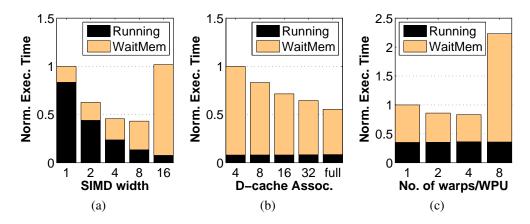

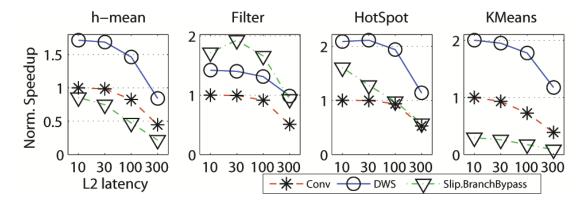

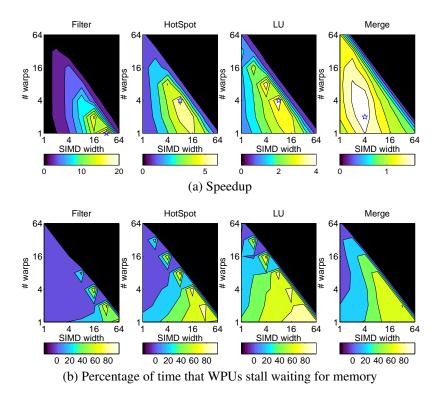

| 7.1  | Space exploration of various SIMD widths and multi-threading depths 185   |

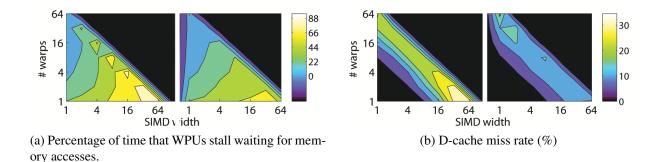

| 7.2  | Characterizations of various SIMD widths and multi-threading depths 186   |

| 7.3  | The baseline SIMD architecture                                            |

| 7.4  | The process of adapting a WPU's SIMD width and multi-threading depth      |

|      | to a particular data-parallel section of code                             |

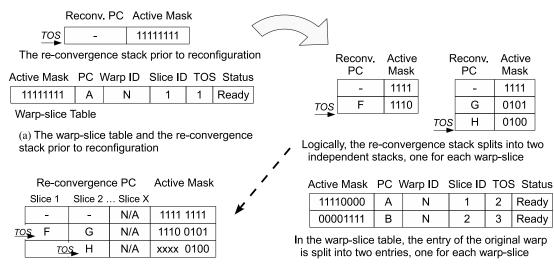

| 7.5  | The warp-slice table and the re-convergence stack before and after a warp |

|      | is split into two warp-slices                                             |

| 7.6  | Comparing different adaptation strategies                                 |

| 7.7  | Sensitivity study for convergence rate and interval length                |

| 7.8  | Speedups of Robust SIMD over various SIMD organizations                   |

| 7.9  | Robustness across various D-cache setups                                  |

| 7.10 | The impact of Robust SIMD on latency hiding and D-cache misses 217        |

| 8.1  | By giving higher scheduling priority to warps are likely to miss sooner,  |

|      | more MLP can be exploited than with a round-robin scheduler               |

# **List of Tables**

| 2.1 | Comparison with other simulators                                      |

|-----|-----------------------------------------------------------------------|

| 2.2 | MV5 Parameters                                                        |

| 3.1 | Default system configuration                                          |

| 3.2 | Simulated benchmarks with descriptions and input sizes                |

| 3.3 | Different partitioning and scheduling combinations                    |

| 4.1 | Default System Configuration                                          |

| 4.2 | Simulated benchmarks with descriptions and input sizes                |

| 5.1 | Architectural parameters for GeForce GTX 280                          |

| 5.2 | Benchmark parameters used in our performance modeling                 |

| 6.1 | Characterization of the frequency of branch divergence and SIMD cache |

|     | misses                                                                |

| 6.2 | Simulated benchmarks with descriptions and input sizes                |

| 6.3 | Hardware parameters used in studying Dynamic Warp Subdivision 155     |

| 7.1 | Hardware parameters used in studying Robust SIMD                      |

| 7.2 | Simulated benchmarks with descriptions and input sizes                |

# Chapter 1

# Introduction

### 1.1 Introduction to Chip Multi-Threading

The era of instruction level parallelism (ILP) and single processor performance scaling has ended: power constraints prevent clock cycles from increasing, and the point of diminishing return has reached for adding more transistors to explore ILP. We are now in the era of *Chip Multiprocessor* (CMP), where each chip typically consists of a number of simple cores on a single chip. Compared to single processors, CMPs generally have higher throughput since they better exploit data parallelism and task parallelism, both exist extensively in many emerging applications. Examples of such application domains include scientific computation, media processing, machine learning and data mining [1].

However, having multiple cores on a single chip leads to more communication and data movement, which in turn demands higher memory bandwidth. Even worse, the memory speed doubles only every six years, whereas the processor speed historically doubles every two years [2]. This inevitably leads to the *memory wall* where CMP pipelines often stall waiting for memory accesses.

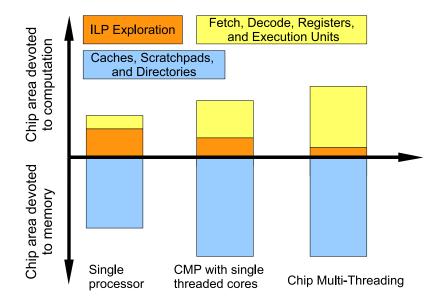

To increase throughput in spite of the increasing gap between processor speed and memory speed, each core in a CMP architecture can have multiple threads; this type of architecture is often named *Chip Multi-Threading* (CMT). Comparing to CMPs with single threaded cores, a CMT architecture has several advantages. First, CMTs allow threads with overlapping working sets to share the same cache, so that the on-chip storage can be utilized better. Second, CMTs increase pipeline utilization by overlapping the outgoing memory access of one thread with the computation of another thread on the same core. Third, by having more threads per storage, CMTs can exploit more data and task parallelism within the same area budget. Figure 1.1 summarizes the trend of shifting from single processors to CMT.

Figure 1.1: Trends for area breakdown of a chip. CMP and CMT devotes less area for ILP exploration and more area for register files and execute units to improve throughput. CMT multiply the number of threads per core to further increase throughput without significantly increasing storage area.

CMT commonly comes in the forms of Simultaneous Multi-Threading (SMT) [3] and Single Instruction Multiple Data (SIMD) [4]. SMT can fetch instructions from multiple independent threads in one cycle; each instruction can be fed to the appropriate execute unit if available. This increases the efficiency of the pipeline and improves utilization of execute units. Examples of SMT include Intel's Pentium IV [5], IBM's POWER 5 [6], and Sun's UltraSPARC T1 [7].

With SIMD architectures, a group of threads share the same instruction sequencer and they operate in lockstep. SIMD organizations amortize the area and power of fetch, decode, and issue logic across multiple processing units in order to maximize throughput for a given area and power budget. SIMD lockstep operation of multiple datapaths can be implemented with vector units, where the SIMD operation is explicit in the instruction set and a single thread operates on wide vector registers. SIMD lockstep can also be *implicit*, where each lane executes distinct threads that operate on scalar registers, but the threads progress in lockstep. The latter is also referred to by NVIDIA as *single instruction multiple threads* (SIMT). Examples of SIMD include Sun's Niagara [8], the Cell Broadband Engine (CBE) [9], Clearspeed's CSX600 [10], Cray [11], Tarantula [12], NVIDIA's Tesla [13] and Fermi [14], and Intel's Larrabee [15]. Academic researchers have also been exploring this design space and several prototypes have been produced, including Stanford's Imagine [16] or Merrimac [17].

CMT architectures—especially SIMD architectures—drastically increase the thread count per core. Therefore, they often subject to more intensive data movement and communication. We study the memory wall in the context of CMT in more details below.

### **1.2** The Memory Wall for Chip Multi-Threading

CMT architectures come with various types of memory system organizations. *Cache-based* memory systems provide a hierarchy of caches that are implicitly managed by a coherent protocol. Data is automatically fetched into caches or spilled into the memory according to

locality heuristics. On the other hand, *stream-based* memory systems require programmers to explicitly move data and specify which data to be stored closer to the execute units. The additional programming effort enables application specific optimizations.

Despite the variety of memory systems, we have been consistently observing that the number of threads per L1 storage has been increasing dramatically for CMT: Power 5 has two threads sharing a 32 KB D-cache; Niagara runs four threads over an 8 KB D-cache; and NVIDIA's GTX280 [18] can operate up to 32 warps each have 32 threads over a 16 KB scratchpad (officially referred to as the per-block shared memory (PBSM))! This reflects the fact that given a fixed area budget, more parallelism can be exploited by increasing the threads per storage ratio. However, the system has to be designed in a manageable and balanced way; the on-chip storage needs to be reduced to make room for more threads, but not to such an extent that the memory system easily gets thrashed (*i.e.*, frequent data movement to and from the memory resulted from severe contention). In other words, the more efficient data is managed, the more hardware threads can be accommodated on a single chip and the more throughput the architecture can produce.

Evidence has already shown that parallel architectures have already hit the memory wall: as Mckee et al. conducted [19] in 2004, commercial applications such as transaction processing workloads show 65% percent node idle times; scientific applications show 95% node idle times; much of this is due to memory bottlenecks. Therefore, efficient data management is critical for CMT to achieve better performance.

### **1.3** Challenges in CMT Data Management

The unique properties of CMT poses several new challenges for data management. First, not only the shared storage, but also the per-core private storage is contended for by multiple threads. The aggregate working set of all active threads on the same core has to fit in the L1 storage, otherwise the L1 storage may be overwhelmed and performance risks severe degradation. As a result, multi-threaded cores benefit from extensive data sharing among threads on the same core.

Second, communication latency among threads is no longer uniform; the overhead is much longer among threads on different cores than those on the same core. While threads on the same core can communicate by writing and reading from the per core L1 storage, data communication between threads on different cores has to go through the shared storage, and it may require several coherence messages. In other words, the set of all active threads can no longer be viewed as a group of homogeneous, independent entities; instead, they demonstrate heterogeneity and appropriately collocating threads leads to significantly less data communication between cores.

Third, highly multi-threaded cores are often in-order and they lack the ability to execute beyond pending memory instructions to hide memory latency. A conventional single processor devotes significant area to out-of-order execution and ILP exploration with the purpose of shortening the *latency of an individual thread*. It often comes with additional units such as rename registers, scoreboards, re-order buffer (ROB), and load store queues. On the other hand, multi-threaded cores aim at *leveraging the overall throughput* and therefore they devote more area for hardware thread contexts—such as the register files—and less for ILP exploration. However, little ILP exploration limits the ability hide memory access latency. In many CMT architectures, limited ILP exploration is compensated by *multi-threading*, the ability to switch to other threads when the current thread experiences long latency memory accesses. However, the effectiveness of multi-threading depends on various runtime dynamics and has not be well studied. We will discuss it in more detail in Chapter 6 and 7.

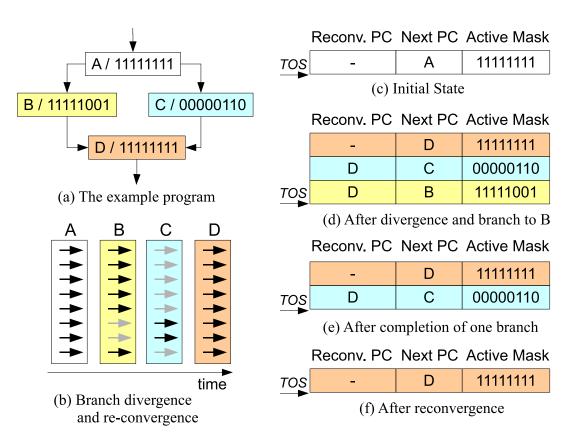

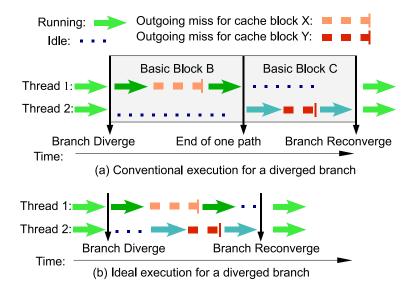

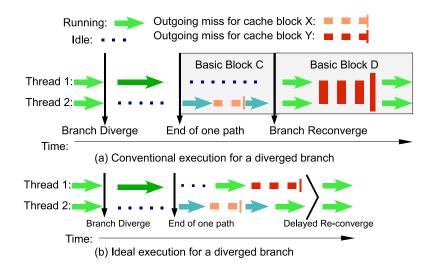

Finally, SIMD enforces threads to operate in lockstep, which may incur additional overhead when some threads have to wait for their peers to be ready. This often occurs in two scenarios. First, upon *branch divergence*, SIMD threads take different paths after a conditional branch. SIMD organizations have to execute one path of the branch at a time, with threads falling into the alternate path suspended. Second, upon *memory latency divergence*, SIMD threads experience different memory-reference latencies caused by cache misses or accessing different DRAM banks. Threads that operate in SIMD must wait until the last thread has its reference satisfied. In Chapter 6, we propose several ways to address the above issues.

### **1.4 Data Management for Multi-Threaded Cores**

Data management has been extensively studied for decades. We list general principles in conventional data management that have applied well to single processors and CMPs with single-threaded cores. We then discuss the new problems and opportunities posed by multi-threaded cores.

#### 1.4.1 Background

The general ways to cope with limited bandwidth and storage capacity are to either reduce or tolerate data movement and associated latencies. Such data management can occur in software (*i.e.* applications), middleware(*i.e.* compilers and run-time systems), and hardware (*i.e.* memory systems, interconnects, scheduling units, and the computation pipeline).

Data movement can be reduced by:

• Algorithmically modifying target applications to reduce data transfer. There are also application-specific methods to either organize data or restructure the computation so that data movement is minimized [20]. These techniques are not the focus of this dissertation.

- Wisely distributing data using compilers or run-time systems to increase data reuse and reduce data communication. Researchers have proposed various techniques to partition the data set in a way that maximizes spatial locality [21, 22, 23, 24, 25, 26, 27, 28, 29, 30]. There are also several techniques that attempt to map an individual thread closer to the data to be consumed [31, 32, 33, 34, 35, 36, 37, 38, 39]. Moreover, researchers have designed techniques to reduce contention of the shared cache by wisely selecting concurrent threads [40, 41, 42, 43] or partitioning the cache [44, 45, 46].

- Employing efficient data movement protocols or interconnects in the hardware. Architects have explored various cache organizations [47, 48], data replacement and communication strategies [49, 50, 51, 52], cache inclusion properties [53, 54], and various scalable coherence protocols [55, 56].

- Designing efficient storages to increase the amount of data they can accommodate. For example, caches can be compressed [57], and data from multiple cache lines can be collapsed into one line [58].

Latency in data movement can be tolerated with:

- Asynchronous data transfer such as direct memory-access (DMA). The DMA engine can read and write memory independently of the processing elements. Typically, programs specify the address and size of the data transfer, start the DMA engine, and continue with their execution while data is being transferred in parallel.

- Data prefetching, memory level parallelism, and latency hiding techniques. Researchers have proposed temporal and spatial streaming [59, 60, 61] to leverage the repetitive data access patterns in a CMP.

• Speculatively allowing a thread to run ahead beyond pending memory instructions and roll back if speculation fails [62]. Alternatively, speculative threads [63] can issue a stream of future memory references extracted from the original thread.

While many of the above techniques can still be applied to highly multi-threaded cores straightforwardly, some do not apply well due to the nature of simple cores (*e.g.* speculative execution). This dissertation proposes several solutions to address data distribution, task scheduling, and latency hiding in CMT. Moreover, CMT raises new topics such as the ability to trade abundant computing resources for less communication. The following subsections introduce each contribution.

#### **1.4.2 Uniform Data Distribution in Shared Cache**

The typical runtime system allocates data without considering how data distributes into cache sets in the shared cache. Overall, it is rare in single-threaded processors that contention over a few cache sets in the shared cache becomes the performance bottleneck. However, in the realm of multi-threaded cores, we found that even slight non-uniform data distribution caused by the run-time system can be magnified by the large thread count. This leads to severe contention on a few hot cache sets, which eventually becomes the bottleneck for performance scaling.

This phenomenon is particularly acute with stack allocation in common operating systems. Generally, a shared, inclusive cache can improve data sharing among cores; data in all upper level caches is replicated in the shared cache, therefore a different core can often reuse data directly in the shared cache instead of probing private caches of a remote core. However, the inclusion property also means that each cache set in the shared cache is contended for by all threads on the chip, which may reach hundreds or thousands in quantity. Current memory allocators align stack bases on page boundaries, which is accommodated by only a few cache sets. The conflict misses caused by such nonuniform allocation is not obvious when the thread count is small, however, it emerges as a source of severe conflict misses when there are a large number of actives threads all trying to allocate stack data.

In Chapter 4, we propose stack-base randomization that eliminates the major source of conflict misses for large numbers of threads. However, when capacity becomes a limitation for the directory or last-level cache, this is not sufficient. We then propose non-inclusive, semi-coherent cache organization (NISC) that allows private data to be noninclusive in the shared cache. Our data-parallel benchmarks show that conventional systems cannot scale beyond 8 cores, while our techniques allow performance to scale to at least 32 cores for most benchmarks. At 8 cores, stack randomization provides a mean speedup of 1.2X, but stack randomization with 32 cores gives a speedup of 2.7X over the best baseline configuration. Comparing to conventional performance with a 2 MB shared cache, our technique achieves similar performance with a 256 KB shared cache, suggesting shared caches may be typically overprovisioned. When very limited Last Level Cache (LLC) resources are available, NISC can further improve system performance by 1.8X. This work was published in [64].

#### **1.4.3** Fine grained, Inter-Thread Data Sharing

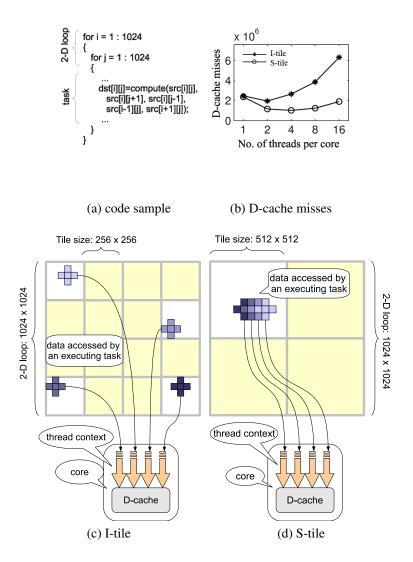

Even after shared cache contention is mitigated by uniform data distribution, the first level data caches are still contended for by multiple threads that collocate on the same core. Therefore, the thread schedulers must try to minimize cache contention among threads sharing the same D-cache. While this has been studied for concurrent threads with *disjoint* working sets, the problem has not been addressed for multi-threaded data-parallel workloads in which threads can be scheduled or constructed to improve inter-thread cache sharing. Chapter 3 proposes *symbiotic affinity scheduling (SAS)* algorithm in which work

is first partitioned according to the number of cores (i.e., the number of caches), and these partitions are then subdivided and scheduled among each core's available thread contexts so that threads sharing a core operate on neighboring elements to maximize cache locality.

We demonstrate this concept with a series of data-parallel benchmarks. Simulations achieve an average speedup of  $1.69 \times$  and 36% energy savings over conventional scheduling techniques that are oblivious to whether threads share a cache. Even compared to an approach that extends oblivious scheduling to ensure that the sum of the threads' working sets fits in the cache, symbiotic affinity scheduling is able to exploit greater temporal locality and provide 30% performance gains on average. Symbiosis also outperforms adaptive contention reduction techniques by 17%. This work was published in [65].

#### **1.4.4 Replicating Computation to Reduce Communication**

*Iterative stencil loops* (ISL) [66] are widely used in image processing, data mining, and physical simulations. ISLs usually operate on multi-dimensional arrays, with each element computed as a function of some neighboring elements. These neighbors comprise the *stencil*. Multiple iterations across the array are usually required to achieve convergence and/or to simulate multiple time steps. Tiling [25, 30] is often used to partition the stencil loops among multiple processing elements (PEs) for parallel execution. It partitions a nested parallel *for* loop into continuous blocks and assign each block to an individual thread. Between two iterations, a tile needs to exchange its bordering data, or *halo*, with tiles on different PEs. Such communication is expensive. In addition, synchronization is often used to signal the completion of halo exchanges. Both communication and synchronization may incur significant overhead on parallel architectures with shared memory. This is especially true in the case of graphics processors (GPUs), which do not preserve the state of the per-core L1 storage across global synchronization. Techniques to enhance locality–including the

techniques described above—fail to capture the coarse-grained locality across iterations. To improve inter-iteration locality and reduce synchronization overheads, ghost zones can be created to replicate stencil operations, reduce communication and synchronization costs, by redundantly computing halos on multiple PEs. However, the selection of the optimal ghost zone size depends on the characteristics of both the architecture and the application.

To automate the process of optimizing the ghost zone size, Chapter 5 establishes a performance model for NVIDIA's Tesla architecture [13]. The performance model can be used to automatically select the ghost zone size that performs best. The modeling is validated by four diverse ISL applications, for which the predicted ghost zone configurations are able to achieve a speedup no less than 95% of the optimal speedup. This work was published in [67].

#### **1.4.5** Overcoming SIMD Constraints for Better Latency Hiding

Even if data locality is extensively exploited, throughput can still be undermined when a set of threads operating in lockstep (a warp) are stalled due to long latency memory accesses. The wider SIMD it is, the more threads will have to wait when a thread misses the cache. Multi-threading can hide latencies by interleaving the execution of multiple warps, but deep multi-threading using many warps dramatically increases the cost of the register files (multi-threading depth  $\times$  SIMD width), and increased cache contention can make performance worse. Instead, intra-warp latency hiding should first be exploited. This allows threads that are ready but stalled by SIMD restrictions to use these idle cycles and reduces the need for multi-threading among warps. Chapter 6 introduces *dynamic warp subdivision* (DWS), which allows a single warp to occupy more than one slot in the scheduler without requiring extra register file space. Independent scheduling entities allow divergent branch paths to interleave their execution, and allow threads that hit to run ahead. The result is

improved latency hiding and memory level parallelism (MLP) (*i.e.* more memory accesses that overlap with each other in time).

We evaluate the technique on a coherent cache hierarchy with private L1 caches and a shared L2 cache. With an area overhead of less than 1%, experiments with eight dataparallel benchmarks show our technique improves performance on average by 1.7X. This work was published in [68].

#### 1.4.6 Dynamically Adapted SIMD for Robust Performance

Conventional SIMD organizations embed a fixed SIMD width and multi-threading depth. However, a static organization may not perform well for all applications or when the underlying memory system resizes itself for power saving or error resilience purposes. In fact, our experiments show that the best SIMD width and multi-threading depth depends heavily on the underlying memory system as well as the application.

This challenges designers in identifying the best combination of SIMD width and depth. Several tradeoffs are involved in determining the best combination of several parameters: wider SIMD may enable more throughput, but is also more likely to waste cycles due to divergent branches or memory accesses; deeper multi-threading may overlap more computation with memory accesses, but it is also likely to increase L1 contention due to multiplication of thread count, especially when combined with wide SIMD. Even with dynamic warp subdivision, threads may still incur severe cache contention for some applications.

Chapter 7 proposes *Robust SIMD*, which dynamically optimizes and reconfigures SIMD width and multi-threading depth according to runtime performance feedback. Robust SIMD can also trade wider SIMD for deeper multi-threading by splitting a wider SIMD group into multiple narrower SIMD groups. Compared to the performance generated by running every benchmark on its individually preferred SIMD organization, the *same* Robust SIMD

organization performs similarly—sometimes even better due to phase adaptation—and outperforms the best fixed SIMD organization by 17%. Our experiments also show that even with dynamic warp subdivision (DWS), a fixed SIMD organization that performs best with 32 KB D-caches can only yield less than 50% of the optimal performance when D-cache capacities reduce to 16 KB. By combining Robust SIMD and DWS, the proposed organization achieves 99% of the optimal performance persistently. In fact, it achieves 97% of the performance achievable by a conventional organization with D-caches that double in size. Overall, Robust SIMD's area overhead is less than 1%. This work was submitted to MICRO-43 [69].

### **1.5** Dissertation Organization

The rest of the dissertation is organized as follows: Chapter 2 presents the simulation tool we built to conduct our research. Chapter 3 introduces a technique to improve inter-thread spatial and temporal locality for multi-threaded cores. Chapter 4 demonstrates the need to distribute data uniformly to reduce shared cache contention. Chapter 5 establishes an analytical performance model to improve the effectiveness of the ghost zone technique which replicates computation to reduce communication. Chapter 6 proposes dynamic warp subdivision for SIMD architecture to address SIMD constraints and better latency hiding. Chapter 7 describes a reconfigurable SIMD organization that yields robust performance across applications and various memory configurations. Finally, Chapter 8 summarizes the lessons learned and proposes potential research extensions.

# Chapter 2

# Simulating General Purpose Multi-Threaded Cores

### 2.1 Introduction

There is an increasing demand for commodity computer systems to host modern applications that exhibit diverging characteristics. While many latency-oriented workloads such as compilers (e.g. GCC) and compressors (e.g. bzip2) still prefer sequential execution, many throughput-oriented workloads are transitioning to parallel execution. They include media processing, scientific computing, physics simulation, and data mining. Workloads can also be compute-intensive or data-intensive. Moreover, different types of workloads can execute simultaneously over the same system. Each workload may demonstrate different instruction-level (ILP), data-level (DLP), thread-level (TLP), and memory-level parallelism (MLP), which challenges future architectures to optimize for less execution time and more power- and area- efficiency.

Several architecture designs have been proposed to address the challenges posed by

heterogeneous workloads. In addition to conventional, general purpose processors, special purpose processors have been built for particular application domains (e.g. Graphics Processors (GPUs) [70], ParallAX [71], Anton [72]). However, the physical separation of the processors incurs significant latency in communication and data transfers. The lack of shared resources may also lead to power- and area- inefficiency. These hardware disadvantages, when exposed to the programmers, complicate coding effort and lead to poor productivity. Alternatively, the integration among heterogeneous processing elements can be made more efficient given a general purpose chip multiprocessor (CMP), where multiple cores reside on the same die and operate over a shared memory. General purpose CMP products have been developed by both academic and industrial groups. They include MIT's Raw [73], Compaq's Piranha [74], Sun's Niagara [8], IBM's Power5 [6], Cell [9], and Intel's Larrabee [15]. While most of these architectures present homogeneous cores, recent studies show that heterogeneous multicore architectures provide significant power and performance advantages [75, 76].

The two extremes over the spectrum of heterogeneous cores are out-of-order (OOO) cores and simple, in-order (IO) cores. While OOO cores dedicate more area to leverage ILP, IO cores remain simple and the equivalent area budget can host more cores, leveraging DLP and TLP. OOO cores and IO cores correspond to the two extremes of workloads — latency-critical and throughput-critical workloads, respectively. These two types of cores have been working complimentarily on traditional computer systems with separate CPU and GPU. Since the release of programmable GPUs [77], many researchers have found that many applications that used to execute sequentially on the CPU can actually benefit from parallel execution on the GPU. Recently, NVIDIA has released CUDA [78] that performs both graphics-specific tasks and general purpose computing. As the more general purpose applications benefit from off-loading throughput-oriented computation to GPU cores, merging the latency oriented OOO cores with the throughput oriented IO cores

can lead to more efficient inter-core communication, better area utilization, and lower energy consumption. AMD's Fusion [79], for example, targets integration of CPU and GPU, presenting a heterogeneous multicore design with additional graphics-purposed units. This leads to a large design space: cores may have different number of hardware thread contexts, SIMD (Single Instruction, Multiple Data) width; caches can present different hierarchies, and one cache can be private or shared among multiple cores; the on-chip network (OCN) may exhibit different topologies; and the coherence protocol has several variations as well.

In order to explore this large design space, a conveniently reconfigurable multicore simulator is needed. Despite existing multicore simulators (SMTSIM [80], Sesc [81], Simics [82], SimFlex [83]), none of them provide object-oriented modules that can be easily reconfigured. In addition, the functionality of the modules are largely bound to the physical layouts that connect the units. We build an easily reconfigurable, modularized multicore simulator named MV5 that targets at large-scale architectures with heterogeneous settings. MV5 is based upon M5 [84], an event driven simulator originally designed for a network of processors. It includes a set of different cores including OOO, SMT, IO, SIMD, and cores with several SIMD groups. Caches may have different sizes, associativity, and banking. Both snoop-based and directory-based coherence protocols (MSI and MESI) are available. Moreover, caches can be organized into various hierarchical layouts, and we have experimented with up to three levels of caches. In addition, MV5 provides point-to-point OCNs that include configurable 2-D meshes. The OCN template can be easily extended to accommodate other topologies such as torus and fat-trees as well.

### 2.2 Summary of Available General Purpose Simulators

A number of simulators have been developed to simulate various architectures. However, they are all limited in their capability to simulate large-scale CMPs with tens or hundreds of

| Features                   | MV5/M5                | SimFlex               | Sesc         | Simics/Gems/Garnet      |

|----------------------------|-----------------------|-----------------------|--------------|-------------------------|

| Full-system Simualtion     | √(M5)                 | $\checkmark$          | ×            | $\checkmark$            |

| System-call Emulation      | √(M5)                 | ×                     | $\checkmark$ | ×                       |

| I/O disk                   | √ (M5)                | ×                     | ×            | ×                       |

| Ethernet                   | √ (M5)                |                       | ×            |                         |

| ISA                        | various (M5)          | Sparc                 | Mips         | various                 |

| Emulated thread API        | √(MV5)                | NA                    | $\checkmark$ | NA                      |

| Category                   | Event-driven (M5)     | Cycle-driven          | Event-driven | Event- and Cycle-driven |

| IO core                    | √ (M5)                |                       | ×            |                         |

| Multithreaded core         | √ (MV5)               | ×                     | ×            |                         |

| OOO core                   | √ (M5)                |                       | $\checkmark$ |                         |

| SIMD core                  | √ (MV5)               | ×                     | ×            | ×                       |

| Cache Hierarchy            | Configurable (M5)     | Private L1, Shared L2 | Configurable | Configurable            |

| Coherence                  | Snoop/Directory (MV5) | Snoop/Directory       | Snoop        | Directory/Snoop         |

| Bus                        | √ (M5)                |                       | $\checkmark$ |                         |

| 2-D Mesh                   | √ (MV5)               | ×                     | $\checkmark$ |                         |

| Hypercube                  | ×                     | ×                     | $\checkmark$ | ×                       |

| hardware thread-management | √ (MV5)               | ×                     | ×            | ×                       |

| stream-buffer              | √ (MV5)               | ×                     | ×            | ×                       |

Table 2.1: Comparison with other simulators.

cores connected through a point-to-point OCN with directory-based cache coherence. Two well-known simulators that model single OOO cores and SMT cores are SimpleScalar [85] and SMTSIM [80], respectively. As modern architectures employ chip multiprocessors (CMPs), several other simulators have been released. They include PTLsim[86], Sesc [81], Simics [82], Gems [87], and SimFlex [83]. All of them provide limited types of cores: IO cores are not present on SMTSIM, PTLsim, and Sesc. SIMD cores are not modeled on any of the these simulators. OCN is not provided in PTLsim and SimFlex. Directory-based coherence is not available for PTLsim and Sesc. Simics can work with Gems to combine multiple core modules with a configurable cache hierarchy. More recently, Garnet [88] has been released to support OCN for Gems [87]. Nevertheless, Simics does not support system-call emulation, which is especially useful when a new hardware feature requires additional run-time library or middleware to interact it with the benchmarks. Table 2.1 summarizes the above comparison.

The MV5 simulator aims at exploring the large design space of future heterogeneous

CMPs with integrated CPU and GPU functionality. We pick M5 as our base simulator because of its well-designed modularity, which leads to convenience in both system reconfiguration and module extension. More importantly, M5 provides an integrated infrastructure from cores and caches to I/O devices and network. It supports both full-system simulation and system-call emulation. Finally, M5 provides a clean interface for debugging, checkpointing, fast-forwarding, and statistics. MV5 inherits the integrity, modularity, and flexibility from M5, and it incorporates essential modules that enable simulations for large-scale heterogeneous CMPs.

## 2.3 The MV5 Simulator

MV5 inherits the modular, configurable simulation environment from M5, which was originally designed to study I/O bandwidth for a network of processors. Modules' detailed functionalities are programmed in C++ and their parameters are encapsulated by high level python classes for easy reconfiguration. MV5 adds to M5 with several components which are necessary for modeling multicore architectures. MV5 also provide power and area modeling. In order to assist architects to efficiently explore the gigantic design space and organize the experiment results, an interactive batch system is developed and can operate with a cluster of machines.

#### **2.3.1** Modules and their Extendability

Since M5 was originally designed to study I/O bandwidth for a network of processors, it lacks several components which are necessary for modeling a multicore system. The missing components that are added in MV5 include:

1. Point-to-point OCNs. A large-scale CMP need a distributed, point-to-point OCN

to lower communication overhead and mitigate the increasing bandwidth demand. MV5 provides a template for various OCN options. An OCN is constructed by a set of interconnected routers with a particular topology and a specific routing policy. Deadlock is guaranteed by a correct routing policy. Routers are modeled with receiver buffering and bi-directional links. Two latency models are provided for store-forward and worm-hole routing. Using this OCN template, MV5 builds a 2-D mesh with X-Y routing. The 2-D mesh is configured according a file that depicts the layout of the mesh and which unit connects to which router in an graphical way. The OCN template can be easily extended to other topologies given the corresponding routing policy.

- 2. Directory-based coherence. Snooping is not available on a distributed OCN and thus cache coherence has to be directory based. MV5 inherits Directory-based caches from default caches in M5 and provides a template for various directory entries and coherence protocols. As a result, coherence handlers form separate modules and are isolated from the cache's basic functionalities. Each coherence protocol presents two sets of coherence handlers describing the block state transition diagram (BSTD) and the directory state transition diagram (DSTD), respectively. Coherence among multiple caches is constructed jointly by their BSTDs and the DSTD of their shared lower level cache. In turn, each cache interfaces with two coherence protocols: its BSTD interfaces with a lower level cache, and its DSTD interfaces with multiple upper level caches. Using this template for coherent caches, we build two inclusive coherence protocols, MSI and MESI.

- 3. Caches with multiple banks or multiple ports. A cache shared by multiple cores or multiple thread contexts often have multiple banks or multiple ports to meet the bandwidth demand. Users can still choose from various replacement policies.

- 4. Multi-threaded in-order cores. Data-intensive workloads have frequent memory accesses and may experience frequent cache misses as well. Memory level parallelism (MLP) is able to hide the memory latency by allowing multiple outstanding memory requests and enabling subsequent, independent instructions to continue execution. While out-of-order execution lead to MLP naturally, in-order cores may switch among the instruction streams from multiple hardware thread contexts to achieve MLP. The immediate hardware context switch involves no more than switching to another register file, as modern GPU cores do [70].

- 5. SIMD cores. Many data-parallel workloads can achieve more throughput from SIMD execution. SIMD has been widely employed by GPUs and the Cell. Traditionally, SIMD is provided in the form of vectorization, which imposes coding complexities when programmers are confronted with divergent branches and address alignment. MV5 simulate a different form of SIMD in which multiple hardware thread contexts form a SIMD group with a set of scalar data-paths operating under a common instruction sequencer, such as the Illiac-IV or modern GPUs, where a non-vectorizing compiler generates SPMD code. It provides simplicity in both hardware implementation and user programming, and it allows threads to have independent control flows. Upon branch divergence, the hardware records in a table about threads' diverged PCs and continues to execute the subgroup of threads with the same PC until they reach a convergence point. At this time, the remaining threads' execution will be continued. Because of the lack of compiler support, we annotate part of the benchmarks that performs data-parallel execution with instructions that signal convergence points. To leverage MLP, hardware thread contexts can statically form multiple SIMD groups and the core can switch among them upon memory accesses.

- 6. Threading API for system-call emulation. Because system-call emulation does not

provide a fully functional operating system, API calls to create threads over existing operating systems do not work properly, preventing simulation for multithreaded workloads. We implemented a set of threading API calls that include thread creation, join, and termination. Together with M5's existing synchronization API calls such as lock and barrier, they enable simulations for multi-threaded workloads with only minimum changes to the original code.

All the above modules are object-oriented. Each module isolates their external interfaces from their internal functional details. The standardized object interfaces allows object interchangeability: cores can be replaced by another type, coherence protocols can be switched from MSI to MESI, and a 2-D mesh can be substituted by a crossbar conveniently. Moreover, because an object fully encapsulate a component's state, it is easily replicated to form large-scale systems. We have shared the MV5 modules with the M5 community and will work to further integrate them with M5. Our modules have been used by researchers in University of California, San Diego and University of Hertfordshire.

#### 2.3.2 Latency, Power, and Area Modeling and Validation

MV5 models cache latency using Cacti [89]. Pullini *et al.* provide the basis for our interconnect latency modeling [90]. Users can set a core's clock frequency. The instructionsper-cycle (IPC) of an in-order core is assumed to be one except for memory references, which are modeled faithfully through the memory hierarchy (although we do not model memory controller reordering effects). Cores switch SIMT groups in zero cycles upon a cache access.

Energy is modeled in four parts. We use Cacti4.2 [89] to calculate both the dynamic energy for reads and writes as well as the leakage power of the caches. We estimate the energy consumption of the cores using Wattch [91]. The pipeline energy is divided into

seven parts including fetch and decode, integer ALUs, floating point ALUs, register files, result bus, clock and leakage. Dynamic energy is accumulated each time a unit is accessed. The crossbar's switches and routers are modeled after the work of Pullini et al. [90], and we assume the physical memory consumes 220 nJ per access [92]. We neglect refresh power.

To have realistic area esitmates, we measure the sizes of different functional units in an AMD Opteron processor in 130nm technology from a publicly available die photo. We do not account for about 30% of the total area, which is dedicated to x86-specific circuites. We scaled the functional unit area to 65nm with a 0.7 scaling factor per generation. Final area estimates are calculated from their constituent units. We derive the L1 cache sizes from the die photo as well, and assume a 11  $mm^2/MB$  area overhead for L2 caches.

#### **2.3.3** System Reconfigurations and Data Collections

MV5 adopts M5's flexibility in reconfiguring various architectures. A Python script sets up a system by replicating and instantiating Python objects of different types and connecting them through ports. Objects may have different parameters even if they are of the same type. The ability to interchange different object types and different object parameters enables convenient heterogeneous settings. After the system is instantiated, the Python script starts the simulation with appointed benchmark binaries. No recompilation is required after system reconfiguration. Section 2.4 lists the major parameters for major modules.

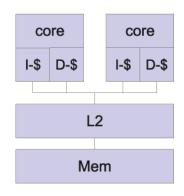

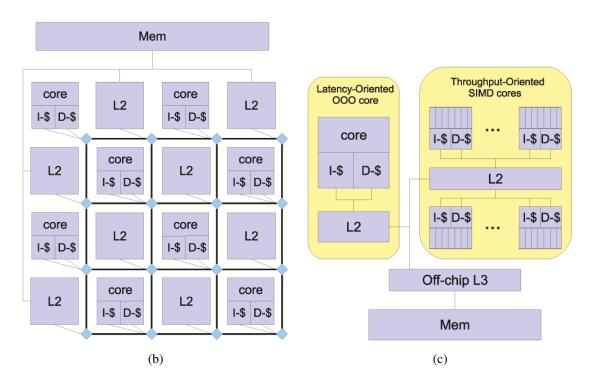

Figure 2.1 illustrates three examples of system configuration. Figure 2.1a is a dual core architecture with two homogeneous cores and they share the same L2 cache through a bus. Figure 2.1b shows a larger scale multicore architecture with eight IO cores they share a distributed L2 with eight banks through a 2-D mesh. Figure 2.1c demonstrates a heterogeneous multicore system with a latency-oriented OOO core, and a group of throughput oriented SIMD cores. The memory system contains two levels of on-chip caches and an

Figure 2.1: Various system configurations: (a) dual core; (b) tiled cores; (c) heterogeneous cores.

off-chip L3 cache.

M5 declares its own counter types for statistical analysis. Various counters are provided in the form of scalars, vectors, distributions, averages, and formulas. All the counters have names and brief descriptions, and their values will be written to an output file upon termination of the simulation. MV5 embeds counters into each extended modules and users are able to add additional counters as well.

#### 2.3.4 Manageable, Interactive Design Space Exploration

The design space of heterogeneous multicore architectures is already huge, let alone an architecture that integrate CPU and GPU with additional special purposed units dedicated to the graphics pipeline. For example with nine benchmarks, thousands of simulations are necessary only to explore various combinations of five different cache sizes and five different associativities for both private and shared caches.

MV5 scales the architects' ability to explore the gigantic design space of heterogeneous multicore architectures by using an interactive Python program to systematically manage the explosive number of simulation tasks. The program interacts with MV5's Python script and it performs the following tasks:

*Creating batches of simulation tasks.* By interpreting a user-provided description file listing the ranges of different parameters to explore, MV5 lists all the combinations of different parameter ranges and registers the batch of simulation tasks.

*Monitoring and Executing simulation tasks in parallel.* MV5 can operate over a cluster of machines. A server program records all the jobs and their status (e.g. pending, running, suspended, finished, failed, etc). Client programs running on the cluster of machines fetch simulation tasks and execute them in parallel. Users can interactively query the status of one or more simulation tasks by providing a task ID or a substring of the tasks' command line. Upon an aborted simulation, the server is notified and users can restart simulation later after debugging. MV5 can also interact with a machine cluster using PBS (Portable Batch System) — a queuing system for a networked multi-platform UNIX environments [93].

*Data collection and post-processing.* Although all counter values are written to the output file after each simulation, further statistical analysis are necessary to aggregate the detailed counter values from similar units. MV5 enables the user to formulate post-processing in a description file, which MV5 then uses to interpret and aggregate the shear amount of data resulted from a single simulation. This data collection and post-processing process can also be distributed to the cluster machines and execute in parallel.

*Tabular and graphical analysis.* To help architects analyze data generated by the large number of experiments, MV5 provides analytical tools that grab requested data from the ocean of experimental results and organize data into tables or directly plot them using gnuplot [94]. As a result, users only have to provide MV5 with a description file that defines the groups of experiments to compare, the scaling of parameters and the data values that interest them — completely bypassing the tedious work of data entry.

# 2.4 Major MV5 Simulation Parameters

| Cores  | clock frequency                                                           |  |  |  |  |

|--------|---------------------------------------------------------------------------|--|--|--|--|

|        | number of hardware thread contexts                                        |  |  |  |  |

|        | enabling latency hiding by switching thread contexts upon memory accesses |  |  |  |  |

|        | context switch latency                                                    |  |  |  |  |

|        | SIMD warp size                                                            |  |  |  |  |

| Caches | coherence protocol                                                        |  |  |  |  |

|        | size                                                                      |  |  |  |  |

|        | line size                                                                 |  |  |  |  |

|        | associativity                                                             |  |  |  |  |

|        | replacement policy                                                        |  |  |  |  |

|        | lookup latency                                                            |  |  |  |  |

|        | prefetch policy                                                           |  |  |  |  |

|        | number of banks                                                           |  |  |  |  |

|        | per-bank queue size                                                       |  |  |  |  |

|        | number of ports                                                           |  |  |  |  |

|        | number of MSHRs                                                           |  |  |  |  |

|        | maximum number of outstanding request in each MSHR                        |  |  |  |  |

| OCN    | clock frequency                                                           |  |  |  |  |

|        | routing latency                                                           |  |  |  |  |

|        | topology                                                                  |  |  |  |  |

|        | buffer size                                                               |  |  |  |  |

|        | bandwidth                                                                 |  |  |  |  |

|        | forwarding scheme (store-forward or wormhole)                             |  |  |  |  |

| Bus    | clock frequency                                                           |  |  |  |  |

|        | bandwidth                                                                 |  |  |  |  |

| Memory | access latency                                                            |  |  |  |  |

|        | size                                                                      |  |  |  |  |

| Misc   | cache hierarchies                                                         |  |  |  |  |

|        | number of cores                                                           |  |  |  |  |

|        | connection topology among cores and caches                                |  |  |  |  |

Table 2.2: MV5 Parameters

# 2.5 Conclusion

We conclude several lessons during the implementation of the MV5 simulator and the exploration of the design space. They are critical in managing a large amount of simulations with various configurations.

- Modularity is critical to explore a large design space. An object-oriented, modularized structure is the key to isolate units, replicate them, or extend their functionalities. Modularity also leads to the flexibility in connecting different units. This is especially useful when a large design space needs to be explored with various mutations of similar units connected in different ways.

- Systematic management of a large number of simulations enhances productivity significantly. It integrates creating simulation tasks in batches, launching simulations to a cluster of machines and monitoring their status, adjusting the priorities of different simulations, collecting experimental results, post-processing data, and intuitive graphical analysis. This complete toolchain relieves researchers from data entry and expedites design space exploration and the process of gaining insights.

- Incremental development helps identify and eliminate bugs at early stages. It also improves modeling quality by consolidating the bricks that eventually form a large simulator.

- Instruction traces with register values and load/store addresses help developers to find clues in debugging a large-scale simulator. For example, developers may find inconsistent values between a load and a previous store, he or she can then further investigate traces for the coherence caches to find out what is wrong.

- It is worthwhile to duplicate pieces of code if this leads to better code-readability

and modularity. In MV5, coherence protocols are programmed as separate finite state machines and each transition is described by a distinct class. Although multiple transitions may appear similar, separating them leads to a clean description of the protocol and we are able to easily extend the protocol from MSI to MESI.

# Chapter 3

# **Exploiting Inter-thread Spatial and Temporal Locality**

# 3.1 Introduction