## **Thermal Modeling and Management of Microprocessors**

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science University of Virginia

In Partial Fulfillment

of the requirements for the Degree

Doctor of Philosophy

**Computer Science**

by

### Karthik Sankaranarayanan

May 2009

### **Approvals**

This dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

**Computer Science**

S.K -~

Karthik Sankaranarayanan

Approved:

Kevin Skadron (Advisor)

nica

Mircea R. Stan (Co-Advisor)

John Lach

Jun W. Ide

Jack W. Davidson (Chair)

0

James P. Cohoon

Accepted by the School of Engineering and Applied Science:

James H. Aylor (Dean)

April 2009

### Abstract

The most recent, and arguably one of the most difficult obstacles to the exponential growth in transistor density predicted by Moore's Law is that of removing the large amount of heat generated within the tiny area of a microprocessor. The exponential increase in power density and its direct relation to on-chip temperature have, in recent processors, led to very high cooling costs. Since temperature also has an exponential effect on lifetime reliability and leakage power, it has become a first-class design constraint in microprocessor development akin to performance.

This dissertation describes work to address the temperature challenge from the perspective of the architecture of the microprocessor. It proposes both the infrastructure to model the problem and several mechanisms that form part of the solution. This research describes HotSpot, an efficient and extensible microarchitectural thermal modeling tool that is used to guide the design and evaluation of various thermal management techniques. It presents several Dynamic Thermal Management (DTM) schemes that distribute heat both over time and space by controlling the level of computational activity. Processor temperature is not only a function of the power density but also the placement and adjacency of hot and cold functional blocks, determined by the floorplan of the microprocessor. Hence, this dissertation also explores various thermally mitigating placement choices available within a single core and across multiple cores of a microprocessor. It does so through the development of HotFloorplan, a thermally-aware microarchitectural floorplanner. Finally, through an analytical framework, this research also focuses on the spatial (size) granularity at which thermal management is important. If regions of very high power density are small enough, they do not cause hot spots. The granularity study quantifies this relationship and illustrates it using three different microarchitectural examples.

### Acknowledgments

This dissertation would not have been possible without the help of so many people. I am greatly indebted to my advisor Professor Kevin Skadron for his guidance. His approach of giving me complete freedom has made me grow as an individual and take ownership of the research problem. He pushed me when he needed to and that is the reason I have reached this point of completion. A significant portion of the text of the second and third chapters of this dissertation arose out of a paper in which my advisor played the primary role in writing. I am also thankful to him for his flexibility in letting me work remotely so I could be with my wife and for his continued financial support all these years. This work was supported in part by the National Science Foundation under grant nos. CCR-0105626, CCR-0133634, EIA-0224434, CCF-0429765, CSR-0509245, CRI-0551630 and MIP-9703440, an Army Research Office grant no. W911NF-04-1-0288, an Excellence Award from the University of Virginia Fund for Excellence in Science and Technology, a grant from Intel MRL and an IBM Research Faculty Partnership Award.

I am deeply grateful to my co-advisor Professor Mircea Stan for the countless hours of patient brainstorming. He helped me in grasping the circuit-level concepts right from the days when I was a student in his VLSI class. My sincere thanks to the members of my committee — apart from my advisor and co-advisor, Professors Jack Davidson, John Lach and James Cohoon, for their patient reading of my dissertation, considerate understanding of the change of scope of this work, will-ingness to give four crucial extra days for the submission of the dissertation and their constructive feedback that has helped in the shaping of this document. I am also thankful to Professor Hossein Haj-Hariri for teaching me the basics of analytical solutions of the heat equation and Professor Robert Ribando for directing me to the right person to ask such questions. I would also like to

express my thanks to Dr. Norman Jouppi for the discussion during his visit to UVA, which formed the origin of the L2 cache-bank insertion study. I have learnt much from my mentors during the two summer internships — Dr. Luiz Barroso and Dr. Scott McFarling and would like to thank them for the opportunity. I would also like to express my sincere thanks to all my professors and teachers, present and past, who have imparted the gift of knowledge in me. Many thanks to Intel and Dr. Daryl Nelson for the job offer and the patient wait. In these times of economic uncertainty, this security has helped me focus on my dissertation.

I cannot thank my colleague Wei Huang enough for all his help. We have collaborated very closely and it is impossible to list the number of times I have benefited from Wei's help in the form of explanations, experiments, feedback, reviews, code, text, figures *etc.* He is the primary contributor to the HotSpot thermal model. I would also like to convey my earnest appreciation for the contributions from Siva Velusamy, David Tarjan and Yingmin Li to the third chapter of this dissertation. Siva made important contributions to the implementation and evaluation of the DTM schemes. David calibrated the power model and Yingmin modified the performance model to mimic an Alpha-like architecture. I would also like to acknowledge the inputs of Siva to the modeling of the extra wire delay in the fourth chapter. I am thankful to Michele Co and Jeremy Sheaffer for their proposal and dissertation documents and presentations which served as samples to base mine upon. Many thanks to David Coppit and John Regehr for putting together a latex dissertation template conforming to the standards of UVA SEAS. I would like to express my thanks to my colleagues Michael Boyer, David Tarjan, Jiyauan Meng, Shuai Che, Eric Humenay and Yingmin Li for helping me work remotely by switching on my computer when it went down. Michael and David especially helped me by taking care of my office space and by plugging in my computer to the UPS.

As an international student in a foreign country, my graduate life in UVA has benefited immensely from the help of many graduate students who have helped me in getting established during my initial years in Charlottesville. I would like to thank them all for all their help including the many rides and errands.

I have been fortunate to have made and drawn support from many close friends formed during

my stay at UVA, during the CEG days and during the high school days at Madurai. Many of them have become my extended family and I am extremely grateful for all their wishes and support. Among them, as my co-travellers in the Ph.D. journey, Ram, Sundar, Easwar and Lakshmi have been my sounding boards offering encouragement and sharing insights innumerable times. I am deeply indebted to them.

I would not be here without my parents. Their constant belief in me, complete independence for my actions and respect for my choices have made me who I am. My heartfelt thanks to them for their love, blessings and prayers. I am thankful for my two little sisters' wishes and untiring confidence in me. Preethi has been constantly cheering me since my middle school. Deepu has brought many laughs by sharing her youthful exploits.

Many friends of our family have practically become part of our own over the years. I am thankful for all their wishes and blessings. I would also like to thank my relatives who took a lot of interest in my progress for their support.

I have received invaluable guidance from two mentors in my personal life — my undergraduate advisor Professor Ranjani Parthasarathi and my uncle Mr. R. Mahendravel. *RP ma'am*, as we affectionately call her, has been an inspiration and an unending source of positive energy. My uncle has been a hero to me and has offered timely advice that has directed me in the right path many times in my life. I would like to express my deep gratitude for both of them.

The last six months of dissertation research is similar to the last mile of a marathon. During this crucial time, my friend and brother, Ram, gave up many comforts in hosting us in his apartment. He would meditate for hours alongside of me when I was working on my dissertation. I am thankful beyond words for all his help, which has enabled my reaching this point.

I am blessed to have a wonderful friend and wife in Meena. She has put her career on hold for a year just to be with me during this critical period. She has laughed with me during the successes and cried with me during the failures. She has been a provider of nourishment both in spirit and as actual food. She has been a part of me in this whole process. It is not possible to do justice by expressing my thanks to her in words. The entire process of dissertation research has been both an exercise in confidence and an exercise in humility. I thank the experience itself, for it was built of many life lessons. I realize that whatever is being presented in the forthcoming pages, I have only been an instrument of. Hence, this work is dedicated to the source of it all.

### Dedication

To where it all came from

## Contents

| 1 | Intr | oduction                                               | 1  |

|---|------|--------------------------------------------------------|----|

| 2 | The  | rmal Modeling                                          | 7  |

|   | 2.1  | Introduction                                           | 7  |

|   | 2.2  | Related Work                                           | 7  |

|   | 2.3  | Importance of Directly Modeling Temperature            | 9  |

|   | 2.4  | The HotSpot Thermal Model                              | 13 |

|   | 2.5  | Analytical Choice of Parameters                        | 18 |

|   | 2.6  | Empirical Leakage Model                                | 23 |

| 3 | Dyn  | amic Thermal Management of a Single Core               | 26 |

|   | 3.1  | Introduction                                           | 26 |

|   | 3.2  | Related Work                                           | 29 |

|   | 3.3  | Techniques for Architectural DTM                       | 31 |

|   | 3.4  | Simulation Setup                                       | 42 |

|   | 3.5  | Results for DTM                                        | 48 |

|   | 3.6  | Conclusions and Future Work                            | 58 |

| 4 | Stat | ic Thermal Management through Core-Level Floorplanning | 60 |

|   | 4.1  | Introduction                                           | 60 |

|   | 4.2  | Related Work                                           | 62 |

|   | 4.3  | Potential in Lateral Spreading                         | 64 |

### Contents

|   | 4.5                                                                         | Results                                   | 73                                                       |

|---|-----------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------|

|   | 4.6                                                                         | Conclusions and Future Work               | 78                                                       |

| 5 | The                                                                         | rmal Benefit of Multicore Floorplanning   | 80                                                       |

|   | 5.1                                                                         | Introduction                              | 80                                                       |

|   | 5.2                                                                         | Related Work                              | 82                                                       |

|   | 5.3                                                                         | Methodology                               | 83                                                       |

|   | 5.4                                                                         | Results                                   | 89                                                       |

|   | 5.5                                                                         | Conclusion                                | 95                                                       |

| 6 | Gra                                                                         | nularity of Thermal Management            | 96                                                       |

|   |                                                                             |                                           |                                                          |

|   | 6.1                                                                         | Introduction                              | 96                                                       |

|   | 6.1<br>6.2                                                                  | Introduction                              | 96<br>99                                                 |

|   |                                                                             |                                           | 99                                                       |

|   | 6.2                                                                         | Related Work                              | 99<br>101                                                |

|   | <ul><li>6.2</li><li>6.3</li></ul>                                           | Related Work       An Analytical Approach | 99<br>101<br>110                                         |

| 7 | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                   | Related Work                              | 99<br>101<br>110                                         |

|   | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Con</li> </ul> | Related Work                              | <ul><li>99</li><li>101</li><li>110</li><li>133</li></ul> |

Х

# **List of Figures**

| 2.1 | Relationship between power density and temperature for different moving average         |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | intervals [104]                                                                         | 10 |

| 2.2 | Power density and temperature profiles of the load-store queue                          | 11 |

| 2.3 | Side view of a typical package. [104]                                                   | 15 |

| 2.4 | A conceptual view of the nodes of the thermal circuit in HotSpot [50]                   | 16 |

| 2.5 | Illustration of the RC networks corresponding to the Elmore delay model and the         |    |

|     | equivalent circuit for thermal conduction.                                              | 18 |

| 2.6 | A transient thermal conduction problem equivalent to HotSpot's RC network with          |    |

|     | a single node.                                                                          | 19 |

| 2.7 | Distributed vs. lumped thermal response                                                 | 21 |

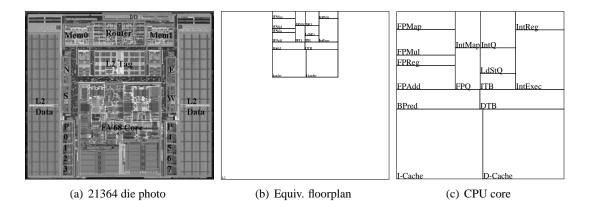

| 3.1 | (a): Die photo of the Compaq Alpha 21364 [26]. (b): Floorplan corresponding to          |    |

|     | the 21364 that is used in our experiments. (c): Closeup of 21364 core. [104]            | 32 |

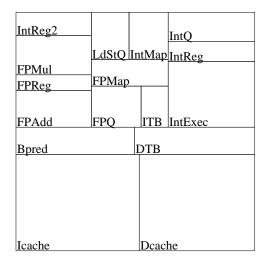

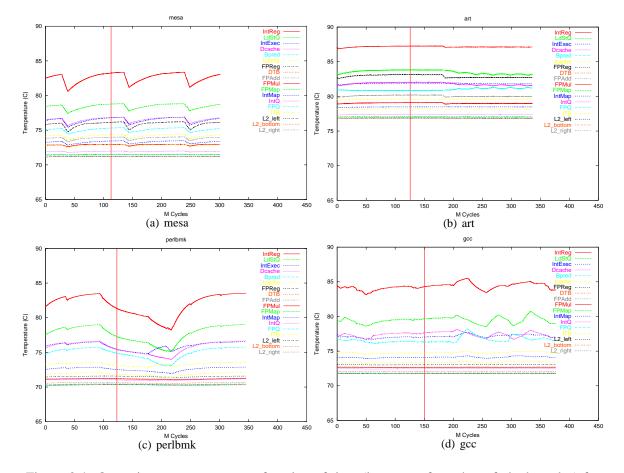

| 3.2 | Floorplan with spare integer register file for migrating computation. [104]             | 36 |

| 3.3 | Simulated and calculated operating frequency for various values of $V_{dd}$ . The nomi- |    |

|     | nal operating point of our simulated processor is 3 GHz at 1.3V. [104]                  | 38 |

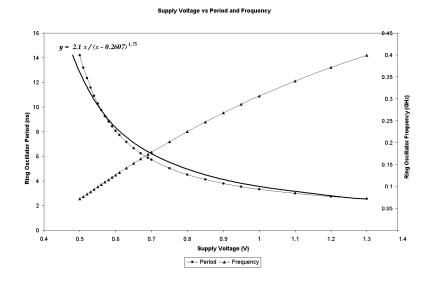

| 3.4 | Operating temperature as a function of time (in terms of number of clock cycles)        |    |

|     | for various warm and hot benchmarks. [104]                                              | 49 |

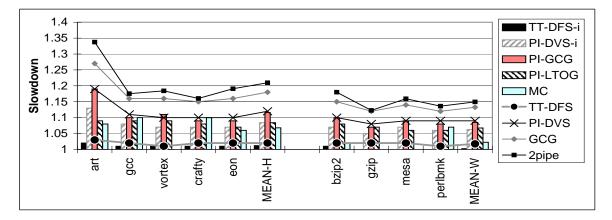

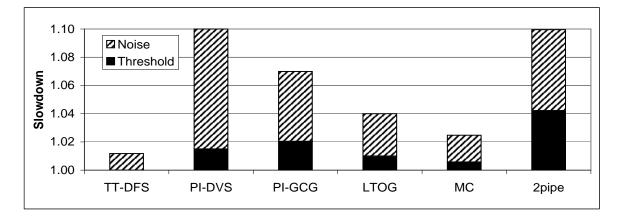

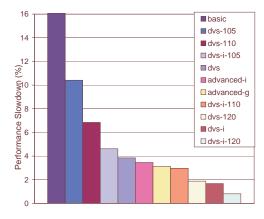

| 3.5 | Slowdown for DTM. Bars: better techniques. Lines: weaker techniques. [104]              | 49 |

| 3.6 | Slowdown for DTM from eliminating sensor noise, and from the consequent in-             |    |

|     | crease in trigger threshold to 82.8°. [104]                                             | 53 |

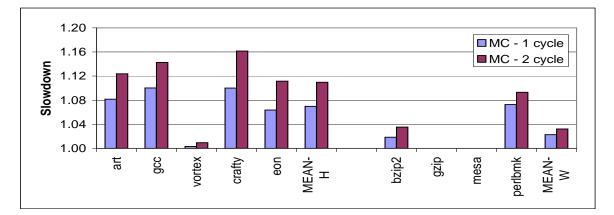

| 3.7        | Slowdown for MC with 1- and 2-cycle penalties for accessing the spare register                                                                                                                                                                                                                                 |          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | file. [104]                                                                                                                                                                                                                                                                                                    | 54       |

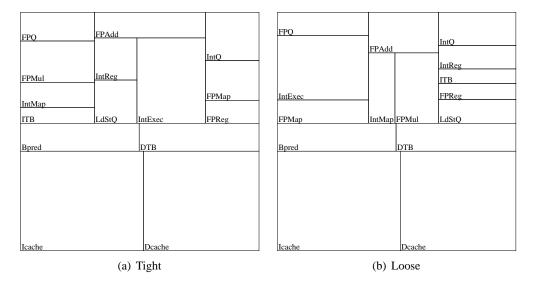

| 3.8        | Two floorplans used to study effects of lateral thermal diffusion. [104]                                                                                                                                                                                                                                       | 56       |

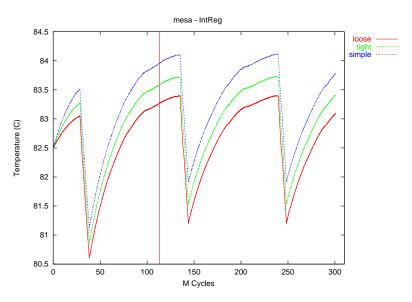

| 3.9        | Temperature as a function of time for the integer register file with the mesa bench-                                                                                                                                                                                                                           |          |

|            | mark, for two different floorplans (tight and loose) and a simulation with lateral                                                                                                                                                                                                                             |          |

|            | thermal resistance omitted (simple). [104]                                                                                                                                                                                                                                                                     | 57       |

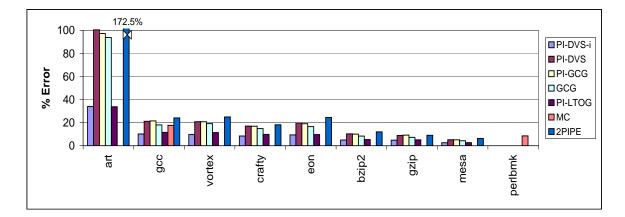

| 3.10       | Percent error in execution time when DTM techniques are modeled using no-DTM                                                                                                                                                                                                                                   |          |

|            | heat sink temperatures. [104]                                                                                                                                                                                                                                                                                  | 58       |

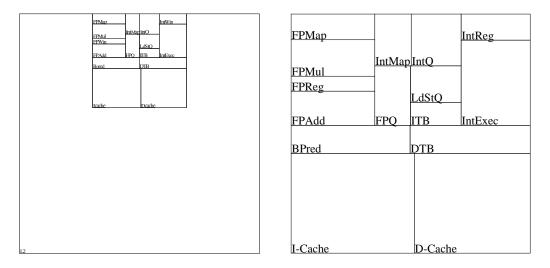

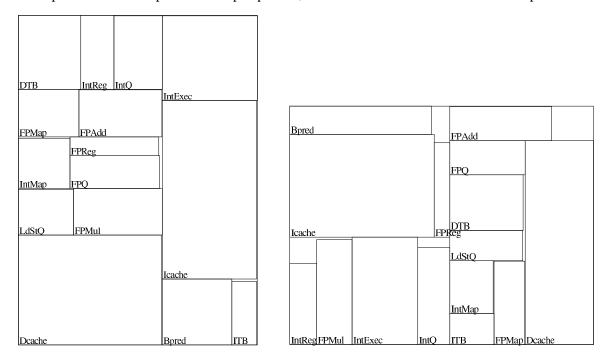

| 4.1        | (a) The basic floorplan corresponding to the 21364 that is used in our experiments.                                                                                                                                                                                                                            |          |

|            | (b) Close-up of the core area. [91]                                                                                                                                                                                                                                                                            | 69       |

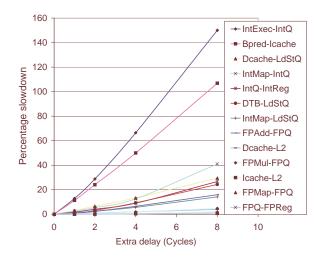

| 4.2        | Performance impact of varying the delay on critical wires. [91]                                                                                                                                                                                                                                                | 71       |

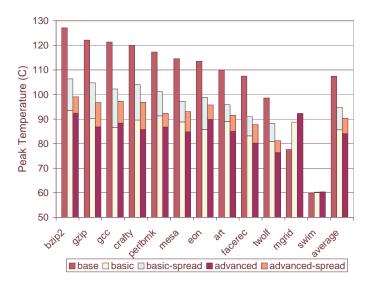

| 4.3        | Floorplans generated by (a) <i>flp-basic</i> and (b) <i>flp-advanced</i> schemes. [91]                                                                                                                                                                                                                         | 74       |

| 4.4        | Impact of floorplanning on peak temperature. [91]                                                                                                                                                                                                                                                              | 76       |

| 4.5        | Performance slowdown of the various thermal management schemes. [91]                                                                                                                                                                                                                                           | 77       |

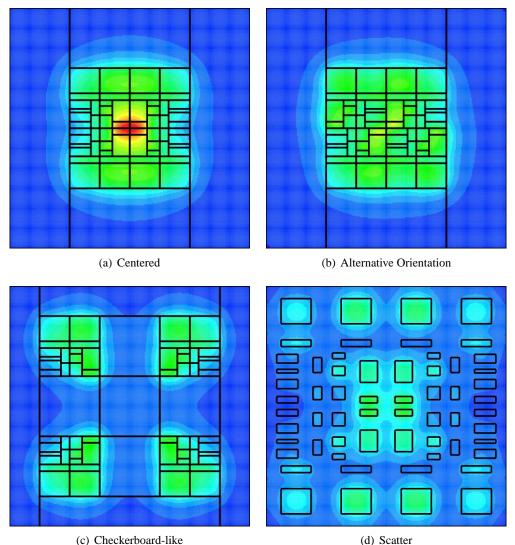

| 5.1        | Illustration of different core arrangements for a four-way CMP with each core re-                                                                                                                                                                                                                              |          |

|            | sembling an Alpha 21364. (a) shows a typical floorplan with hot units adjacent                                                                                                                                                                                                                                 |          |

|            | to each other. (b) shows a floorplan with alternative orientations of the cores. (c)                                                                                                                                                                                                                           |          |

|            |                                                                                                                                                                                                                                                                                                                |          |

|            | shows a checkerboard-like arrangement with the use of L2 cache banks as cooling                                                                                                                                                                                                                                |          |

|            | shows a checkerboard-like arrangement with the use of L2 cache banks as cooling buffers between the cores. (d) shows an arrangement used for a potential study with                                                                                                                                            |          |

|            |                                                                                                                                                                                                                                                                                                                |          |

|            | buffers between the cores. (d) shows an arrangement used for a potential study with                                                                                                                                                                                                                            | 84       |

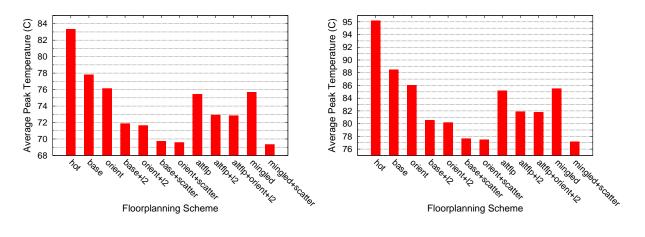

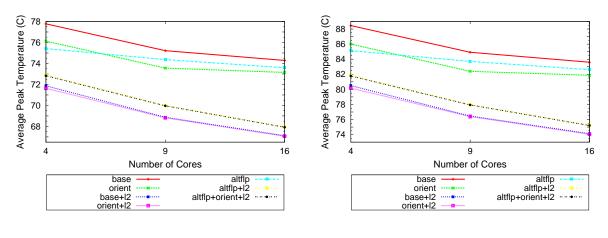

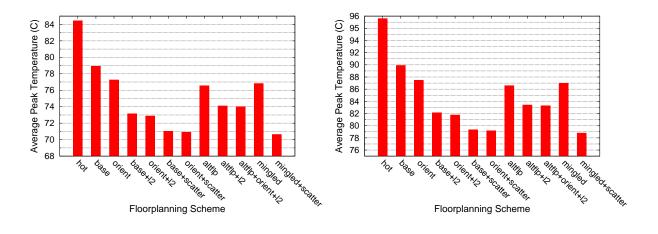

| 5.2        | buffers between the cores. (d) shows an arrangement used for a potential study with functional blocks scattered amidst the cache banks. The adjacency of the blocks in                                                                                                                                         | 84<br>90 |

| 5.2<br>5.3 | buffers between the cores. (d) shows an arrangement used for a potential study with functional blocks scattered amidst the cache banks. The adjacency of the blocks in the original floorplan is maintained through the scattering. [89]                                                                       |          |

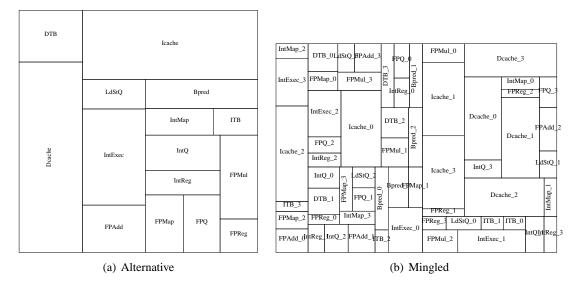

|            | buffers between the cores. (d) shows an arrangement used for a potential study with functional blocks scattered amidst the cache banks. The adjacency of the blocks in the original floorplan is maintained through the scattering. [89] Floorplans used for the <i>altflp</i> and <i>mingled</i> studies [89] |          |

|            | buffers between the cores. (d) shows an arrangement used for a potential study with<br>functional blocks scattered amidst the cache banks. The adjacency of the blocks in<br>the original floorplan is maintained through the scattering. [89]                                                                 | 90       |

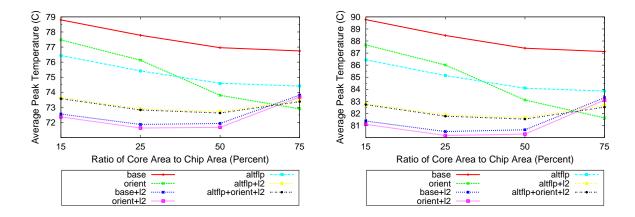

| 5.5 | Impact of the ratio of core area to chip area. The size of each core remains the same          |     |

|-----|------------------------------------------------------------------------------------------------|-----|

|     | while that of the L2 cache is increased, keeping its power density constant. [89] $\therefore$ | 94  |

| 5.6 | Thermal performance of the floorplanning schemes on doubling the L2 cache power                |     |

|     | density. [89]                                                                                  | 95  |

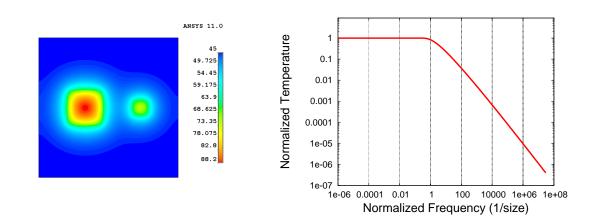

| 6.1 | Illustration of the spatial thermal filtering. (a) Two blocks of different sizes having        |     |

|     | the same power density. (b) low-pass filter "Bode plot" frequency response. [88]               | 97  |

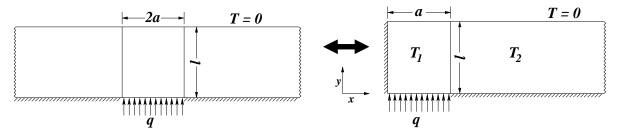

| 6.2 | Simplified heat conduction problem to mimic a silicon die of thickness $l$ . A power           |     |

|     | density of $q$ is applied at the bottom in a region of size $2a$ . Insulated boundaries        |     |

|     | are marked by slanted lines. Serrated lines indicate that the boundaries extend to             |     |

|     | infinity in that direction. (a) shows the original infinite version of the problem             |     |

|     | and (b) shows the equivalent semi-infinite version that (a) reduces to because of              |     |

|     | symmetry. (b) is essentially the right half of (a) [88]                                        | 103 |

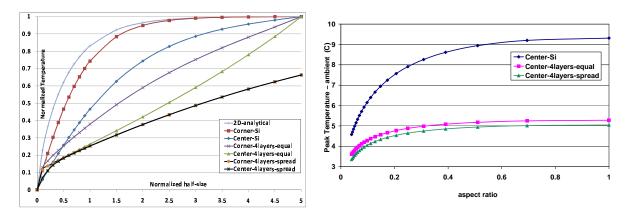

| 6.3 | Comparison of the analytical model and FEM simulation. (a) shows the impact                    |     |

|     | of power dissipator size and (b) shows the effect of aspect ratio. Note that the               |     |

|     | center-4layers-spread and corner-4layers-spread curves are coincident on top of                |     |

|     | each other. [88]                                                                               | 108 |

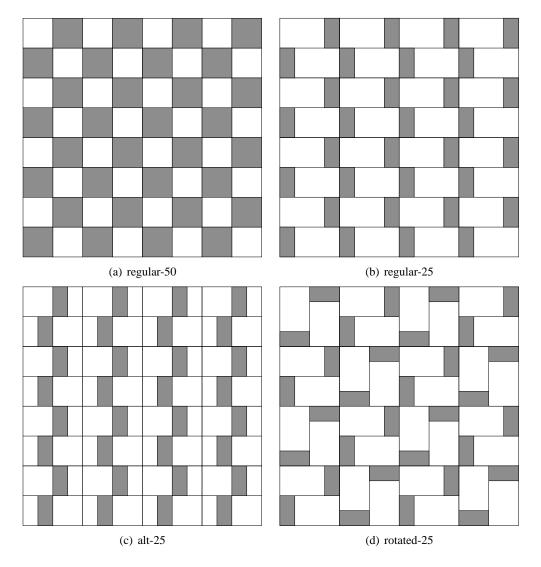

| 6.4 | Illustration of the several checkerboard configurations studied. Darkly shaded areas           |     |

|     | denote the cores and the unshaded areas denote the lower-level cache banks. The                |     |

|     | numeric suffix attached to the name of each configuration indicates the percentage             |     |

|     | of the die area occupied by the cores. Each figure above shows a manycore die with             |     |

|     | 32 cores. [88]                                                                                 | 112 |

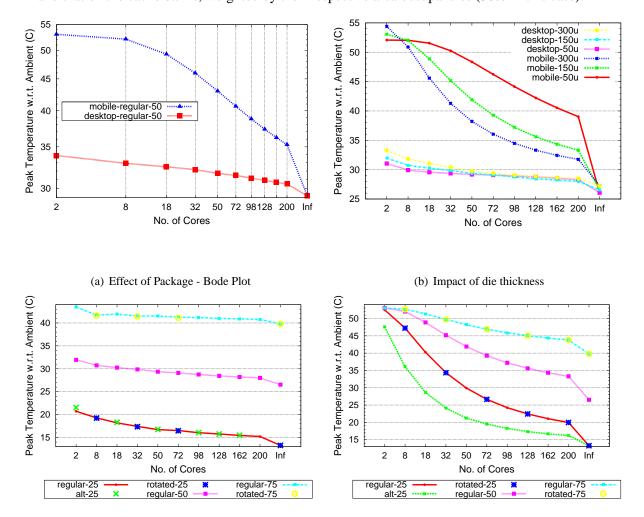

| 6.5 | Results of the checkerboard experiments. Note the overlap of the curves rotated-               |     |

|     | 25 and regular-25 (rotated-75/regular-75) in (c) and (d). alt-25 and regular-25 are            |     |

|     | also coincident in (c). [88]                                                                   | 113 |

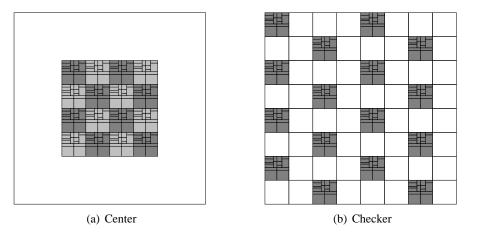

| 6.6 | Illustration of the two different manycore scenarios simulated. The unshaded ar-               |     |

|     | eas indicate second-level cache. The shaded areas denote cores resembling Alpha                |     |

|     | 21364. [88]                                                                                    | 117 |

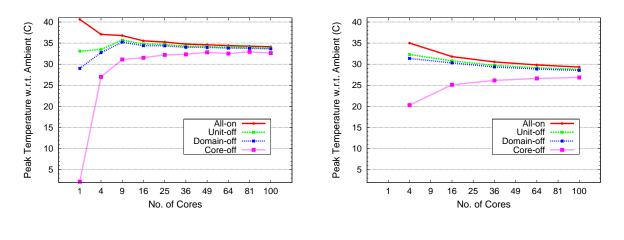

| 6.7  | Results of the local <i>vs</i> . global thermal management study. [88]                   | 119 |

|------|------------------------------------------------------------------------------------------|-----|

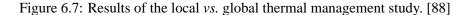

| 6.8  | Two different placements studied for the data cache. The unshaded areas denote the       |     |

|      | SRAM sub-arrays while the shaded portions indicate the periphery and routing. [88]       | 123 |

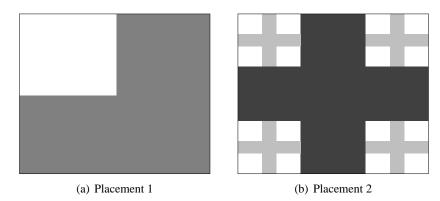

| 6.9  | Results of the data cache thermal experiments. (a) and (b) show the case when all        |     |

|      | lines are passive. (c) plots the peak temperature of the active lines as a function of   |     |

|      | the number of lines that are accessed contiguously. [88]                                 | 125 |

| 6.10 | Relationship between sensor error and inter-sensor distance. For an Alpha 21264-         |     |

|      | like core, (a) shows a sample temperature profile and (b) shows what is seen by the      |     |

|      | sensors. The black dots denote the positions of the sensors. (c) plots the average       |     |

|      | maximum sensor error of the SPEC2000 benchmark suite for two different types of          |     |

|      | package. [88]                                                                            | 128 |

| 6.11 | Results of the interpolation study. (a) and (b) illustrate the behaviour of the bilinear |     |

|      | and bicubic spline algorithms for the thermal profile and sensor readings as in fig-     |     |

|      | ures 6.10(a) and (b) respectively. (c) presents the experimental results of comparing    |     |

|      | the algorithms against the nearest-neighbour interpolation scheme. [88]                  | 131 |

# List of Tables

| 2.1 | Correlation of average power vs. temperature for power averaging windows of                       |     |

|-----|---------------------------------------------------------------------------------------------------|-----|

|     | 10K–1B cycles. [104]                                                                              | 9   |

| 2.2 | Analogy between thermal and electrical quantities [104]                                           | 14  |

| 3.1 | Configuration of simulated processor microarchitecture. [104]                                     | 44  |

| 3.2 | Benchmark summary. "I" = integer, "F" = floating-point. Fast-forward distance                     |     |

|     | (FF) represents the point, in billions of instructions, at which warmup starts (see               |     |

|     | Sec. 3.4.5). [104]                                                                                | 46  |

| 3.3 | Fraction of cycles in thermal violation (no DTM modeled) for the two different                    |     |

|     | floorplans (loose and tight) with lateral thermal diffusion properly modeled (cor-                |     |

|     | rect), and with lateral resistances omitted (simple). [104]                                       | 55  |

| 3.4 | Fraction of cycles above the thermal trigger point (no DTM modeled) for the two                   |     |

|     | different floorplans. [104]                                                                       | 55  |

| 4.1 | Peak steady-state temperature for different levels of lateral heat spreading ( $^{\circ}$ C) [91] | 65  |

| 4.2 | Benchmark characteristics [91]                                                                    | 70  |

|     |                                                                                                   |     |

| 6.1 | Area, power and power density distribution within the data cache for the <i>bzip2</i>             |     |

|     | benchmark. [88]                                                                                   | 122 |

## Chapter 1

## Introduction

Since the advent of the very first microprocessor, the transistors that make them have continued to shrink in size exponentially. This scaling has consistently kept up with or even surpassed the rate of growth predicted by Gordon Moore's empirical law stated in 1965 [73]. In comparison with the early microprocessors, today's processors are faster and cheaper by several orders of magnitude owing to this exponential growth in transistor density. However, as process technology scales into the nanometer region, several hindrances to its continuation emerge. Low-level effects which were previously considered second-order and have traditionally been largely invisible to computer architects have surfaced to become primary concerns. Processor temperature is one such concern that has arguably become one of the hardest obstacles to continued technology scaling.

Most of the energy consumed by a microprocessor is dissipated as heat due to the resistive behaviour of the processor circuits. The temperature of a chip, which is a measure of the amount of heat energy stored in it, is directly related to the power density (*i.e.*, the power consumed per unit area of the chip). In order to see the impact of scaling on temperature, it is illuminating to study the relationship between scaling and power density. Scaling theory [29] provides a simple way to reason about such a relationship between the device parameters (such as transistor length, supply voltage *etc.*) of successive technology generations. Every successive process generation shrinks the length of the transistor by a constant fraction of the previous length. This fraction is by a called the scaling factor (say *k*) and is typically  $\approx 1/\sqrt{2}$ . Hence, the area of the transistor scales proportional to  $k^2$ , *i.e.*, approximately halving every successive generation. Assuming ideal scaling, supply

voltage (*V*) scales down and frequency (*f*) scales up linearly. Assuming that the microarchitecture remains the same, the scaling of the intrinsic capacitance (*C*) of the transistor is also linear in this factor. Hence, the power consumption of the transistor, given by the formula  $CV^2f$ , scales down by a factor  $= k \times k^2/k = k^2$ . In other words, since the area scales down by  $k^2$ , the power density remains constant under ideal scaling. However, in reality, supply voltage has not been able to scale as well as the transistor dimensions. In fact, more recently, in order to maintain the performance under increasing leakage, it has not been able to scale at all! This has resulted in processor power almost remaining constant in moving to a newer process generation. More interestingly, the power density increases approximately by a factor of  $k^2$  every generation! This exponential increase in power density, if left unmanaged, would result in an exponential increase of temperature every successive generation. Since that cannot be allowed (otherwise, the chip would melt!), huge efforts have been put into the removal of heat away from the die-surface of a microprocessor. This has led to expensive packages (heat sinks, heat pipes *etc.*) and as a corollary, exponential increase in the cost of such cooling solutions.

Increase in die temperature is undesirable for a variety of reasons. Catastrophic failure such as the melting of the chip is a possibility, albeit a distant one. In reality, more pertinent reasons are in the form of increased leakage power and accelerated aging that reduces lifetime reliability.

Transistors consume power even when they are idle and not switching. This is called static power or leakage power. Even under nominal conditions, it can be a significant fraction (> 30%) [99] of the total power consumption at current feature sizes. It varies exponentially with respect to temperature. As temperature itself depends on the power consumption, there is a circular dependence between them. In extreme cases, this can result in a self-reinforcing positive feedback loop that leads to thermal runaway.

Temperature also has an exponentially adverse effect on the expected lifetime of a microprocessor. The Mean Time To Failure (MTTF) of a chip can be empirically described using the Arrhenius Equation given by:

$$MTTF = Ae^{-\frac{E_a}{k \cdot T}}$$

Here, T is the temperature, A is an empirical constant and  $E_a$  is the activation energy of the failure mechanism. It is to be noted that this equation does not capture all the effects of temperature (like thermal cycling, thermal gradients *etc.*) on reliability. However, it is a useful expression for first-order estimation. It actually comes from Chemistry where the rate of a chemical reaction is expressed as an exponential function of the temperature of operation. The rate of reaction or equivalently, the rate of failure in case of silicon, is highly accelerated at higher temperatures. In fact, the same principle is used in the testing of chips by accelerating their ageing process from several years to laboratory time scales through the artificial elevation of temperatures.

Apart from high performance microprocessors, temperature is also a matter of concern for mobile processors. Though such chips tend to be low in power consumption, their power density can be quite high because of their form factor (*e.g.* System-On-a-Chip (SoC) architectures) and the high-performance nature of the real-time applications that run on them. Usability considerations like fan noise, wearability *etc.*, also dictate a lower operating temperature budget for these chips. Thus, with the increase in cooling costs, adverse effect on static power, lifetime reliability and usability of processor chips, temperature has become a first-class design constraint in microprocessor development akin to performance.

The thermal problem described above can be approached from different perspectives. For instance, from a mechanical engineering perspective, one can design better, more efficient and cheaper heat removal systems. This is a significant challenge since we are already at the limits of affordable air cooling. For instance, the ITRS [99] projects a very flat trend for air cooling capacity even in the long term. From an operating systems perspective, one can employ better scheduling algorithms that distribute heat evenly across the entire chip by interleaving hot and cold processes in both time and space. With the potential availability of spare cores to run the application, multicore processors offer extra flexibility in this regard. From a compiler design perspective, one can generate code that distributes computation in a manner which minimizes power density. Instead, the scope of this dissertation is to study the possibilities of thermal alleviation from the perspective of the *architecture of the microprocessor*. The microarchitecture is the final determinant of how much computation happens where and when. Hence, it is unique in its ability to accurately identify

the sources of thermal inefficiency and either curb them at the origin or manage them effectively within a desired cost budget. This dissertation is an exercise in offering sufficient research evidence for such an assertion. It should be noted that although microarchitectural power management might help with temperature by limiting wasteful power dissipation, it does so mainly by managing activity in the temporal dimension. Thermal management extends such control to the spatial dimension as well, offering additional levers in the temperature *vs.* performance trade-off.

The first step in addressing the thermal management problem at the microarchitectural level is the ability to model the temperature of a microprocessor accurately and efficiently. Hence, this dissertation first presents a microarchitecture-level thermal modeling tool called HotSpot [50] that models the heat conduction as an equivalent electrical circuit constructed from the layout information of the microprocessor. Given the per-unit power consumption, it then uses standard circuit solving techniques to solve for temperature. HotSpot is a computationally-efficient infrastructure that has been widely used in the computer architecture research community. It has been downloaded by more than one thousand users. This dissertation guides the design of certain important parameters of HotSpot through approximations derived using analytical foundations. Furthermore, since there is a circular and exponential relationship between leakage power and temperature, this dissertation also comes up with an empirical leakage power model by reverse engineering data from the reports of the International Technology Roadmap for Semiconductors (ITRS) [99].

In order to make a case for the argument that microarchitectural thermal management can be effective, the dissertation then presents and evaluates several Dynamic Thermal Management (DTM) schemes for a single-core microprocessor. They distribute heat both over time and space by controlling the level of computational activity in the individual functional blocks of the core. These techniques can manage worst-case thermal situations efficiently, thereby assisting the external cooling solutions to be built for the average-case rather than the worst-case.

Orthogonal to the individual activity of the functional blocks in a microprocessor, another important factor that affects the temperature distribution of a chip is the lateral coupling between adjacent blocks due to the spreading of heat in silicon. This is determined by the floorplan of the microprocessor. Hence, this dissertation also investigates whether floorplanning at the microarchitectural level can be applied viably towards thermal management by placing hot units close to cold ones. It develops a thermally-aware microarchitectural floorplanning tool called HotFloorplan and studies the various thermally mitigating placement choices available within a single core and across multiple cores of a microprocessor. For a single core, this work employs a simulated annealing-based [60] scheme that includes both performance and temperature in its cost function. For multiple cores, it experiments with the orientation of the cores so as to keep the hottest units of adjacent cores as far apart as possible and uses the relatively cooler L2 banks as thermal buffers between the much hotter cores.

The final piece of this dissertation focuses on the size granularity at which thermal management is important. Regions of high power density do not cause hot spots if they are small enough in size (*i.e.*, if their lateral dimensions are much smaller than the chip thickness). In other words, silicon acts as a spatial low-pass filter for temperature. This dissertation explains this phenomenon with an analytical formulation derived by solving the steady-state two-dimensional differential equation of thermal conduction for a geometry similar to microprocessor chips. It also illustrates this with three different microarchitectural examples: a study of the thermal efficiency of small cores *vs.* large cores in a manycore processor, an investigation of whether high aspect ratio sub-blocks like cache lines can become hot spots due to malicious code behaviour and an exploration of thermal sensor accuracy as a function of the distance between sensors with an examination of the effectiveness of sensor interpolation schemes.

With this overview, following are the contributions of this work:

- The design of an accurate and efficient thermal model guided by analytical foundations from conduction heat transfer and an empirical model for leakage power that accounts for dependence on its temperature and supply voltage. [50, 52, 103]

- New microarchitectural thermal management schemes for a single-core microprocessor: temperature-tracking Dynamic Frequency Scaling (DFS) and migration of computation to a spare register file. [101, 102, 103]

- A thermally-aware floorplanning scheme for a single-core microprocessor that incorporates

the key insight of accounting for the amount of communication on the wires and weighting them according to that. [91]

- Multicore floorplanning techniques that experiment with the orientation of the cores and insert second-level cache banks in between the cores in order to reduce the peak temperature. [89]

- An analytical framework that explains the spatial filtering behaviour of lateral thermal conduction, which is then used to understand several interesting questions on microarchitectural thermal granularity including the thermal efficiency of manycores, cache lines and sensor interpolation. [88]

The remainder of the dissertation is organized as follows: Chapter 2 describes the design of the thermal and empirical leakage power models, throwing light on the analytical basis of the thermal model's parametric choices; Chapter 3 presents and evaluates the various single-core thermal management schemes; Chapter 4 explains the thermally-aware single-core floorplanning algorithm and discusses its thermal and performance impact; Chapter 5 studies the various multicore floorplanning options including core orientation and cache bank insertion; Chapter 6 discusses the investigation on the granularity of thermal management; and Chapter 7 concludes this dissertation by summarizing the most important lessons and providing suggestions for potential directions for the future.

# **Chapter 2**

## **Thermal Modeling**

### 2.1 Introduction

This chapter discusses the design of the HotSpot thermal model [50, 52, 103] and the empirical leakage power model [103], providing insights into the analytical foundations of some of the parametric choices in HotSpot. Section 2.2 describes the work done by others closely related to the area of microarchitectural thermal modeling. Section 2.3 discusses the need for directly modeling temperature at the microarchitectural level. Section 2.4 explains the construction of the HotSpot model. Section 2.5 presents the analytical rationale behind the choice of a couple of important parameters of HotSpot. Section 2.6 details the empirical leakage power model.

#### 2.2 Related Work

Thermal models developed prior to this work are typically at the circuit-level and the few microarchitectural models ignore the lateral heat spreading in the chip. An excellent survey of the circuit-level techniques is given by Sabry in [86] and more recently, by Pedram and Nazarian [79]. Batty *et al.* [10], Cheng and Kang [22], Koval and Farmaga [62], Székely *et al.* [83, 109], Torki and Ciontu [111] all describe techniques for modeling localized heating within a chip due to different power densities of various blocks, but none of these tools are easily adapted to architectural exploration for a variety of reasons. Microarchitectural models are employed very early in the design stage, at a *pre-RTL* level, when detailed layout and power consumption information may not be available. Architectural modeling typically precludes direct thermal-response measurements, *e.g.* [109, 111]. Similarly, the use of analytical power models obviates the need for joint electrothermal modeling, *e.g.* [109]. Furthermore, most of the prior models are either at a lower *post-RTL* level depending on VLSI netlists and structural implementation details, or only give steady-state solutions.

Two microarchitectural thermal models we are aware of prior to this work are from Dhodapkar et al. [30] and Skadron et al. [100]. TEMPEST [30] models temperature directly using an equivalent RC circuit, but contains only a single RC pair for the entire chip, giving no localized information. [100] proposed a simple model for tracking temperature on a per-unit level but ignored the effect of lateral heat diffusion. Since this work, a few more higher-level thermal models have been developed. ATMI [72] is an analytical model based on an explicit solution to the heat equation. While the accuracy of an analytical model is attractive, it also implies that the expression for the solution has to be evaluated at every point of interest on the chip. This can be prohibitive when one is looking for temperature not at a particular point but with a particular property (e.g. maximum temperature of each functional block). Moreover, it is not very flexible in terms of the package configuration and number of layers, which could be an obstacle in its use for exploration at the microarchitectural level. For instance, adding support for an extra layer of Thermal Interface Material (TIM) would involve significant effort in recomputing the analytical solutions. The Mercury [46] and Thermostat [24], models that are intended to be used at the full-system-level, are also worth mentioning here. Mercury is a system-level temperature emulation suite that uses offline calibration and online update of per-component utilization information to compute temperature of systems (including disks, processors, air inlets etc.). Thermostat employs Computational Fluid Dynamic (CFD) modeling of rack-mounted servers. Although both tools model the entire system including convective heat transfer, they are much more coarse-grained by design. The microprocessor itself is only a component within the system they model and hence no localized information is obtainable, which is essential for architectural studies.

Since this work, there have been efforts in applying state-of-the-art numerical techniques such

as multigrid methods [67], Discrete Cosine Transforms (DCT) [118], moment matching [69] and adaptive temporal adaptation [117] to thermal circuit solvers. There have also been improvements to the thermal solver of HotSpot suggested by others [42]. HotSpot has benefited from some of these efforts and I have since incorporated a multigrid method in HotSpot's steady-state thermal solver. However, these models do not provide significant extra detail and lack the flexibility of HotSpot. Since microarchitectural simulations tend to be long, the simulation speed of HotSpot remains quite sufficient for most architectural studies.

| Units   | Avg. Temp. | $R^{2}$ (%) |      |      |      |      |      |

|---------|------------|-------------|------|------|------|------|------|

|         | (°C)       | 10K         | 100K | 1M   | 10M  | 100M | 1B   |

| Icache  | 74.4       | 43.9        | 51.1 | 55.8 | 73.8 | 78.5 | 10.5 |

| ITB     | 73.2       | 35.3        | 42.2 | 46.8 | 64.0 | 75.0 | 10.6 |

| Bpred   | 76.2       | 54.0        | 71.5 | 77.6 | 88.7 | 91.0 | 5.3  |

| IntReg  | 83.5       | 44.2        | 51.9 | 57.0 | 76.4 | 71.0 | 8.0  |

| IntExec | 76.7       | 46.3        | 53.3 | 57.9 | 75.7 | 76.6 | 8.3  |

| IntMap  | 73.9       | 41.7        | 49.6 | 54.8 | 73.5 | 76.8 | 8.0  |

| IntQ    | 72.4       | 31.5        | 36.4 | 39.6 | 53.9 | 80.7 | 13.0 |

| LdStQ   | 79.2       | 47.9        | 63.4 | 69.0 | 83.6 | 83.2 | 6.6  |

| Dcache  | 77.3       | 46.8        | 60.5 | 65.9 | 81.2 | 82.8 | 10.8 |

| DTB     | 72.0       | 29.6        | 38.2 | 41.7 | 53.4 | 87.5 | 16.4 |

| FPReg   | 73.0       | 26.0        | 29.6 | 38.8 | 64.6 | 84.8 | 21.1 |

| FPAdd   | 72.6       | 49.7        | 51.1 | 54.9 | 66.5 | 86.4 | 24.9 |

| FPMul   | 72.6       | 53.9        | 54.1 | 54.9 | 62.1 | 84.8 | 29.6 |

| FPMap   | 71.7       | 16.8        | 20.2 | 22.3 | 26.9 | 0.5  | 3.2  |

| FPQ     | 71.8       | 28.0        | 30.0 | 35.2 | 49.4 | 78.0 | 30.7 |

| L2      | 71.7       | 14.2        | 19.7 | 21.8 | 26.6 | 49.9 | 3.3  |

### 2.3 Importance of Directly Modeling Temperature

Table 2.1: Correlation of average power vs. temperature for power averaging windows of 10K–1B cycles. [104]

Temperature of a functional block of a microprocessor depends upon the power consumed by it per unit area (its power density). In fact, the thermal capacity of silicon acts as a temporal low pass filter and smooths out the spikes of power density. This behaviour has prompted a few prior studies to model temperature by averaging power dissipation over a window of time. This section will show the fallacy in using such a proxy for temperature. While the moving average helps in temporal smoothing, the temperature of a block depends not only on its power density but also on the temperatures of the other blocks nearby. Hence, any amount of temporal averaging without considering this lateral coupling of heat will not track its temperature reliably.

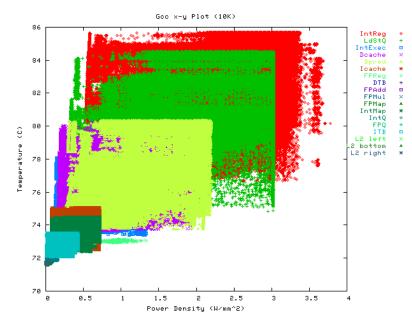

#### (a) 10 K, all blocks

Figure 2.1: Relationship between power density and temperature for different moving average intervals [104].

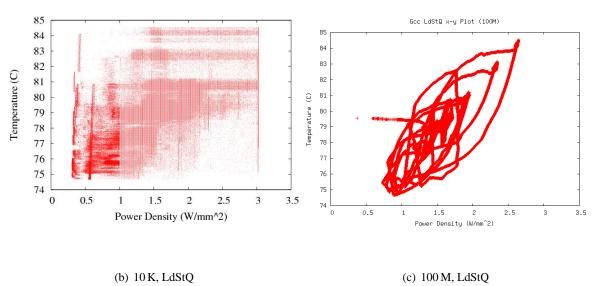

Figure 2.2: Power density and temperature profiles of the load-store queue.

To show the importance of such a thermal model with lateral diffusion capability as opposed to a power metric, Table 2.1 shows the  $R^2$  value for correlation between temperature and a moving average of power dissipation for different averaging intervals. Each row of the table denotes an

average of power dissipation for different averaging intervals. Each row of the table denotes an architectural functional block of an out-of-order processor similar to the Alpha 21364 [103]. The  $R^2$  value gives the percentage of variance that is common between two sets of data; values closer to 100% indicate better correlation. The data in Table 2.1 come from gcc, a representative benchmark. It can be seen that overall, there is poor correlation between temperature and moving average of the power dissipation. Even with the best-correlated averaging interval (100 million cycles), power still cannot track operating temperature effectively. This is further shown in figures 2.1 and 2.2. Figure 2.1 presents the relationship between power density and temperature for two different averaging intervals. Figure 2.1(a) shows the scatter plots of power density vs. temperature for all the major architectural blocks for an averaging interval of 10K cycles. For clarity, Figure 2.1(b) shows the same data only for the load-store queue. Figure 2.1(c) shows a similar scatter plot but for a higher averaging interval of 100M cycles. Figures 2.2(a) and (b) show the same power density and temperature data for the LdStQ block individually against time (in cycles). Any linear relationship between power density and temperature will show up as an approximate straight line in Figure 2.1. A temperature metric calibrated from a simple average of the power dissipation has such a linear relationship. However, what is seen in the graphs is an absence of any such linear relationship even at the higher averaging interval of 100M cycles (2.1(c)). It can be seen in Figure 2.1 that, for a given power density, the temperature varies by a large margin and vice-versa. Actually, for the LdStQ block, in 2.1(b), there is a clear range in the power density (around 0.35 to  $3 W/mm^2$ ) and temperature (around 74.5 to 84.5°C). On examining the graphs 2.2(a) and (b), it can be observed that this range corresponds to their maximum and minimum values over time. For power density, the maximum and minimum values also correspond to maximum and zero utilization of the LdStQ respectively. Also, the power density graph (2.2(a)) shows a pattern of bands while the temperature graph shows a pattern of lines. This means, for almost any given temperature, the instantaneous power density at that time could be all over the board. This uncorrelated behaviour is the reason for the rectangular shape in the first two graphs and the diverging shape in the third graph of Figure 2.1. It is also the reason why power density is not a good proxy for temperature. Hence, for reliable temperature estimation, it is important to model temperature directly.

### 2.4 The HotSpot Thermal Model

As a solution to the modeling problem, this dissertation presents my contributions to HotSpot [50, 52, 103], an efficient, extensible microarchitectural thermal model. HotSpot is available for free public download in the source form from http://lava.cs.virginia.edu/HotSpot. It is based on the well-known analogy [48, 64] that exists between the physical laws that govern current flow and heat flow, summarized in Table 2.2. Temperature is akin to "electric potential". Heat flow can be described as a "current" passing through a thermal "resistance" (R), leading to a temperature difference analogous to a "potential difference" or "voltage". Thermal "capacitance" (C) measures the amount of heat energy stored in a body — specifically, the product of its volume and specific heat capacity — and hence its rise in temperature. It is necessary for modeling transient behaviour, to capture the delay before a change in power results in the temperature's reaching steady state. Lumped values of thermal R and C can be computed to represent the heat flow among units and from each unit to the thermal package. The thermal Rs and Cs together lead to exponential rise and fall times characterized by thermal RC time constants analogous to the electrical RC time constants. The rationale behind this analogy is that current and heat flow are described by exactly the same differential equations that describe the flow, *i.e.*, Ohm's law for electrical conduction and Fourier's law for heat conduction. Together with the principle of conservation of energy, these differential equations completely determine the electrical and thermal conduction in a body. HotSpot utilizes this principle in that it computes the thermal resistances and capacitances of a chip based on its geometry and floorplan. Then, for a power density map provided by a power-performance simulator (e.g. Simplescalar [5] and Wattch [13]), it solves for the temperatures using standard circuit solving techniques. Early releases of HotSpot [103] incorporated a single circuit node for each functional block of a floorplan. Such a *block-based* model has the advantage of high computational efficiency. However, feedback from the use of HotSpot by the research community suggested that additional modeling capability for high accuracy even at much finer levels of granularity is desirable. To this end, later releases of HotSpot [50, 52] also include support for high resolution through a threedimensional, uniform grid-like structure of its thermal Rs and Cs. In such a case, each functional block is modeled as a grid of thermal Rs, each with its own capacitance to ground. With the presence of both the *block-based* and the *grid-based* models in HotSpot, the user is offered a choice between two levels of modeling granularity as a trade-off between accuracy and efficiency.

| Thermal quantity                                        | unit            | Electrical quantity                         | unit                 |

|---------------------------------------------------------|-----------------|---------------------------------------------|----------------------|

| Q, Heat                                                 | J               | q, Charge                                   | С                    |

| T, Temperature                                          | Κ               | φ, Potential                                | V                    |

| Temperature difference                                  | Κ               | V, Voltage                                  | V                    |

| P, Heat flow, power                                     | W               | <i>I</i> , Current flow                     | Α                    |

| $\kappa$ , Thermal conductivity                         | $W/(m \cdot K)$ | $\sigma$ , Electrical conductivity          | $1/(m \cdot \Omega)$ |

| q, Heat flux, power density                             |                 | <i>j</i> , Current density                  |                      |

| $= -\kappa \nabla T$ (Fourier's law)                    | $W/m^2$         | $= -\sigma \nabla \phi$ (Ohm's law)         | $A/m^2$              |

| $R_{th}$ , Thermal resistance                           | K/W             | R, Electrical resistance                    | $\Omega = V/A$       |

| $C_{th}$ , Thermal mass, capacitance                    | J/K             | C, Electrical capacitance                   | F = C/V              |

| $\tau_{th} = R_{th} \cdot C_{th}$ , Thermal RC constant | S               | $\tau = R \cdot C$ , Electrical RC constant | S                    |

Table 2.2: Analogy between thermal and electrical quantities [104]

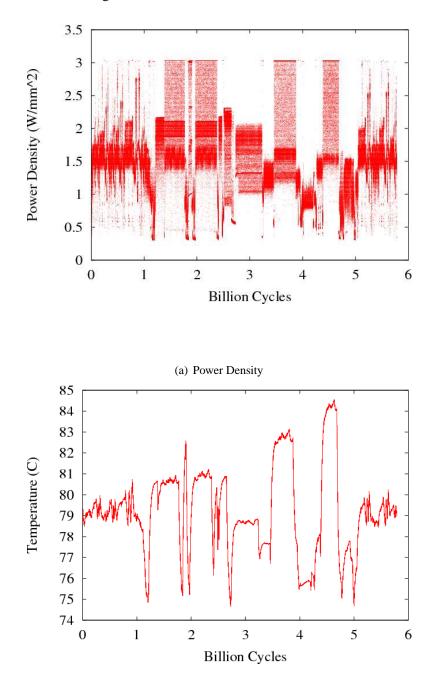

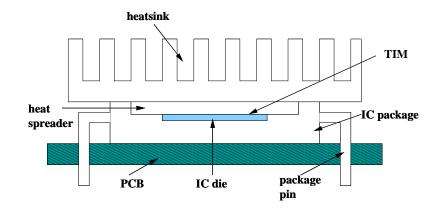

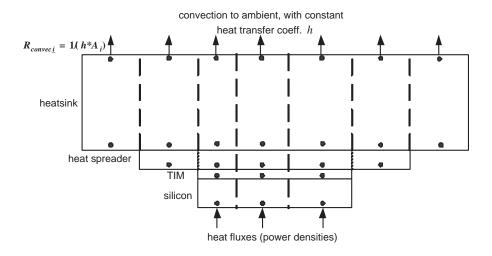

Chips today are typically packaged with the die placed against a spreader plate, often made of aluminum, copper, or some other highly conductive material, which is in turn attached to a heat sink of aluminum or copper through a Thermal Interface Material (TIM). The heat sink is cooled by a fan. HotSpot takes this into account and models the heat flow through such a typical cooling solution. An example of the configuration modeled by HotSpot is shown in Figure 2.3. Low-power/low-cost chips often omit the heat spreader and sometimes even the heat sink; and mobile devices often use heat pipes and other packaging that avoid the weight and size of a heat sink.

Given the floorplan of a processor and a set of power consumption values for each of its functional blocks, HotSpot first forms a thermal equivalent circuit by discretizing the geometry of the chip in all three dimensions. The topology of the resulting thermal circuit is very similar to the geometry of the chip and the thermal solution that it attempts to model. Each vertical layer of heat conduction (chip, heat sink, spreader, TIM *etc.*) is accounted for by a corresponding layer of circuit nodes connected to the layers immediately above and below it through a set of vertical thermal

Figure 2.3: Side view of a typical package. [104]

resistances. Similarly, within a given layer, the lateral heat conduction is modeled through a network of lateral thermal resistances in both the *x* and *y* directions that connect regions of physical adjacency. For instance, in case of the *block-based* thermal model, this lateral discretization of the silicon layer results in one circuit node per functional block. Blocks adjacent to each other in the floorplan are also correspondingly connected by a lateral thermal resistance in the equivalent thermal circuit. Similarly, for the *grid-based* thermal model, the lateral discretization is uniform, with the silicon die being partitioned into a regular mesh of fixed number rectangular regions. Hence, the number of circuit nodes per layer is equal to the number of partitions. Also, partitions that are physically adjacent in the chip have their corresponding circuit nodes connected to each other in the equivalent circuit.

Since most of the vertical heat conduction through the different layers occurs through the regions directly beneath the die, the regions outside the die in the heat sink and spreader layers are discretized at a much coarser granularity. Specifically, the region of the heat spreader that lies outside the die is divided into four (north, east, south and west) with only one circuit node per region. Similarly, the region of the heat sink outside both the spreader area and the die area is also divided into four. The same holds true for the region of the heat sink that lies beneath the heat spreader but outside the coverage of the die as well. Figure 2.4 illustrates this arrangement through a conceptual view of a thermal solution in HotSpot consisting of TIM, spreader and sink. Each filled circle in the figure denotes a node in the thermal circuit. The power dissipation in silicon is modeled in the thermal circuit as current sources connected to the circuit nodes corresponding to the silicon layer. Similarly, the heat removal at the fins of the heat sink is modeled as a convection resistance computed from the heat transfer co-efficient of the fins. This is shown in the figure through the parallel arrows.

Figure 2.4: A conceptual view of the nodes of the thermal circuit in HotSpot [50]

The vertical and lateral thermal resistances described above only capture the heat conduction behaviour in the steady state. In order to model the transient thermal behaviour, each circuit node is also connected to ground through a thermal capacitance.

With this overview of the finite-element discretization in HotSpot, the final piece that remains in the construction of the equivalent thermal circuit is the computation of the thermal resistance and capacitance values themselves. The vertical and lateral discretizations in HotSpot reduce the heat conduction problem from three dimensions to a single dimension. Finally, in the single- dimensional case, the thermal resistance and capacitance values should be computed in such a manner that the response of the equivalent RC circuit matches closely with the true response of the onedimensional transient thermal conduction problem. It turns out that for a given one-dimensional block of length *t*, cross-sectional area *A*, thermal conductivity  $\kappa$ , specific heat capacity *c* and density  $\rho$ , the thermal resistance *R*<sub>th</sub> and capacitance *C*<sub>th</sub> values are given by:

$$R_{th} = \frac{t}{\kappa \cdot A}$$

$$C_{th} = c \cdot \rho \cdot t \cdot A \qquad (2.1)$$

The thermal equivalent circuit thus constructed is solved by HotSpot using standard circuit solving techniques that are simple yet fast. Since the number of nodes in the *block-based* model tends to be small, HotSpot uses a direct matrix inversion method to solve for its steady-state temperature. However, since the number of nodes in the *grid-based* model is usually large, it employs a more sophisticated multigrid technique [81] which in turn uses an iterative Gauss-Siedel method for steady-state solution. For transient calculation, HotSpot uses an adaptive step-size, fourth order Runge-Kutta method [81]. The reason for the choice of these solvers is that they are simple enough to be implemented and modified easily and efficient enough to be used in real-time microarchitectural simulations. Integration of more efficient off-the-shelf solvers into HotSpot is an area of future work not part of this dissertation.

HotSpot has been validated against two different finite-element solvers, Floworks [37, 103] and ANSYS [4, 50]. It has also been validated against actual measurements from a test chip [52, 108] and a Field-Programmable Gate Array (FPGA) [112].

For the kind of studies in this dissertation, the thermal model must have the following properties. It must track temperatures at the granularity of individual microarchitectural units. It must be parameterized, in the sense that a new network of Rs and Cs is automatically generated for different microarchitectures. It must be portable, making it easy to use with a range of power/performance simulators. It must be able to solve the RC-circuit's differential equations quickly. It must be calibrated so that simulated temperatures can be expected to correspond to what would be observed in real hardware. The HotSpot model meets all these conditions. It is a software that provides an interface for specifying some basic information about the thermal solution and for specifying any floorplan that corresponds to the architectural blocks' layout. HotSpot then generates the equivalent RC circuit automatically, and supplied with power dissipation over any chosen time step, computes

temperatures of each block of interest. It is efficient and extensible, making it a correct fit for the microarchitectural thermal studies of this dissertation.

HotSpot is a group effort that has involved many people. Apart from our professors (Skadron and Stan), acknowledgements are due to Wei Huang, Shougata Ghosh, Siva Velusamy and David Tarjan. Particularly, a majority of the modeling work and model validation are contributions of Wei Huang. My role, as one of the two primary contributors, has been in the design and implementation of the software, including feature enhancements (*e.g.* the ability to model a configuration without the heat sink or heat spreader), accuracy enhancements (of both the *block-based* and *grid-based* models), performance enhancements of the solvers (*e.g.* adaptive step sizing of the transient solver and the multigrid technique for the steady-state solver) and usability improvements (*e.g.* support for integration with other simulators, cleaner interfaces *etc.*). Furthermore, my contributions also include analytical reasoning of modeling granularity and capacitance fitting factors and some model validation using the ANSYS tool.

### 2.5 Analytical Choice of Parameters

#### 2.5.1 Lumped Capacitance Scaling Factor

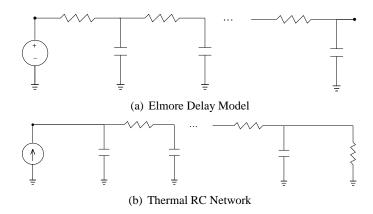

Figure 2.5: Illustration of the RC networks corresponding to the Elmore delay model and the equivalent circuit for thermal conduction.

It was mentioned in the last section that the three-dimensional discretization in HotSpot reduces the heat conduction problem to a single dimension. However, care has to be taken to ensure that the equivalent RC approach in one dimension matches closely with the true thermal response. As a distributed RC network, the transient solution of the true thermal response is an infinite series of exponentials while that of a lumped RC is a single exponential. The common practice of calculating the lumped RC values is to use the Elmore delay model [34], as a result of which, a scaling factor of 50% is typically used. However, the Elmore delay model assumes a distributed RC network that is slightly different from the equivalent thermal RC network. Figure 2.5 illustrates both these networks. Figure 2.5(a) shows a network corresponding to the Elmore delay model while Figure 2.5(b) shows a network equivalent to thermal conduction. The Elmore delay model has a voltage source at its input while the thermal model has a current source. Moreover, the output terminal of the Elmore delay model is open while that of the thermal model is connected to ground. Hence, the 50% scaling factor from the Elmore delay model is not directly applicable in the thermal case. Instead, the principle of its derivation should be applied to the problem at hand (in this case, one-dimensional transient thermal conduction) in order to calculate the appropriate scaling factor. One of my contributions to the HotSpot model is the derivation of such an approach for the thermal conduction problem.

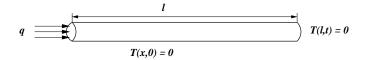

Figure 2.6: A transient thermal conduction problem equivalent to HotSpot's RC network with a single node.

Let us consider the transient thermal conduction problem in one dimension with boundary conditions similar to those found in HotSpot. We are interested in the case similar to Figure 2.5(b) where the input node of a thermal circuit is supplied by a current source and is connected to ground through a thermal distributed RC line. Figure 2.6 shows an equivalent thermal situation. A thin rod of length *l*, which is insulated on the sides, has one end at zero temperature while the other end is supplied with a heat flux (power density) *q*. Let the thermal conductivity of the material of the rod be  $\kappa$ , its thermal capacitance be *c* and its density be  $\rho$ . Then, if the transient temperature of the rod at distance *x* from the left end at time *t* is denoted by T(x,t), then the one-dimensional transient thermal conduction equation that describes this system is given by [17]:

$$\frac{\partial T}{\partial t} = \frac{\kappa}{c\rho} \frac{\partial^2 T}{\partial x^2}$$

(2.2)

subject to:

$$T(l,t) = 0 \tag{2.3}$$

$$T(x,0) = 0$$

(2.4)

$$\frac{\partial T}{\partial x}\Big|_{x=0} = -\frac{q}{\kappa} \tag{2.5}$$

The solution for the above equation and boundary conditions can be obtained from [17]. Note that we are only interested in the temperature at x = 0 or T(0,t). For simplicity of notation, let us define the normalized temperature  $T_{norm}$  to be  $\frac{T(0,t)}{T(0,\infty)}$ . Then, the expression for  $T_{norm}$  can be calculated as:

$$T_{norm} = 1 - \frac{8}{\pi^2} \sum_{n=1,3,5,\dots} \frac{e^{-n^2 \frac{\pi^2}{4} \frac{t}{RC}}}{n^2}$$

(2.6)

where,  $RC = \frac{c\rho l^2}{\kappa}$  or

$$R = \frac{1}{\kappa} \cdot \frac{l}{A} \quad and \quad C = c \cdot \rho \cdot l \cdot A \tag{2.7}$$

*i.e. R* and *C* are the same as equivalent thermal resistances  $R_{th}$  and  $C_{th}$  mentioned in equation 2.1. Now, we seek to approximate  $T_{norm}$  by an equivalent RC pair. Let us say that the time constant of that RC pair be  $\tau$ . The response for an RC pair is given by  $1 - e^{\frac{-t}{\tau}}$ . Clearly,  $T_{norm}$  is an infinite sum of exponentials while the response of an RC pair is a single exponential. Hence, an exact match is not possible. However, taking cue from the Elmore delay model, since both expressions are exponentials going from 0 to 1, we can seek that the area *above* their curves match (since the area *under* them is infinity). In other words, we could seek that the integrals of  $1 - T_{norm}$  and

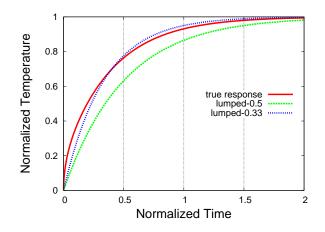

Figure 2.7: Distributed vs. lumped thermal response.

$1 - (1 - e^{\frac{-t}{\tau}}) = e^{\frac{-t}{\tau}}$  match. It can be seen that the latter integral (from 0 to  $\infty$ ) is equal to  $\tau$ . So, we get

$$\tau = \frac{8}{\pi^2} \int_0^\infty \sum_{n=1,3,5,\dots} \frac{e^{-n^2 \frac{\pi^2}{4} \frac{t}{RC}}}{n^2} dt$$

=  $\frac{32 \cdot RC}{\pi^4} \sum_{n=1,3,5,\dots} \frac{1}{n^4}$

=  $\frac{RC}{3}$  (2.8)

since  $\sum_{n=1,3,5,...,\frac{1}{n^4}} = \frac{\pi^4}{96}$  from [1].

Thus, the scaling factor for the lumped capacitance turns out to be  $\frac{1}{3}$ . Figure 2.7 shows this experimentally. It plots the true thermal response ( $T_{norm}$ ) and the lumped responses with scaling factors of 0.5 and  $\frac{1}{3}$  respectively. It is evident that the scaling factor of 0.33 offers a better match.

#### 2.5.2 Convection Capacitance

We saw in Section 2.4 from Figure 2.4 that HotSpot models the convection heat removal at the fins of the heat sink using a convection resistance. For a convection heat transfer co-efficient *h* and area of convection *A* (which is nothing but the area of the top face of the heat sink), the resistance  $R_{convec}$ is calculated as  $\frac{1}{h\cdot A}$ . In order to model the transient behaviour of the heat removal due to convection, HotSpot also includes a convection capacitance  $C_{convec}$ . This section throws more light on how the value of  $C_{convec}$  is computed in HotSpot.

The rate of heat transfer due to convection from a given surface to an ambient temperature  $T_{amb}$  is directly proportional to the difference in temperature between the surface and  $T_{amb}$  [56]. The constant of proportionality is called the heat transfer co-efficient *h*. To compute the lumped capacitance  $C_{convec}$  at the heat sink, we can use this principle in conjunction with the law of conservation of energy. Assuming the average temperature of the surface is *T*, the rate of heat lost due to convection is the same as the rate of decrease in temperature multiplied by the bulk thermal mass *m* and the specific heat capacity *c i.e.*,

$$mc\frac{dT}{dt} = -hA(T - T_{amb})$$

(2.9)

Solving this differential equation for an initial condition of  $T = T_0$  at t = 0, we get

$$T = T_{amb} + (T_0 - T_{amb}) \cdot e^{-\frac{hAt}{mc}}$$

$$\tag{2.10}$$

Hence, the thermal time constant  $R_{convec} \cdot C_{convec}$  is  $\frac{mc}{hA}$ . In other words, if  $R_{convec}$  is  $\frac{1}{hA}$ , then  $C_{convec} = mc$ . For a typical configuration in HotSpot, most of the bulk thermal mass is from the heat sink. The mass of the heat spreader is about  $\frac{1}{28}^{th}$  of that of the heat sink and the mass of the silicon die is about  $\frac{1}{48}^{th}$  of that of the heat spreader. Hence, we can safely assume that the bulk thermal mass m is the mass of copper (heat sink and heat spreader). Hence, for the default configuration of HotSpot, with c denoting the specific heat capacity of copper, we get  $C_{convec} = mc = 91.377 \frac{J}{K}$ . However, since all capacitances are scaled by the scaling factor derived in the previous section (0.33), this value has to be divided by the same value to compensate for scaling. Hence, the default  $C_{convec}$  value for HotSpot is 274.131  $\frac{J}{K}$ .

#### 2.6 Empirical Leakage Model

The leakage power consumed even when circuits are idle and not switching has an important relationship with temperature. Firstly, it increases exponentially with temperature. Secondly, its increase causes higher power density, resulting in even higher temperature and so on. Such a reinforcing feedback loop could, in extreme conditions, lead to catastrophic failure due to thermal runaway. Hence, in a study such as this dissertation involving the thermal management of microprocessors, it is important to consider the relationship of leakage power to temperature accurately. Hence, this section presents an empirical model that captures the most important factors in the relationship between leakage and temperature.

We begin with the BSIM3 v3.2 device model [61] for the drain current of a MOSFET transistor. Ignoring the effects of Drain-Induced Barrier Lowering (DIBL), assuming that the supply voltage is much greater than the threshold voltage and grouping parameters that remain constant for a given technology [119], we get,

$$I_D = K_1 \cdot T^2 e^{\frac{q}{k_{\Pi}} (\frac{V_{GS} - V_T - V_{off}}{T})}$$

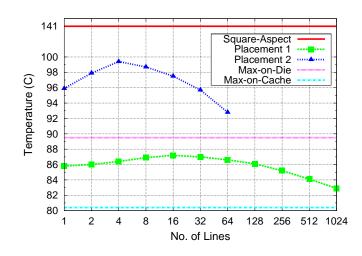

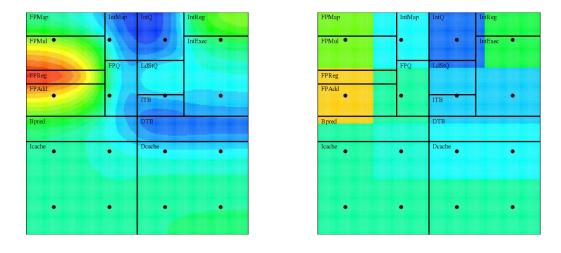

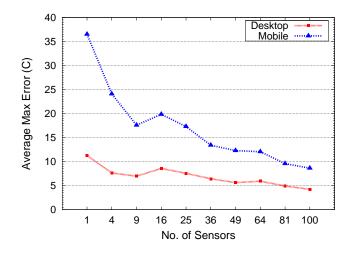

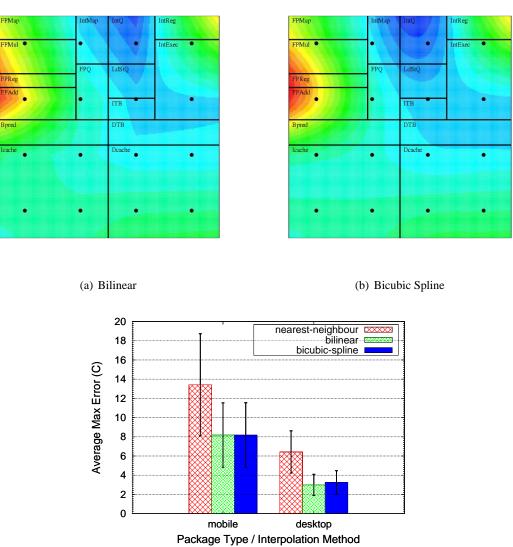

(2.11)