This page does not represent the most current semester of this course; it is present merely as an archive.

CS:aPP §4.2.5 says a little about how a clock signal causes hardware registers to store data. It is worth saying more about this idea.

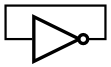

Consider a simple counter. The bottom bit of the counter should switch 1, 0, 1, 0, 1, 0, and so on. We can write this logic as bit0 = ~bit0. The simplest hardware for that would be an inverter with its input as it's output:

But in the hardware, an inverter with its output as its input is not stable in part because it takes a not-quite-deterministic amount of time for the output wire to react to a change in the voltage on the input wire.

To make a reliable count we add a hardware register between the input and output.

Now when the register's output (Q) is low voltage (0) the inverter produces a high voltage (1) on its output, but the register ignores its input (D) until a rising clock edge. On that rising clock edge the register stores its input (D) which is a high voltage (1) and produces it as its output (Q) until the next rising clock edge. Before that next clock edge the inverter will have changed from outputing high voltage to outputing low voltage and the desired 0-1 oscillation will be achieved.

If the clock cycles too quickly then the signal from the old register values will not have time to propagate all the way to the register inputs before the next rising clock edge. That will mean the resisters might store the wrong inputs, leading to incorrect behavior.

The potential for incorrect behavior is one of the potential problems with overclocking a computer chip. Other problems include an increase in heat production (heat = voltage × current; the voltage of a chip is roughly constant but the current scales with the number of times voltages change per second), decreased performance at higher temperatures, and the potential for clock signals to reach different parts of the chip at different times.