# An Interactive Gate-Level Simulator of a Classical Von Neumann Architecture, as an Educational Aid for Introducing Novices to the Fundamentals of Computer Organization

Gabriel Robins

Computer Science Department University of California, Los Angeles Los Angeles, California 90025

# 1. Abstract

I have developed an interactive tool for the simulation of a classical Von Neumann computer architecture. The simulation takes place at the register, bus, and gate level. The simulated system consists of 9 registers, 4 buses, 40 gates, an adder, a memory, a micro-programmed control subsystem, a 3-phase clock, a "scratch" register, logical inverters, a bi-directional shift register, several constant registers, and zero-detect logic. A friendly user interface was also implemented, featuring an assembler, a microcode interpreter, and a terminal-independent full-screen display facility. My simulator prototype could effectively be used as an educational tool for the introduction of novices to the fundamentals of computer organization. Alternatively, the construction of such a simulator may in itself constitute a good term project for an upper division hardware course.

Keywords: Computer organization, simulation, learning tools, computer hardware, educational aids, user training systems.

#### 2. Introduction

We have developed an interactive tool for the simulation of a classical von Neumann computer architecture. The simulation takes place at the register, bus, and gate level. The components of our system include 9 registers, 4 buses, 40 gates, 1 adder, a memory, a micro-programmed control subsystem, a 3-phase clock, an extra "scratch" register, logical inverters, a bi-directional shift register, several constant registers, and zerodetect logic. In addition, we have constructed a friendly user interface, featuring an assembler, a microcode interpreter, and a terminal-independent full-screen display facility. There exists a distinct lack of software tools to aid and enhance the teaching of computer science at the undergraduate level. We believe that our interactive simulator prototype constitutes an extremely useful educational tool for the introduction of novices to the fundamentals of computer organization. The architecture we consider is based on the one discussed in [Tanenbaum].

# 3. Overview

This simulator requires 3 specification: the micro-code, the assembly instruction set, and the user program. When the simulator starts running, it loads the micro-program into the micro-store; next, it reads and assembles the user program into machine language, according to the instruction set specified (or else the default assembly instruction set). The resulting machine program is loaded into the main memory of the simulator. The simulator then begins to execute the micro-program; the micro-program, in turn, fetches, decodes, and executes instructions of the machine-language program.

By programming the simulator in micro-code, the user may thus create new and novel "instruction sets" for the "machine." For example, suppose the user wanted to add an assembly instruction "sqrt" which takes the integer squareroot of the ACC register and leaves the result in the ACC register. The user will then need to add a new opcode called "sqrt" (and a corresponding machine-instruction code) to the assembly instruction set of the machine (by updating that file), and next modify the micro-program to perform the square root operation on the ACC register whenever the new instruction is encountered. The organization of the rest of this paper is as follows: section 4 describes the details of the simulated hardware, section 5 describes the assembler and the assembly language, section 6 describes the microcode interpreter and its language, section 7 discusses the user interface, and section 8 summarizes the implementation and explains how to obtain the source code.

#### 4. The Hardware

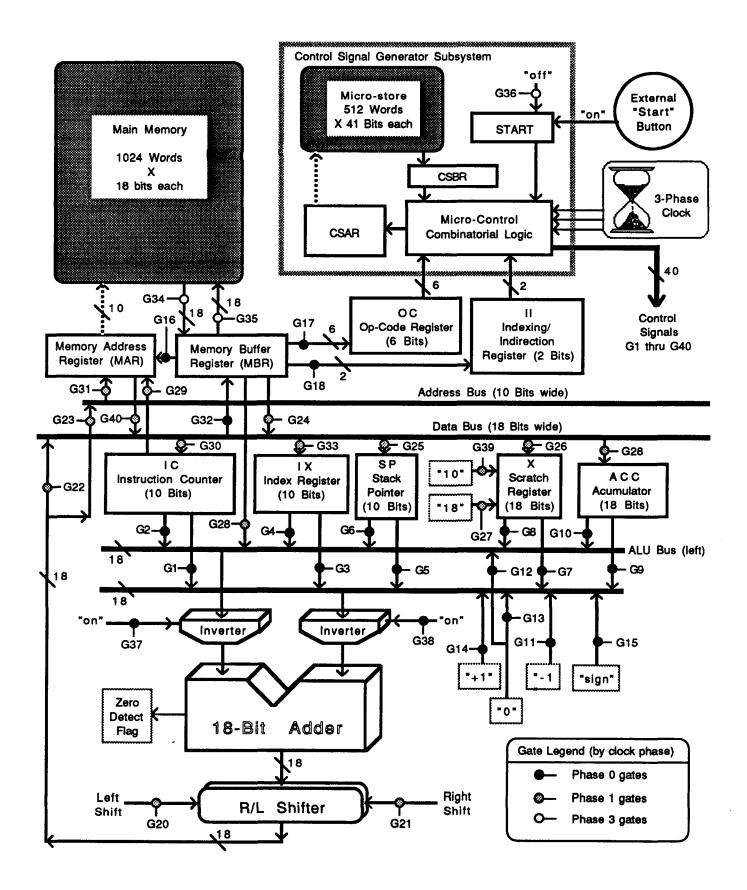

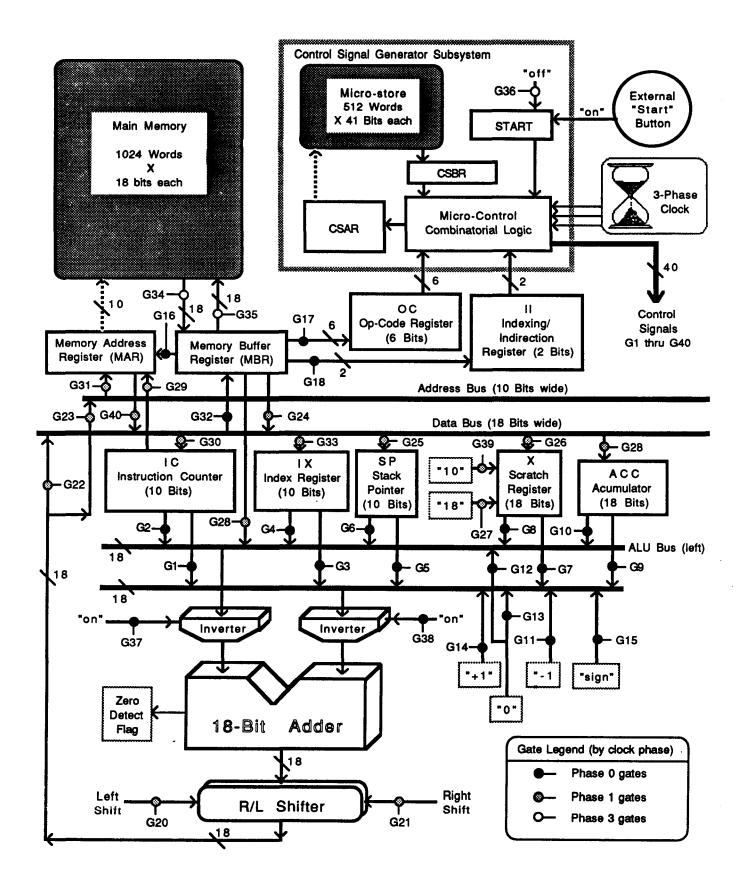

The computer system we chose to simulate is a simplified von Neumann-type single-processor micro-program controlled machine. The schematic organization of this system is given in Appendix II. A detailed description of the components and topology of the system follows. Unless otherwise specified, when two registers/buses with different numbers of bits are connected, say m and n where m > n, the connection consists of bits 0 through n-1 of the first register/bus being connected to bits 0 through n-1 of the second register/bus. The rest of the m-n connections are connected to logical low (0).

### 4.1. Registers

<u>IC</u> - a 10-bit used as the <u>instruction counter</u> for the user's program.

**IX** - a 10-bit register used as the <u>index register</u> by user programs for array-type addressing.

<u>SP</u> - a 10-bit register used as a <u>stack pointer</u> for call/return instructions as well as for arbitrary push/pop operations.

$\underline{X}$  - an 18-bit register used as a <u>scratch register</u> in various micro-instructions, and is invisible to the assembly -language program.

<u>ACC</u> - an 18-bit register which serves as an "accumulator" in the user's program.

$\underline{MAR}$  - a 10-bit register used primarily to store the address of where main memory is going to be written into or read from. It may also be used as a scratch register by the micro-program.

<u>MBR</u> - an 18-bit used to store the data involved in all memory read/write operations.

<u>OC</u> - a 6-bit register used to store the <u>op-code</u> of the currently executed macro-instruction.

**II** - a 2-bit register used to store the indexing/indirection flags of the currently executing assembly instruction.

# 4.2. Buses

**Data bus** - an 18-bit bi-directional bus that is connected to the various registers and to the adder

output lines. Most movement of data between registers takes place via the data bus.

<u>Address bus</u> - a 10-bit bi-directional bus that is connected to the MAR register and to the adder output bus. This bus is used to supply the MAR register with the address of memory locations in read/write operations.

Left adder bus - an 18-bit bus that connects the various registers and several constant registers with the left input to the adder module.

<u>**Right adder bus**</u> - an 18-bit bus that connects the various registers and several constant registers with the right input to the adder module.

#### 4.3. Gates

There are 40 distinct gates, each, when open, initiates a micro-operation. Any number of gates may be open at the same time, but some combinations of gates are mutually exclusive (ex: left-shift and right-shift). The hardware diagram in Appendix II specifies which gates open what hardware connections.

### 4.4. Memory

The main memory consists of 1024 words of 18 bits each. The memory locations have addresses in the range 0 through 1023, inclusive. Each word has its bits numbered 0 through 17, inclusive, where bit 0 is considered to be the least significant when numeric values are represented.

#### 4.5. Inverters

There is a single logical inverter between each of the adder left and right buses, and the adder. These may invert none, one, or both arguments to the adder, depending on whether neither, one, or both are enabled.

#### 4.6. Adder

There is an 18-bit adder whose inputs are the outputs of the inverters. At each clock cycle, the adder (which consists of solid-state combinatorial logic) sums its inputs and outputs the answer to its output.

# 4.7. Shifter

There is a single bi-directional shift register between the adder output and the data and address buses. It may shift the adder output by one bit to either left or right, depending on whether it is enabled.

# 4.8. Zero-detect logic

After each addition operation of the adder, the zero-detect logic resets or presets a bit that can be later tested for branching purposes. The zero-detect logic is set to '1' if the last addition resulted in a zero answer, and to '0' if the last addition resulted in a non-zero answer.

### 4.9. The Control Subsystem

The micro-programmed control subsystem of the machine is implemented by a control store micro-memory, a CSAR (control store address register) and CSBR (control store data register) registers, and hard-wired micro control logic. This entire subsystem is invisible to the assemblylanguage user.

# 4.9.1. The Micro-memory

The micro-memory consists of 512 words of storage, each of which contains 41 bits. The micro-memory words are numbered 0 through 511, inclusive, while the bits in each micro word are numbered 0 through 40, inclusive.

### 4.9.2. Micro-registers

<u>CSAR</u> - this is a 9-bit register that is used to address the micro-memory. It is similar in function to the MAR register for the main memory. CSAR is an acronym for "Control Store Address Register".

<u>CSBR</u> - this is a 41-bit register that contains the current micro instruction being executed. This register is directly in control of the hard-wired control logic and supervises the opening and closing of control gates (i.e., the generation of control signals) by virtue of the values contained in its bits. CSBR is an acronym for "Control Store Buffer Register".

#### 4.9.3. Control Logic

The control logic for the micro programmed control subsystem is hard-wired (in this simulation it is written in C). It supervises the loading of instructions from the micro-memory, incrementing the CSAR register, and generating the control signals from the value of the CSBR and the clock pulses.

# 4.9.4. Start Toggle

The start toggle is a single bit register that allows the system to commence execution (when high) or causes the entire operation of the system to be suspended (when low). This is used to halt execution of the simulation, so that the user may inspect the contents of various registers/buses.

#### 4.9.5. Clock

The operation of the control subsystem is governed by a three-phase clock. The phases of the clock are numbered P0, P1, and P2. The set of 40 system gates is partitioned into 3 distinct nonempty disjoint subsets, each of which contains gates that can be open ONLY during a unique clock phase. These sets are:

This partition exists in order to eliminate certain nasty ambiguities that arise when several inputs are allowed to to enter into the same register simultaneously, thereby rendering its contents undefined.

# 4.9.6. Micro-Instruction Format

Each micro instruction has one of the two formats specified in Appendix III. In the first format, the only operations that can occur are gates being opened according to which of bits 1 through 40 of the instruction are set high, during the appropriate clock phases. In the second format, a certain bit (specified by bits 10 through 14) of a register (specified by bits 1 through 9) is examined and compared with bit 15 of that instruction. If the comparison was successful (i.e., they were equal), then micro-control is transferred to the microlocation specified by bits 16 through 25 of the instruction. Both the "bit num" and the "address" fields are encoded in binary; the rest of the fields are linearly encoded, and only one of the bits of all of these fields must be set high (the rest being set low) in order for the instruction to logically make sense.

Having the system be micro-programmed

makes it very powerful with respect to non-microprogrammed systems. This is because new userlevel assembly instruction sets can be easily implemented, and only by changing the microprogram, not having to touch the hardware at all. In fact, users may write their own microprograms, thereby taking advantage of higher machine efficiency to suit their particular applications.

# 5. The Assembly Language

This section describes the assembler for the machine. The purpose of the assembler is to "compile" the user's assembly language into machine language and to place the resulting object code into the main memory so that it may be later executed. The reason for having an assembler, is to make the task of programming less tedious for the user; otherwise, the user would have had to program directly in the hardware's binary machine language.

A reasonable instruction set has already been written (and is the default instruction set) in order to accommodate users who do not wish to go through the tedium of writing their own microprograms. Sensible mnemonics were also assigned to the various operations. It should be noted that the assembler is written in a general manner. The opcode mnemonics are read from an external file. and thus subject to modification by the user. The rest of the functions of the assembler remain unchanged from language to language. In fact, the only difference between two assembly languages here is between their two respective opcode mnemonic sets. Appendix IV gives the the mnemonics and their respective opcodes for the default assembly instruction set.

# 5.1. Stack

As can be easily seen, this language has a built-in stack facility for calling functions and for pushing values onto a stack. This makes the language posses substantial versatility. In the micro-program, the stack is rooted at the top of memory (location 1023) and grows toward smaller memory locations.

# 5.2. Instruction Format

The instruction format for this language calls for each instruction to be one word in length, in the format specified in Appendix V.

#### 5.3. Assembly Syntax

This assembler recognizes an assembly language that is in a standard format, where each line of code is composed of one to three fields: label, opcode, and address. The address field may be immediately preceded by the character "" which signified indirection, and succeeded by the two characters '()' which signify indexing. In addition to the default opcodes described earlier, there are three additional pseudo-opcode: the 'equ' opcode, which is used to associate a label with a number/address, the 'con' pseudo-operator, which is used to store data/constants into memory locations during the assembly process, and the 'org' pseudo-operator, used to assemble code into several separate memory regions. A sample assembly program is given in Appendix I.

# 6. The Microcode Interpreter

This section describes the microcode interpreter. The function of the microcode interpreter is to convert the microcode from the symbolic form it is written in, to the form that can be placed into the micro-memory. Alternatively, the microcode would have been coded in binary by the user, which makes for a very tedious and error-prone task.

# 6.1. Microcode Syntax

The micro-program in symbolic form is composed of as many occurrences of the following 40 strings as desired: alu-right=ic, alu-left=ic, alu-right=ix, alu-left=ix, alu-right=sp, aluleft=sp, alu-right=x, alu-left=x, alu-right=acc, alu-left=acc, alu-right=-1, alu-left=0, aluright=0, alu-right=1, alu-right=sign, mar=mbr, oc=mbr, ii=mbr, alu-left=mbr, left-shift, rightshift, data-bus=alu-output, address-bus=aluoutput, data-bus=mbr, sp=data-bus, x=data-bus, x=18, acc=data-bus, mar=ic, ic=data-bus, mar=address-bus, mbr=data-bus, ix=data-bus, mbr=mem(mar), mem(mar)=mbr, start=off, invert-left-alu, invert-right-alu, x=10, databus=mar.

Each set of micro-operations that are specified on ONE input line, will be executed during ONE clock cycle (but maybe in different clock phases). The character ';' is used as a separator and should follow each one of the strings. Labels may be used, and comments are placed between curly brackets. In addition to the micro operations specified above, two more micro-instructions may be specified: the '<u>if</u>' and the '<u>goto</u>'. The 'if' has the following syntax:

#### if(reg,blt)=cmp then goto label;

where '<u>reg</u>' is one of the strings { ic, ix, sp, x, acc, mbr, mar, oc, ii, zero-detect }, '<u>bit</u>' is a decimal number that represents the bit to be tested, '<u>cmp</u>' is either 0 or 1 (the value to be tested against), and '<u>label</u>' is a valid label in the micro-program to be branched to if the test is successful (i.e. reg(bit)=cmp ). The 'goto' microinstruction is much simpler:

#### goto <u>label;</u>

This micro-instruction unconditionally transfers micro-control to the micro-location specified by <u>'label'</u>.

#### 7. The User Interface

#### 7.1. Screen format

The simulator updates the terminal display in a screen-oriented fashion. Direct cursor control is exercised through a library package which is intelligent enough to look up the terminal type in the appropriate UNIX system file. The most current values of the various registers and buses are displayed on the screen at all times, unless the user specified to the simulator to run in the 'quiet' mode. This display makes possible for the user to trace only the specific system components of his/her choice, while possibly ignoring the rest, with minimal cognitive overhead. While the system is running, the display appears as in Appendix VI.

# 7.2. The interaction With the User

All commands are one letter long, which in all cases is the first letter of the word describing the command. A short menu is present at the bottom of the display at all times, summarizing the commands. A help facility makes it possible to review the functions of the commands at any given time. Some commands generate a sub-menu, which contains subcommands appropriate for the original command only.

The various commands that are available at the top-level are: <u>Pause</u> - pauses between clock cycles (or phases), and wait for a new command, <u>Continue</u> - negates the last pause command, <u>Stop</u> - halts the machine, and creates a final memory dump, <u>Quiet</u> - does all things silently without updating the display, <u>Trace</u> - negates the 'quiet' command, <u>Redraw</u> - clears the screen and redraw the display, <u>Values</u> - allows the user to change the contents of registers and buses, <u>Microcode</u> - lists the interpreted microcode, <u>Object</u> - lists the object code of the assembled program, <u>Examine</u> - lists the contents of the entire main memory, <u>Help</u> - print this summary.

# 7.3. Error Handling

The microcode interpreter, as well as the assembler, may produce various diagnostic messages during normal operation. This usually occurs when the user fails to comply with the syntax rules built into the simulator. All such error messages are meant to be self-explanatory. The line number on which the error occurred is included in the error-message, when appropriate. When the microcode contains errors, assembly will not be attempted. When the source program contains errors, execution will not be attempted.

#### 8. The Implementation

The hard-wired part of the control subsystem is written directly in the C language (after all, the simulation has to *end* somewhere). Execution of the microcode is done here and here only. Execution of the microcode commences at micro location 0 and proceeds logically unless "goto" instructions alter the logic flow. The Microcode is assumed to have been assembled and placed into the micro-memory. Execution of the microcode halts only after the microcode instruction 'start=off' has been executed. Each microcode instruction is fetched from the micro-memory, placed into the CSBR register, and combined with the clock pulses to generate control signals that will open various system gates.

As the microcode executes, it will fetch and interpret individual assembly/machine instructions from the user's program in main memory. Appropriate gates will open and close, and the desired effect will be achieved by having the corresponding micro operations take place. The types and effects of the various micro operations are described in earlier sections. To obtain the annotated C-sources constituting the simulator, please contact the author: Gabriel Robins, P.O. Box 8369, Van Nuys, California, 91409-8369, U.S.A.

#### 9. Summary

à.

I have developed an interactive tool for the simulation of a classical Von Neumann computer architecture. The simulation takes place at the register, bus, and gate level, and features a friendly user interface, an assembler, a microcode interpreter, and a terminal-independent full-screen display facility.

There exists a distinct lack of software tools to aid the teaching of computer science at the undergraduate level. I believe that my interactive simulator prototype, or other similar tools, will prove to be useful educational tools for the introduction of novices to the fundamentals of computer organization. Indeed, the construction of such a simulator will in itself constitute a good term project for an upper division hardware course.

# 10. Bibliography

Tanenbaum, S., <u>Structured Computer Organization</u>, Englewood Cliffs, New Jersey, Prentice Hall, 1976.

#### **11.** Appendix I: Usage Examples

#### 11.1. Sample Micro-program

This is part of the default microcode for the simulated machine:

```

{ initialize the instruction counter and stack pointer to 0 }

alu-left=0 ; alu-right=0 ; data-bus=alu-output ; ic=data-bus; sp=data-bus;

{ fetch a macro-instruction from the main memory }

fetch: mar=ic; mbr=mem(mar);

{ transfer the opcode and the indexing and indirection flags and

increment the instruction counter }

oc=mbr; ii=mbr; mar=mbr; alu-left=ic; alu-right=1; data-bus=alu-output; $

ic=data-bus;

{ the following section is a giant 'switch' construct, that decodes the 64

possible opcodes and branches to the appropriate place for the execution

of the corresponding machine instruction }

0-to-63: if bit(oc, 5)=1 then goto 32-to-63;

0-to-31: if bit(oc,4)=1 then goto 16-to-31;

0-to-15: if bit(oc,3)=1 then goto 8-to-15;

0-to-7: if bit(oc,2)=1 then goto 4-to-7;

0-to-3: if bit(oc,1)=1 then goto 2-to-3;

0-to-1: if bit(oc,0)=1 then goto 1-to-1;

{ nop - no operation }

0-to-0: goto fetch;

{------}

{ add - add memory to register }

{-----}

{ see if this instruction requires indexing }

1-to-1: if bit(ii,0)=0 then goto 1-to-1-no-indexing;

{ preform the indexing }

data-bus=mar; x=data-bus;

alu-right=ix; alu-left=x; address-bus=alu-output; mar=address-bus;

{ see if this instruction requires indirection }

1-to-1-no-indexing: if bit(ii,1)=0 then goto 1-to-1-no-indirection;

{ perform the indirection }

mbr=mem(mar);

mar=mbr;

{ fetch the data from memory }

1-to-1-no-indirection: mbr=mem(mar);

alu-left=mbr; alu-right=acc; data-bus=alu-output; acc=data-bus;

goto fetch;

2-to-3: if bit(oc,0)=1 then goto 3-to-3;

```

{-----} { sub - subtract memory from register } {-----} { see if this instruction requires indexing } 2-to-2: if bit(ii,0)=0 then goto 2-to-2-no-indexing; { preform the indexing } data-bus=mar; x=data-bus; alu-right=ix; alu-left=x; address-bus=alu-output; mar=address-bus; { see if this instruction requires indirection } 2-to-2-no-indexing: if bit(ii,1)=0 then goto 2-to-2-no-indirection; { perform the indirection } mbr=mem(mar); mar=mbr; { fetch the data from memory } 2-to-2-no-indirection: mbr=mem(mar); alu-left=mbr; alu-right=0; invert-left-alu; data-bus=alu-output; x=data-bus; alu-left=x; alu-right=1; data-bus=alu-output; x=data-bus; alu-left=x; alu-right=acc; data-bus=alu-output; acc=data-bus; goto fetch; { Most of the micro-program is omitted here for space considerations...} {-----} { hlt - halt the machine } {------} 63-to-63: start=off; goto fetch; end

#### 11.2. Sample Assembly Program

{ This program generates the first 25 Fibonacci numbers and places them in an array in memory locations 50 thru 74 }

| max<br>array<br>acc<br>ix | equ 0<br>equ 2                                                               | <pre>{ number of Fibonacci numbers we want } { array begins at 50 } { defines the accumulator } { defines the index register } { initialize }</pre>                                                   |

|---------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fibo                      | lda -2()<br>add -1()<br>sta 0()<br>incr ix<br>ldai array<br>addai max        | <pre>{ get the Nth-2 Fibonacci number } { add to it the Nth-1 Fibonacci number } { store the result into the array } { increment the index } {} {} {} { see if we have enough Fibonacci nums } </pre> |

| init                      | subar ix<br>janz fibo<br>hlt<br>org 100<br>ldai array<br>ldixr acc<br>ldai 1 | <pre>{} { if not, go generate some more } { stop the machine } { place the routine starting at loc 100 } { initialize the array index }</pre>                                                         |

|                           | <pre>sta 0() incr ix sta 0() incr ix ret end</pre>                           | <pre>{ set the 1st Fibonacci number manually } { set the 2nd Fibonacci number manually } { set the array pointer to the 3rd element } { return to the caller } { end of assembly }</pre>              |

Note the computed Fibonacci numbers beginning in memory location 50:

| Location: 0 =      | 000000000      | Contents:    | 10000000001100100 = 131172           |

|--------------------|----------------|--------------|--------------------------------------|

| Location: 1 =      | 000000001      | Contents:    | 00001101111111110 = 14334            |

| Location: 2 =      | 000000010      | Contents:    | 00000101111111111 = 6143             |

| Location: 3 =      | 000000011      | Contents:    | 00010001000000000 = 17408            |

|                    | 000000100      | Contents:    | 00010100000000010 = 20482            |

| Location: 5 =      | 000000101      | Contents:    | 100101000000110010 = 151602          |

| Location: 6 =      | 000000110      | Contents:    | 00011100000011001 = 28697            |

| Location: 7 =      | 000000111      | Contents:    | 00111000000000010 = 57346            |

| Location: 8 =      | 0000001000     | Contents:    | 01110100000000001 = 118785           |

| Location: 9 =      | 0000001001     | Contents:    | 1111110000000000 = 258048            |

| Location: 10 =     | 000001010      | Contents:    | 0000000000000000000 = 0              |

| (intermediate      | locations have | the same val | .ue)                                 |

| Location: 49 =     | 0000110001     | Contents:    | 0000000000000000000 = 0              |

| Location: 50 =     | 0000110010     | Contents:    | 00000000000000001 = 1                |

| Location: 51 =     | 0000110011     | Contents:    | 00000000000000001 = 1                |

| Location: 52 =     | 0000110100     | Contents:    | 000000000000000000000000000000000000 |

| Location: 53 =     | 0000110101     | Contents:    | 00000000000000011 = 3                |

| Location: 54 =     | 0000110110     | Contents:    | 00000000000000101 = 5                |

| Location: 55 =     | 0000110111     | Contents:    | 000000000000000000000000000000000000 |

| Location: 56 =     | 0000111000     | Contents:    | 00000000000001101 = 13               |

| Location: 57 =     | 0000111001     | Contents:    | 00000000000010101 = 21               |

| Location: 58 =     | 0000111010     | Contents:    | 000000000000100010 = 34              |

| Location: 59 =     | 0000111011     | Contents:    | 00000000000110111 = 55               |

| Location: $60 =$   | 0000111100     | Contents:    | 00000000001011001 = 89               |

| Location: $61 =$   | 0000111101     | Contents:    | 00000000010010000 = 144              |

| Location: $62 =$   | 0000111110     | Contents:    | 00000000011101001 = 233              |

| Location: 63 =     | 0000111111     | Contents:    | 00000000101111001 = 377              |

| Location: $64 =$   | 0001000000     | Contents:    | 00000001001100010 = 610              |

| Location: 65 =     | 0001000001     | Contents:    | 00000001111011011 = 987              |

| Location: 66 =     | 0001000010     | Contents:    | 000000011000111101 = 1597            |

| Location: $67 =$   | 0001000011     | Contents:    | 000000101000011000 = 2584            |

| Location: $68 =$   | 0001000100     | Contents:    | 000001000001010101 = 4181            |

| Location: 69 =     | 0001000101     | Contents:    | 000001101001101101 = 6765            |

| Location: $70 =$   | 0001000110     | Contents:    | 0000000000000000000 = 0              |

| (intermediate      | locations have | the same val | ue)                                  |

|                    | 0001100011     |              | 0000000000000000000 = 0              |

|                    | 0001100100     | Contents:    | 100101000000110010 = 151602          |

|                    | 0001100101     | Contents:    | 0100100000000000 = 73728             |

| Location: $102 =$  | 0001100110     | Contents:    | 10010100000000001 = 151553           |

|                    | 0001100111     | Contents:    | 00010001000000000 = 17408            |

|                    | 0001101000     | Contents:    | 00010100000000010 = 20482            |

|                    | 0001101001     |              | 00010001000000000 = 17408            |

| Location: $106 =$  | 0001101010     |              | 00010100000000010 = 20482            |

| Location: $107 =$  | 0001101011     | Contents:    | 1000010000000000 = 135168            |

| Location: $108 =$  | 0001101100     | Contents:    | 00000000000000000 = 0                |

| (intermediate      | locations have |              |                                      |

| Location: $1022 =$ | 1111111110     |              | 000000000000000000000000000000000000 |

| Location: $1023 =$ | 1111111111     | Contents:    | 00000000000000001 = 1                |

|                    |                |              |                                      |

# 12. Appendix II: The Hardware Diagram

ŝ

# 13. Appendix III: The Microcode Instruction Format

(II) The TEST micro-instruction:

| [ | 0 | ю | IX | SP | х | ACC | MBR | MAR | œ | Ш | bit num | cmp | address | zd | unused |

|---|---|---|----|----|---|-----|-----|-----|---|---|---------|-----|---------|----|--------|

|   | 0 | 1 | 2  | 3  | 4 | 5   | 6   | 7   | 8 | 9 | 1014    | 15  | 1625    | 26 | 2740   |

14. Appendix IV: The Default Assembly Instruction Set

| op num | mnemonic         | binary code | effect of operation                  |

|--------|------------------|-------------|--------------------------------------|

| •      |                  | 00000       |                                      |

| 0      | nop              | 000000      | no operation                         |

| 1      | add              | 000001      | add memory to register acc           |

| 2      | sub              | 000010      | subtract memory from register acc    |

| 3      | lda              | 000011      | load memory into register acc        |

| 4      | sta              | 000100      | store register acc into memory       |

| 5      | incr             | 000101      | increment register                   |

| 6      | decr             | 000110      | decrement register                   |

| 7      | addai            | 000111      | add to register acc immediate        |

| 8      | subai            | 001000      | subtract from register acc immediate |

| 9      | addixi           | 001001      | add to ix immediate                  |

| 10     | subixi           | 001010      | subtract from ix immediate           |

| 11     | addspi           | 001011      | add to sp immediate                  |

| 12     | subspi           | 001100      | subtract from sp immediate           |

| 13     | addar            | 001101      | add register to acc                  |

| 14     | subar            | 001110      | subtract register from acc           |

| 15     | addixr           | 001111      | add register to ix                   |

| 16     | subixr           | 010000      | subtract register from ix            |

| 17     | ldar             | 010001      | load acc with register               |

| 18     | ldixr            | 010010      | load ix with register                |

| 19     | ldicr            | 010011      | load ic with register                |

| 20     | inva             | 010100      | invert acc                           |

| 21     | invix            | 010101      | invert ix                            |

| 22     | anda             | 010110      | and acc with memory                  |

| 23     | ora              | 010111      | or acc with memory                   |

| 24     | xora             | 011000      | xor acc with memory                  |

| 25     | rsfta            | 011001      | right shift acc                      |

| 26     | Isfta            | 011010      | left shift acc                       |

| 27     | jmp              | 011011      | jump                                 |

| 28     | jaz              | 011100      | jump if acc is zero                  |

| 29     | janz             | 011101      | jump if acc is not zero              |

| 30     | jixz             | 011110      | jump if ix is zero                   |

| 31     | jixnz            | 011111      | jump if ix is not zero               |

| 32     | call             | 100000      | call a subroutine                    |

| 33     | ret              | 100001      | return to caller                     |

| 34     | pusha            | 100010      | push register acc onto stack         |

| 35     | popa             | 100011      | pop acc from stack                   |

|        | <b>•</b> • • • • |             |                                      |

10

| 36 | zeroa | 100100 | zero out the acc   |

|----|-------|--------|--------------------|

| 37 | Idai  | 100101 | load acc immediate |

| 63 | hlt   | 111111 | halt the machine   |

# 15. Appendix V: The Assembly Instruction Format

| operation code |   |   | indirection | indexing | address of operand |   |

|----------------|---|---|-------------|----------|--------------------|---|

| 17             | 1 | 2 | 11          | 10       | 9                  | 0 |

Bit 11, when on, causes indirection to occur. Bit 10, when on, causes indexing to occur via the IX register. Indexing takes precedence over indirection.

# 16. Appendix VI: The Main Display

| Computer-Simulation-b                    | yGabriel-Robins                | version-3-of-7/26/88                    |

|------------------------------------------|--------------------------------|-----------------------------------------|

| ACC=000 1000 10 100 10 1 1 1 1 = 177 1 1 | DATA-BUS=0                     | 000000000000000000000000000000000000000 |

| MBR=000 1000 10000000000 = 17408         | RDDRESS-BUS=0                  | 00000000=0                              |

| MAR=0000000000=0                         | ALU-LEFT-BUS=0                 | 000000000000000000000000000000000000000 |

| I C=0000000 1 1=3                        | ALU-RIGHT-BUS=0                | 000000000000000000000000000000000000000 |

| open gates: 2 14 16 17 18                |                                |                                         |

| micro-ops: alu-left=ic; alu-             | right=1; mar=mbr; c            | oc=mbr; ii=mbr;                         |

|                                          | **=======                      | CLOCK-PHASE=0                           |

| 0C=000100=4 i i =01=1                    | Micro Program<br>Control Logic | START=off pausing                       |

| CSAR=0000000011=3                        |                                |                                         |

| CSBR= 10 10000000000 10 1 1 1000 10      | 000000 10000000000             | SP=0000000000=0                         |

| X=00000000111111111111                   | type=GRTE                      | I X=000 1000 1 1 1=7 1                  |

|                                          |                                |                                         |

-Pause-Continue-Stop-Quiet-Trace-Redraw-Values-Microcode-Object-Examine-Help--

# 17. Table of Contents

| 1Abstract                                            |   |

|------------------------------------------------------|---|

| 2Introduction                                        |   |

| 3Overview                                            | 1 |

| 4The Hardware                                        | 2 |

| 4.1Registers                                         | 2 |

| 4.2Buses                                             | 2 |

| 4.3Gates                                             | 2 |

| 4.4Memory                                            | 2 |

| 4.5Inverters                                         | 2 |

| 4.6Adder                                             | 2 |

| 4.7Shifter                                           | 2 |

| 4.8Zero-detect logic                                 | 3 |

| 4.9The Control Subsystem                             |   |

| 4.9.1The Micro-memory                                |   |

| 4.9.2Micro-registers                                 |   |

| 4.9.3Control Logic                                   |   |

| 4.9.4Start Toggle                                    |   |

| 4.9.5Clock                                           |   |

| 4.9.6Micro-Instruction Format                        |   |

| 5The Assembly Language                               |   |

| 5.1Stack                                             |   |

| 5.2Instruction Format                                |   |

| 5.3Assembly Syntax                                   |   |

| 6The Microcode Interpreter.                          |   |

| 6.1Microcode Syntax                                  | 4 |

| 7The User Interface                                  | 5 |

| 7.1Screen format                                     |   |

| 7.2The interaction With the User                     |   |

| 7.3Error Handling                                    |   |

| 8The Implementation                                  |   |

| 9Summary                                             |   |

| 10Bibliography                                       |   |

| 11Appendix I: Usage Examples                         | 6 |

| 11.1Sample Micro-program                             | ñ |

| 11.2Sample Assembly Program                          | 7 |

| 11.3Main Memory Dump                                 | Ŕ |

| 12Appendix II: The Hardware Diagram                  |   |

| 13Appendix III: The Microcode Instruction Format1    |   |

| 14Appendix IV: The Default Assembly Instruction Set1 | ň |

| 15Appendix V: The Assembly Instruction Format        |   |

| 16Appendix VI: The Main Display                      |   |

| 17Table of Contents                                  |   |

|                                                      | 2 |

# An Interactive Gate-Level Simulator<sup>1</sup> of a Classical Von Neumann Architecture, as an Educational Aid for Introducing Novices to the Fundamentals of Computer Organization

#### Gabriel Robins

Computer Science Department University of California, Los Angeles

"Begin at the beginning," said the King very gravely,"and go on till you come to the end; then stop."

#### 1. Abstract

I have developed an interactive tool for the simulation of a classical Von Neumann computer architecture. The simulation takes place at the register, bus, and gate level. The system consists of 9 registers, 4 buses, 40 gates, an adder, a memory, a micro-programmed control subsystem, a 3-phase clock, a "scratch" register, logical inverters, a bi-directional shift register, several constant registers, and zero-detect logic. A friendly user interface has been constructed, featuring an assembler, a microcode interpreter, and a terminal-independent full-screen display facility. My simulator prototype could effectively be used as an educational tool for the introduction of novices to the fundamentals of computer organization. Alternatively, the construction of such a simulator may in itself constitute a good term project for an upper division hardware course.

Keywords: Computer organization, simulation, learning tools, computer hardware, educational aids, user training systems.

Alice thought to herself, "I don't see how he can ever finish if he doesn't begin."

#### 2. Introduction

We have developed an interactive tool for the simulation of a classical von Neumann computer architecture. The simulation takes place at the register, bus, and gate level. The components of our system include 9 registers, 4 buses, 40 gates, 1 adder, a memory, a micro-programmed control subsystem, a 3-phase clock, an extra "scratch" register, logical inverters, a bi-directional shift register, several constant registers, and zero-detect logic. In addition, we have constructed a friendly user interface, featuring an assembler, a microcode interpreter, and a terminal-independent full-screen display facility.

$<sup>^1</sup>$  "But it isn't old!" Tweedledum cried, in a greater fury than ever. "It's new, I tell you-"  $\mathbbm{C}$  1988, by Gabriel Robins

There exists a distinct lack of software tools to aid and enhance the teaching of computer science at the undergraduate level. We believe that our interactive simulator prototype constitutes an extremely useful educational tool for the introduction of novices to the fundamentals of computer organization. The architecture we consider is based on the one discussed in [Tanenbaum].

# 3. Overview

#### "The Question is," said Alice, "whether you can make words mean so many different things."

This simulator requires 3 specification: the micro-code, the assembly instruction set, and the user program. When the simulator starts running, it loads the micro-program into the micro-store; next, it reads and assembles the user program into machine language, according to the instruction set specified (or else the default assembly instruction set). The resulting machine program is loaded into the main memory of the simulator. The simulator then begins to execute the micro-program; the micro-program, in turn, fetches, decodes, and executes instructions of the machine-language program.

By programming the simulator in micro-code, the user may thus create new and novel "instruction sets" for the "machine." For example, suppose the user wanted to add an assembly instruction "sqrt" which takes the integer square-root of the ACC register and leaves the result in the ACC register. The user will then need to add a new opcode called "sqrt" (and a corresponding machine-instruction code) to the assembly instruction set of the machine (by updating that file), and next modify the micro-program to perform the square root operation on the ACC register whenever the new instruction is encountered.

#### 4. The Hardware

"The time has come," the Walrus said, "to talk of many things."

The computer system we chose to simulate is a simplified von Neumann-type singleprocessor micro-program controlled machine. The schematic organization of this system is given in appendix II. A detailed description of the components and topology of the system follows. Unless otherwise specified, when two registers/buses with different numbers of bits are connected, say m and n where m > n, the connection consists of bits 0 through n-1 of the first register/bus being connected to bits 0 through n-1 of the second register/bus. The rest of the m-n connections are connected to logical low (0).

# 4.1. registers

"Oh!" said Alice. She was too much puzzled to make any other remark.

<u>IC</u> - a 10-bit register whose output is connected to both adder buses, as well as to the MAR register (gates 1, 2, 29, respectively) and whose input is connected to the data bus (gate 30). This register is used as the <u>instruction counter</u> for the user's program.

**IX** - a 10-bit register whose output is connected to both adder buses (gates 3, 4) and whose input is connected to data bus (gate 33). This register is used as the <u>index register</u> by user programs for array-type addressing.

<u>SP</u> - a 10-bit register whose output is connected to both adder buses (gates 5, 6) and whose input is connected to the data-bus (gate 25). This register is used as a <u>stack pointer</u> for call/return instructions as well as for arbitrary push/pop operations.

$\underline{X}$  - an 18-bit register whose output is connected to both adder buses (gates 7, 8) and whose input is connected to the data bus, as well as to two constant registers "10" and "18" (gates 26, 39, 27, respectively). This register is only used as a <u>scratch register</u> in various micro-instructions, and is invisible to the assembly -language program.

<u>ACC</u> - an 18-bit register whose output is connected to both adder buses (gates 9, 10) and whose input is connected to the data bus (gate 28). This register is used in all arithmetic and logical operations, and serves as an "accumulator" in the user's program.

<u>MAR</u> - a 10-bit register whose output is connected to the data bus and to the memory (gate 40), and whose input is connected to the IC register as well as to the address bus (gates 29, 31, respectively). This register is also known as the <u>memory address register</u>, and is used primarily to store the address of where main memory is going to be written into or read from. It may also be used as a scratch register by the micro-program.

**MBR** - an 18-bit register whose output is connected to the main memory, data-bus, and left adder bus (gates 35, 24, and 19, respectively), and whose input is connected to the memory and to the data bus (gates 34, and 32, respectively). This register is also known as the <u>memory buffer register</u> and is used to store the data involved in all memory read/write operations (i.e., it contains the data to be read/written from/into a memory location referenced by register MAR).

<u>OC</u> - a 6-bit register whose output is directly connected to the micro-programmed control subsystem, and whose input is connected to the MBR register (gate 17). This register is used to store the <u>op-code</u> of the currently executed macro-instruction.

<u>II</u> - a 2-bit register whose output is directly connected to the micro-programmed control subsystem, and whose input is connected to the MBR register's bits 10 through 11 (gate 18). This register is used to store the <u>indexing/indirection</u> flags of the currently executing assembly instruction.

4.2. Buses

"Would you tell me please," said Alice, "what that means?"

<u>Data bus</u> - an 18-bit bi-directional bus that is connected to the various registers and to the adder output lines. Most movement of data between registers takes place via the data bus.

<u>Address bus</u> - a 10-bit bi-directional bus that is connected to the MAR register and to the addre output bus. This bus is used to supply the MAR register with the address of memory locations in read/write operations.

<u>Left adder bus</u> - an 18-bit bus that connects the various registers and several constant registers with the left input to the adder module. This bus is used to supply the adder with its left argument.

<u>**Right adder bus</u>** - an 18-bit bus that connects the various registers and several constant registers with the right input to the adder module. This bus is used to supply the adder with its right argument.</u>

4.3. Gates

Fellenser

"I don't understand you," said Alice. "Its dreadfully confusing!"

There are 40 distinct gates, each, when open, initiates a micro-operation. Any number of gates may be open at the same time, but some combinations of gates are mutually exclusive (ex: left-shift and right-shift). A summary of the various gates and the micro operations they initiate follows:

1. alu-right = ic2. alu-left = icalu-right = ix3. 4. alu-left = ix5. alu-right = sp6. alu-left = spalu-right = x7. 8. alu-left = xalu-right = acc9. 10. alu-left = acc11. alu-right = -112. alu-left = 013. alu-right = 014. alu-right = 115. alu-right = sign 16. mar = mbr17. oc = mbr18. ii = mbr19. alu-left = mbr 20. left-shift 21. right-shift 22. data-bus = alu-output 23. address-bus = alu-output 24. data-bus = mbr25. sp = data-bus26. x = data-bus

27. x = 1828. acc = data-bus 29. mar = ic30. ic = data-bus 31. mar = address-bus 32. mbr = data-bus 33. ix = data-bus 34. mbr = mem(mar)35. mem(mar) = mbr36. start = off37. invert-left-alu 38. invert-right-alu 39. x = 1040. data-bus = mar

#### 4.4. Memory

"It's a poor sort of memory that only works backwards," the Queen remarked.

The main memory consists of 1024 words of 18 bits each. The memory locations have addresses in the range 0 through 1023, inclusive. Each word has its bits numbered 0 through 17, inclusive, where bit 0 is considered to be the least significant when numeric values are represented.

#### 4.5. Inverters

There is a single logical inverter between each of the adder left and right buses, and the adder. These may invert none, one, or both arguments to the adder, depending on whether neither, one, or both are enabled.

# 4.6. Adder

"Can you do Addition?" the White Queen asked. "What's one and one?" "I don't know," said Alice. "I lost count." "She can't do Addition," the Red Queen interrupted.

There is an 18-bit adder whose inputs are the outputs of the inverters. At each clock cycle, the adder (which consists of solid-state combinatorial logic) sums its inputs and outputs the answer to its output.

#### 4.7. Shifter

There is a single bi-directional shift register between the adder output and the data and address buses. It may shift the adder output by one bit to either left or right, depending on

whether it is enabled.

#### 4.8. Zero-detect logic

After each addition operation of the adder, the zero-detect logic resets or presets a bit that can be later tested for branching purposes. The zero-detect logic is set to '1' if the last addition resulted in a zero answer, and to '0' if the last addition resulted in a non-zero answer.

#### 4.9. The Control Subsystem

Alice remained looking thoughtfully at the mushroom for a minute, trying to make out which were the two sides of it; and, as it were perfectly round, she found this a very difficult question.

The micro-programmed control subsystem of the machine is implemented by a control store micro-memory, a CSAR (control store address register) and CSBR (control store data register) registers, and hard-wired micro control logic. This entire subsystem is invisible to the assembly-language user.

### 4.9.1. The Micro-memory

"-But there's one great advantage in it, that one's memory works both ways."

The micro-memory consists of 512 words of storage, each of which contains 41 bits. The micro-memory words are numbered 0 through 511, inclusive, while the bits in each micro word are numbered 0 through 40, inclusive.

# 4.9.2. Micro-registers

#### "And now which is which?" she said to herself

<u>CSAR</u> - this is a 9-bit register that is used to address the micro-memory. It is similar in function to the MAR register for the main memory. CSAR is an acronym for "Control Store Address Register".

<u>CSBR</u> - this is a 41-bit register that contains the current micro instruction being executed. This register is directly in control of the hard-wired control logic and supervises the opening and closing of control gates (i.e., the generation of control signals) by virtue of the values contained in its bits. CSBR is an acronym for "Control Store Buffer Register".

# 4.9.3. Control Logic

The control logic for the micro programmed control subsystem is hard-wired (in this simulation it is written in C). It supervises the loading of instructions from the micro-

memory, incrementing the CSAR register, and generating the control signals from the value of the CSBR and the clock pulses.

# 4.9.4. Start Toggle

"I know something interesting is sure to happen," she said to herself

The start toggle is a single bit register that allows the system to commence execution (when high) or causes the entire operation of the system to be suspended (when low). This is used to halt execution of the simulation, so that the user may inspect the contents of various registers/buses.

# 4.9.5. Clock

The operation of the control subsystem is governed by a three-phase clock. The phases of the clock are numbered P0, P1, and P2. The set of 40 system gates is partitioned into 3 distinct non-empty disjoint subsets, each of which contains gates that can be open ONLY during a unique clock phase. These sets are:

<u>phase 1 gates</u> = { 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 37, 38 } <u>phase 1 gates</u> = { 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 39, 40 }

<u>phase 3 gates</u> = { 34, 35, 36 }

This partition exists in order to eliminate certain nasty ambiguities that arise when several inputs are allowed to to enter into the same register simultaneously, thereby rendering its contents undefined.

# 4.9.6. Micro-Instruction Format

"You'll get used to it in time," said the Caterpillar;

Each micro instruction has one of the following formats:

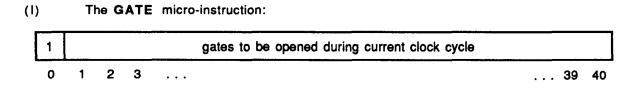

(1) The **GATE** micro-instruction:

| 1 |   |   |   | gates to be opened during current clock cycle |       |

|---|---|---|---|-----------------------------------------------|-------|

| 0 | 1 | 2 | 3 |                                               | 39 40 |

(II) The **TEST** micro-instruction:

| 0 | Ю | IX | SP | x | ACC | MBR | MAR | 8 | 11 | bit num | cmp | address | zd | unused |

|---|---|----|----|---|-----|-----|-----|---|----|---------|-----|---------|----|--------|

| 0 | 1 | 2  | 3  | 4 | 5   | 6   | 7   | 8 | 9  | 1014    | 15  | 1625    | 26 | 2740   |

In the first format, the only operations that can occur are gates being opened according to which of bits 1 through 40 of the instruction are set high, during the appropriate clock phases.

In the second format, a certain bit (specified by bits 10 through 14) of a register (specified by bits 1 through 9) is examined and compared with bit 15 of that instruction. If the comparison was successful (i.e., they were equal), then micro-control is transferred to the micro-location specified by bits 16 through 25 of the instruction. Both the "bit num" and the "address" fields are encoded in binary; the rest of the fields are linearly encoded, and only one of the bits of all of these fields must be set high (the rest being set low) in order for the instruction to logically make sense.

Having the system be micro-programmed makes it very powerful with respect to nonmicro-programmed systems. This is because new user-level assembly instruction sets can be easily implemented, and only by changing the micro-program, not having to touch the hardware at all. In fact, users may write their own micro-programs, thereby taking advantage of higher machine efficiency to suit their particular applications.

#### 5. The Assembly Language

The Red Queen shook her head. "you may call it 'nonsense' if you like," she said, "but I've heard nonsense, compared with which that would be as sensible as a dictionary!"

This section describes the assembler for the machine. The purpose of the assembler is to "compile" the user's assembly language into machine language and to place the resulting object code into the main memory so that it may be later executed. The reason for having an assembler, is to make the task of programming less tedious for the user; otherwise, the user would have had to program directly in the hardware's binary machine language.

A reasonable instruction set has already been written (and is the default instruction set) in order to accommodate users who do not wish to go through the tedium of writing their own micro-programs. Sensible mnemonics were also assigned to the various operations. It should be noted that the assembler is written in a general manner. The opcode mnemonics are read from an external file, and thus subject to modification by the user. The rest of the functions of the assembler remain unchanged from language to language. In fact, the only difference between two assembly languages here is between their two respective opcode mnemonic sets.

#### 5.1. Mnemonics

"I can't believe that!" said Alice. "Can't you?" the Queen said in a pitying tone. "Try again: draw a long breath, and shut your eyes."

Here we give the mnemonics and their respective opcodes for the default assembly instruction set.

| op_num | mnemonic | binary code | effect of operation                  |

|--------|----------|-------------|--------------------------------------|

| 0      | nop      | 000000      | no operation                         |

| 1      | add      | 000001      | add memory to register acc           |

| 2      | sub      | 000010      | subtract memory from register acc    |

| 3      | lda      | 000011      | load memory into register acc        |

| 4      | sta      | 000100      | store register acc into memory       |

| 5<br>6 | incr     | 000101      | increment register                   |

| 6      | decr     | 000110      | decrement register                   |

| 7      | addai    | 000111      | add to register acc immediate        |

| 8      | subai    | 001000      | subtract from register acc immediate |

| 9      | addixi   | 001001      | add to ix immediate                  |

| 10     | subixi   | 001010      | subtract from ix immediate           |

| 11     | addspi   | 001011      | add to sp immediate                  |

| 12     | subspi   | 001100      | subtract from sp immediate           |

| 13     | addar    | 001101      | add register to acc                  |

| 14     | subar    | 001110      | subtract register from acc           |

| 15     | addixr   | 001111      | add register to ix                   |

| 16     | subixr   | 010000      | subtract register from ix            |

| 17     | Idar     | 010001      | load acc with register               |

| 18     | ldixr    | 010010      | load ix with register                |

| 19     | ldicr    | 010011      | load ic with register                |

| 20     | inva     | 010100      | invert acc                           |

| 21     | invix    | 010101      | invert ix                            |

| 22     | anda     | 010110      | and acc with memory                  |

| 23     | ora      | 010111      | or acc with memory                   |

| 24     | xora     | 011000      | xor acc with memory                  |

| 25     | rsfta    | 011001      | right shift acc                      |

| 26     | Isfta    | 011010      | left shift acc                       |

| 27     | jmp      | 011011      | jump                                 |

| 28     | jaz      | 011100      | jump if acc is zero                  |

| 29     | janz     | 011101      | jump if acc is not zero              |

| 30     | jixz     | 011110      | jump if ix is zero                   |

| 31     | jixnz    | 011111      | jump if ix is not zero               |

| 32     | call     | 100000      | call a subroutine                    |

| 33     | ret      | 100001      | return to caller                     |

| 34     | pusha    | 100010      | push register acc onto stack         |

| 35     | popa     | 100011      | pop acc from stack                   |

| 36     | zeroa    | 100100      | zero out the acc                     |

| 37     | Idai     | 100101      | load acc immediate                   |

| 63     | hlt      | 111111      | halt the machine                     |

In addition, there are three pseudo-operators that have effect only during the assembly process. These are the 'con', 'equ', and the 'org' operators, and will be discussed later.

ાયતીય આવ્યું પ્રાથમિક જાણવામાં આવ્યું છે.

÷

5.2. Stack

"Why?" said the Caterpillar. Here was another puzzling question;

As can be easily seen, this language has a built-in stack facility for calling functions and for pushing values onto a stack. This makes the language posses substantial versatility. In the micro-program, the stack is rooted at the top of memory (location 1023) and grows toward smaller memory locations.

5.3. Instruction Format

"Come, there's half my plan done now! How puzzling all these changes are!"

The instruction format for this language calls for each instruction to be one word in length, having the following format:

| ope | ration code | indirection | indexing |   | address of operand |   |

|-----|-------------|-------------|----------|---|--------------------|---|

| 17  | 12          | 11          | 10       | 9 |                    | 0 |

Bit 11, when on, causes indirection to occur. Bit 10, when on, causes indexing to occur via the IX register. Indexing takes precedence over indirection.

#### 5.4. Syntax

"Curiouser and curiouser!" cried Alice

This assembler recognizes the assembly language that is described by the following rules:

- Each line of code is composed of one to three fields: label, opcode, and address.

- The label field contains a label that may be referenced to anywhere else in the program. This label must consist of any non-white-space (i.e., non-blank-looking-whenprinted) characters and can be of any length.

- The opcode field must contain a string that corresponds to one of the legal opcodes.

- The address field must contain a string that consists of the characters '0' through '9', optionally preceded by the character '-'. The address field may be immediately preceded by the character '\*' which signified indirection, and succeeded by the two characters '()' which signify indexing. The last two options are not mandatory but should not be separated with a blank from the rest of the address field when included. Instead of a number, the address field may be a label, conforming to the rules of label-forming. The

address will be filled with the value of the label before the end of assembly. Each label must be unique in the program when appearing on the left on an opcode.

- The label field may start on or before column 3. The opcode field should start following the label field and anywhere on or before column 15. The address field should start after the opcode field and on or before column 40. There should be at least one white-space between each pair of fields.

- In addition to the default opcodes described earlier, there are three more pseudoopcodes. These are used during assembly only, and are not used at all during execution. The first one is the 'equ' opcode. It associates the label on its line with the number/address appearing on the same line, for future references in the program. This is useful for defining "global" constants once at the beginning of the program, and referring to them by name all throughout the program. The second one is the 'con' pseudo-operator. It places the value of the address of the same line into the memory location specified by the assembly memory counter. The address here may be a label. This operator can be used to store data/constants into memory locations during the assembly process. The third is the 'org' pseudo-operator. It simply modifies the assembler memory counter to become the address field specified with this operator. This is used to assemble code into several separate memory regions.

- The last line of any program must contain only the string "end" in the normal opcode field of that line.

- Comments may be included between curly brackets (i.e., '{' and '}'). All comments will be ignored. Blank lines may be inserted anywhere in the source program. All such lines will also be ignored. Comments may span several lines.

- Immediate instructions have their data in the address field, so the data can only be ten bits long, not eighteen.

- Instructions that operate on registers (ex: 'addar') take as an operand (i.e., as the address field) a number between 0 and 3, inclusive, that represents the register to be operated on as follows:

0 - ACC 1 - SP 2 - IX 3 - IC

It is usually convenient to define these registers with 'equ's at the beginning of the program, for future references. For example:

ix equ 2 . . . addar ix

The last statement adds to the accumulator the contents of IX.

Character case (upper vs. lower) matters, so the label 'FOO' is distinct from 'foo', and both are distinct from 'Foo'.

#### The Microcode Interpreter 6.

It sounded an excellent plan, no doubt, and very neatly and simply arranged: the only difficulty was, that she had not the smallest idea how to set about it.

This section describes the microcode interpreter. The function of the microcode interpreter is to convert the microcode from the symbolic form it is written in, to the form that can be placed into the micro-memory. Alternatively, the microcode would have been coded in binary by the user, which makes for a very tedious and error-prone task.

6.1. Syntax

"I didn't say there was nothing better," the King replied. "I said there was nothing like it."

The micro-program in symbolic form should comply with the following rules:

Each line shall be composed of as many occurrences of the following 40 strings as desired:

- 1. alu-right=ic

- 2. alu-left=ic

- alu-right=ix 3.

- alu-left=ix 4.

- 5. alu-right=sp

- alu-left=sp 6.

- 7. alu-right=x

- 8. alu-left=x

- alu-right=acc 9.

- 10 alu-left=acc

- 11. alu-right=-1

- 12. alu-left=0

- 13. alu-right=0

- 14. alu-right=1

- 15. alu-right=sign

- 16. mar=mbr

- 17. oc=mbr

- 18. ii=mbr

- 19. alu-left=mbr

- 20.

- left-shift

- 21. right-shift

- 22. data-bus=alu-output

- 23. address-bus=alu-output

- 24. data-bus=mbr

- 25. sp=data-bus

-

- 26. x=data-bus

- 27. x=18

- 28. acc=data-bus

- 29. mar=ic

- 30. ic=data-bus

- 31. mar=address-bus

- 32. mbr=data-bus

- 33. ix=data-bus

- 34. mbr=mem(mar)

- 35. mem(mar)=mbr

- 36. start=off

- 37. invert-left-alu

- 38. invert-right-alu

- 39. x=10

- 40. data-bus=mar

Each set of micro-operations that are specified on ONE input line, will be executed during ONE clock cycle (but maybe in different clock phases).

- The character ';' is used as a separator and should follow each one of the strings.

- Any line may be labeled by placing a label string at its beginning and by separating the label from the first micro-operation by the character ':'. Each label so used must be unique in the micro-program.

- Comments may be inserted between curly brackets. All comments will be ignored by the interpreter. Blank line will also be ignored and therefore can be inserted anywhere. Comments may span several lines.

- The last line of the micro program must contain the string "end", and nothing else.

- Case matters, so the label 'FOO' is distinct from 'foo', and both are distinct from 'Foo'.

- Long lines may be continued by placing the character '\$' at the end of the line to be continued, and this may be done to continue a single micro instruction on as many lines as desired.

- In addition to the micro operations specified above, two more micro-instructions may be specified: the '<u>if</u>' and the '<u>aoto</u>'. The 'if' has the following syntax:

#### if(reg,bit)=cmp then goto label;

where '<u>reg</u>' is one of the strings { ic, ix, sp, x, acc, mbr, mar, oc, ii, zero-detect }, '<u>bit</u>' is a decimal number that represents the bit to be tested, '<u>cmp</u>' is either 0 or 1 (the value to be tested against), and '<u>label</u>' is a valid label in the micro-program to be branched to if the test is successful (i.e. reg(bit)=cmp). The 'goto' micro-instruction is much simpler:

### goto <u>label;</u>

This micro-instruction unconditionally transfers micro-control to the micro-location specified by 'label'. If the label has any non-numeric character in it, it is considered to

be a relative target address, to be determined when the same label is found at the beginning of another micro instruction. If the label consists entirely of numeric characters, it is taken to be an absolute address, specified in decimal. For example, '123-foo' is a label while '123' is a absolute micro-memory address. In the former case, the interpreter will search for a '123-foo' label on the other microcode source lines, and, if none are found, an 'undefined micro-label' will be generated. The label in the 'if' and 'goto' statements may optionally be replaced by an absolute address: this address will be taken literally to be the branching address, but in almost all cases, a label is much preferable to an absolute branching address, and so the provision for this capability here is only token.

White-spaces may be inserted anywhere in the micro-program, as all white-spaces are completely ignored.

Any failures to comply with the above rules will cause syntax errors to be generated during the microcode-interpretation phase of this program. All error messages are explicit and are meant to be self-explanatory. After the microcode has been interpreted, it will be placed into the micro-memory, beginning at micro-memory location 0.

7. The User Interface

"Thank you very much," she whispered in reply, "but I can do quite well without."

#### 7.1. Screen format

The simulator updates the terminal display in a screen-oriented fashion. Direct cursor control is exercised through a library package which is intelligent enough to look up the terminal type in the appropriate UNIX system file. The most current values of the various registers and buses are displayed on the screen at all times, unless the user specified to the simulator to run in the 'quiet' mode. This display makes possible for the user to trace only the specific system components of his/her choice, while possibly ignoring the rest, with minimal cognitive overhead. In addition, this method of display is generally considered particularly aesthetically pleasing (it is analogous to using a window-editor, whereas the alternative is a line-editor).

While the system is running, the display appears as follows:

| Computer-Simulation-by                                        | y−−Gabriel−Robins−−                               | version-3-of-7                | /26/88    |  |  |

|---------------------------------------------------------------|---------------------------------------------------|-------------------------------|-----------|--|--|

| ACC=000 1000 10 100 10 1 1 1 1 = 177 1 1                      | DATA-BUS=0                                        | DATA-BUS=00000000000000000000 |           |  |  |

| MBR=000 1000 100000000000 = 17408                             | ADDRESS-BUS=0000000000=0                          |                               |           |  |  |

| Mrr=0000000000=0                                              | ALU-LEFT-BUS=000000000000000000000000000000000000 |                               |           |  |  |

| I C=00000000 1 1=3                                            | RLU-R   GHT-BUS=0000000000000000 1= 1             |                               |           |  |  |

| open gates: 2 14 16 17 18                                     |                                                   |                               |           |  |  |

| micro-ops: alu-left=ic; alu-right=1; mar=mbr; oc=mbr; ii=mbr; |                                                   |                               |           |  |  |

|                                                               |                                                   | CLOCK-PHASE=0                 |           |  |  |

| 0C=000100=4   =01=1                                           | Micro Program<br>Control Logic                    | START=off                     | paus i ng |  |  |

| CSAR=000000011=3                                              |                                                   |                               |           |  |  |

| CSBR= 10 10000000000 10 1 1 1000 10000000 1000000             |                                                   | SP=00000000                   |           |  |  |

| X=0000000011111111111=1023                                    | tupe=GATE                                         | I X=000 1000 1 1 1=7 1        |           |  |  |

-Pause-Continue-Stop-Quiet-Trace-Redraw-Values-Microcode-Object-Examine-Help--

# 7.2. The interaction With the User

But Humpty Dumpty only shut his eyes, and said "Wait till you've tried."

All commands are one letter long, which in all cases is the first letter of the word describing the command. A short menu is present at the bottom of the display at all times, summarizing the commands. A help facility makes it possible to review the functions of the commands at any given time. Some commands generate a sub-menu, which contains subcommands appropriate for the original command only. A major feature of the user interface is that pressing 'return' is never necessary, and most of the time even quite useless. Instead, the simulator 'senses' when a key was pressed, and accordingly takes the appropriate action. When no keys are pressed, it will continue merrily about its simulation, not bothering to prompt the user. Some commands, however, directly cause the simulator to pause and read keyboard input. This scheme tends to minimize both the number of key strokes and the elapsed time involved when controlling the behavior of the simulator.

#### 7.3. The Commands

"When I use a word," Humpty Dumpty said, in a rather scornful tone, "it means just what I choose it to mean -- neither more nor less."

The various commands that are available at the top-level are:

Pause - pause between clock cycles, and wait for a command. The pause command is

two-level: a second pause will cause the machine to pause between clock phases. Subsequent pause commands will not have any effect.

- <u>Continue</u> negate the last pause command.

- <u>Stop</u> halt the machine, and create a final memory dump.

- <u>Quiet</u> do all things silently, (do not update the display). This is useful for going quickly through thousands of simulation steps, without having to watch the changes in the system on the screen (which tends to greatly slow down the simulation).

- <u>Trace</u> negate the 'quiet' command. All state changes of the simulator will be reflected on the screen.

- <u>Redraw</u> clear the screen and redraw the display. This is useful when some renegade process writes bogus text to your terminal and 'messes up' the display.

- <u>Values</u> allows the user to change the contents of registers and buses through a windoweditor. This is very useful for experimenting with the simulator, and playing various 'what-if' scenarios.

- <u>Microcode</u> list the interpreted microcode.

- <u>Object</u> list the object code of the assembled program.

- <u>Examine</u> list the contents of the entire main memory.

- <u>Help</u> print this summary.

All commands that list things, do so by piping the output through a familiar system filter, for the convenience of the user. All standard system subcommands that can be used with this filter, can also be used when doing a listing. The filter used here is the UNIX utility more(1).

#### 7.4. Error Handling

"It is wrong from beginning to end," said the Caterpillar, decidedly;

The microcode interpreter, as well as the assembler, may produce various diagnostic messages during normal operation. This usually occurs when the user fails to comply with the syntax rules built into the simulator. All such error messages are meant to be self-explanatory. The line number on which the error occurred is included in the error-message, when appropriate. When the microcode contains errors, assembly will not be attempted. When the source program contains errors, execution will not be attempted.

#### 7.5. Special Files

"Ah, what is it now?" the Unicorn cried eagerly. "You'll never guess! I couldn't."

Several file names have special meaning to the simulator:

- <u>"object.dump</u>" this file will contain the dump of the assembled user program, immediately after the assembly. It is not updated, so it will not be current when running self-modifying programs.

- <u>"microcode.dump"</u> this file will contain the dump of the microcode. Since the microcode can not modify itself, this file is always current. For large micro-programs, however, the usefulness of the binary microcode dump is questionable.

- <u>"final.memory"</u> this file will contain the final dump of the memory, after the entire system halted. It is meant to be used for debugging as well as for output presentation purposes (i.e., since there are no output devices associated with the simulator, programs can "print" to the memory, which can be examined by the user).