- [22] A. B. Kahng and G. Robins, "A New Class of Iterative Steiner Tree Heuristics with Good Performance", *IEEE Transactions on CAD* 11(7), July 1992, pp. 893-902.

- [23] S. Khuller, B. Raghavachari and N. Young, "Balancing Minimum Spanning and Shortest Path Trees", Proc. ACM/SIAM Symp. on Discrete Algorithms, January 1993, to appear.

- [24] S. Kim, R. M. Owens and M. J. Irwin, "Experiments with a Performance Driven Module Generator", Proc. ACM/IEEE Design Automation Conf., 1992, pp. 687-690.

- [25] T. Lengauer, Combinatorial Algorithms for Integrated Circuit Layout, Berlin, Wiley-Teubner, 1990.

- [26] I. Lin and D. H. C. Du, "Performance-Driven Constructive Placement", Proc. ACM/IEEE Design Automation Conf., 1990, pp. 103-106.

- [27] M. Marek-Sadowska and S. Lin, "Timing Driven Placement", Proc. IEEE Intl. Conf. on Computer-Aided Design, 1989, pp. 94-97.

- [28] S. Prasitjutrakul and W. J. Kubitz, "A Timing-Driven Global Router for Custom Chip Design", Proc. IEEE Intl. Conf. on Computer-Aided Design, 1990, pp. 48-51.

- [29] A. Prim, "Shortest Connecting Networks and Some Generalizations", Bell System Tech. J. 36 (1957), pp. 1389-1401.

- [30] S. K. Rao, P. Sadayappan, F. K. Hwang and P. W. Shor, "The Rectilinear Steiner Arborescence Problem", Algorithmica 7 (1992), pp. 277-288.

- [31] G. Robins, "On Optimal Interconnections", Ph.D. thesis (technical report CSD TR-920024), CS Department, University of California, Los Angeles, June 1992.

- [32] J. Rubinstein, P. Penfield, and M. A. Horowitz, "Signal Delay in RC Tree Networks", *IEEE Trans. on CAD* 2(3) (1983), pp. 202-211.

- [33] A. Srinivasan, K. Chaudhary and E. S. Kuh, "RITUAL: A Performance Driven Placement Algorithm for Small-Cell ICs", *Proc. IEEE Intl. Conf. on Computer-Aided Design*, 1991, pp. 48-51.

- [34] S. Sutanthavibul and E. Shragowitz, "Adaptive Timing-Driven Layout for High Speed VLSI", Proc. ACM/IEEE Design Automation Conf., 1990, pp. 90-95.

- [35] S. Teig, R. L. Smith and J. Seaton, "Timing Driven Layout of Cell-Based ICs", VLSI Systems Design, May 1986, pp. 63-73.

- [36] R. S. Tsay, "Exact Zero Skew", Proc. IEEE Intl. Conference on Computer-Aided Design, 1991, pp. 336-339.

- [37] D. Zhou, F. P. Preparata and S. M. Kang, "Interconnection Delay in Very High-speed VLSI", IEEE Trans. on Circuits and Systems 38(7), 1991.

- [38] D. Zhou, S. Su, F. Tsui, D. S. Gao and J. Cong, "Analysis of Trees of Transmission Lines", technical report UCLA CSD-920010.

## References

- [1] C. J. Alpert, T. C. Hu, J. H. Huang and A. B. Kahng, "A Direct Combination of the Prim and Dijkstra Constructions for Improved Performance-Driven Global Routing", technical report CSD-920051, UCLA Department of Computer Science, 1992.

- [2] T. G. Andrews, ed., Methods of Psychology, New York, John Wiley, 1948.

- [3] B. Awerbuch, A. Baratz and D. Peleg, "Cost-Sensitive Analysis of Communication Protocols", *Proc.* ACM Symp. on Principles of Distributed Computing, 1990, pp. 177-187.

- [4] Barrera, T., J. Griffith, G. Robins and T. Zhang, "Narrowing the Gap: Near-Optimal Steiner Trees in Polynomial Time", *Proc. IEEE Intl. ASIC Conf.*, Rochester, Sept. 1993, pp. 87-90.

- [5] K. D. Boese, J. Cong, A. B. Kahng, K. S. Leung and D. Zhou, "On High-Speed VLSI Interconnects: Analysis and Design" *Proc. Asia-Pacific Conf. on Circuits and Systems*, Sept. 1992, pp. 35-40.

- [6] K.D. Boese, A. B. Kahng and G. Robins, "High-Performance Routing Trees with Identified Critical Sinks", Proc. ACM/IEEE Design Automation Conf., June 1993, pp. 182-187.

- [7] K. D. Boese, A. B. Kahng, B. A. McCoy and G. Robins, "Fidelity and Near-Optimality of Elmore-Based Routing Constructions", *Proc. IEEE Intl. Conf. on Computer Design*, October 1993, pp. 81-84.

- [8] D.-S. Chen and M. Sarrafzadeh, "A Wire-Length Minimization Algorithm for Single-Layer Layouts", Proc. IEEE Intl. Conference on Computer-Aided Design, 1992, pp. 390-393.

- [9] J. P. Cohoon and L. J. Randall, "Critical Net Routing", Proc. IEEE Intl. Conf. on Computer Design, 1991, pp. 174-177.

- [10] J. Cong, A. B. Kahng, G. Robins, M. Sarrafzadeh, and C. K. Wong, "Provably Good Performance-Driven Global Routing", *IEEE Trans. on CAD* 11(6), June 1992, pp. 739-752.

- [11] J. Cong, K.-S. Leung and D. Zhou, "Performance-Driven Interconnect Design Based on Distributed RC Delay Model", Proc. ACM/IEEE Design Automation Conf., 1993, pp. 606-611.

- [12] E. W. Dijkstra, "A Note on Two Problems in Connection With Graphs", Numerische Mathematik 1(1959), pp. 269-271.

- [13] W. E. Donath, R. J. Norman, B. K. Agrawal, S. E. Bello, S. Y. Han, J. M. Kurtzberg, P. Lowy and R. I. McMillan, "Timing Driven Placement Using Complete Path Delays", Proc. ACM/IEEE Design Automation Conf., 1990, pp. 84-89.

- [14] A. E. Dunlop, V. D. Agrawal, D. N. Deutsh, M. F. Jukl, P. Kozak and M. Wiesel, "Chip Layout Optimization Using Critical Path Weighting", Proc. ACM/IEEE Design Automation Conf., 1984, pp. 133-136.

- [15] W. C. Elmore, "The Transient Response of Damped Linear Network with Particular Regard to Wideband Amplifiers", J. Applied Physics 19 (1948), pp. 55-63.

- [16] S. Even, Graph Algorithms, Potomac, MD, Computer Science Press, 1979.

- [17] M. Hanan, "On Steiner's Problem with Rectilinear Distance", SIAM J. Appl. Math., 14 (1966), pp. 255-265.

- [18] P. S. Hauge, R. Nair and E. J. Yoffa, "Circuit Placement for Predictable Performance", *Proc. IEEE Intl. Conf. on Computer-Aided Design*, 1987, pp. 88-91.

- [19] J.-M. Ho, G. Vijayan and C. K. Wong, "New Algorithms for the Rectilinear Steiner Tree Problem", *IEEE Transactions on Computer-Aided Design*, 9(2), 1990, pp. 185-193.

- [20] M. A. B. Jackson and E. S. Kuh, "Estimating and Optimizing RC Interconnect Delay During Physical Design", Proc. IEEE Intl. Conf. on Circuits and Systems, 1990, pp. 869-871.

- [21] M. A. B. Jackson, E. S. Kuh, and M. Marek-Sadowska, "Timing-Driven Routing for Building Block Layout", Proc. IEEE International Symposium on Circuits and Systems, pp. 518-519, 1987.

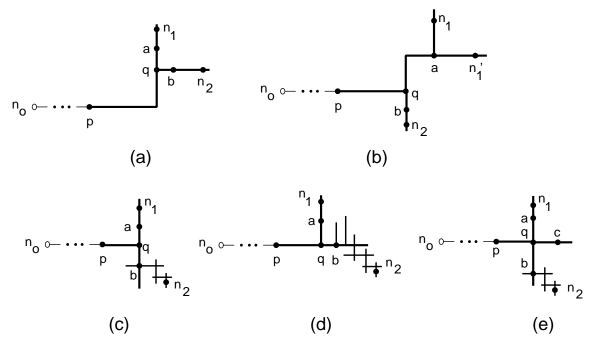

between p, Pin(a), and Pin(b).

In Figure 22(b)-(d), edge (p, q) is a straight edge. Let M be the MS containing (p, q), and let M' be the MS perpendicular to M with entry point q.

- In Figure 22(b), edge (q, a) is L-shaped and edge (q, b) is on the MS M'. By Lemma B4, M' must contain a sink, which will be contained in subtree T<sub>b</sub>. Thus, Pin(b) (n<sub>2</sub> in the Figure) is located on M'. Node a is the entry point for two branches perpendicular branches containing sinks (by Lemma B4); Pin(a) is chosen arbitrarily from one of these branches (Line 3 in Figure 19). In Figure 22, either Pin(a) = n<sub>1</sub> or Pin(a) = n'<sub>1</sub>; thus, it can be seen from the Figure that q is the closest connection between p, Pin(a), and Pin(b).

- In Figure 22(c), M' is the union of two branches. One of these branches contains a sink (by Lemma B4); without loss of generality, let this be the branch containing edge (q, a), with  $Pin(a) = n_1$  in M'. Let B be the branch containing edge (q, b). If Pin(b) is on B, then q will be the closest connection between p, Pin(a) and Pin(b). Otherwise, according to Lemma B2 we must have that b is the entry point to a far branch off of M'. Hence, if Pin(b) is not on B, the b-Pin(b) path in  $T^*$  contains only edges on far branches (by the criteria in Lines 8-10 in Figure 19; see  $n_2 = Pin(b)$  in Figure 22(c)). Thus, Pin(b) is contained in the upper-right quadrant relative to q in the Figure, and q is the closest connection between p, Pin(a), and Pin(b).

- Finally, consider the configuration in Figure 22(d). Here, MS M' is a branch of M containing node a and sink Pin(a). Suppose that M' is a far branch; if Pin(b) is not on MS M, then there must be a near branch off of M somewhere below q in  $T^*$  (otherwise, we could reduce all delays by shifting the entire half segment of M below q toward a). Let  $B_j$  be the near branch below q closest to q. Either sink Pin(b) is on  $B_j$ , or the  $q_j$ -Pin(b) path in  $T^*$  consists only of edges in  $B_j$  or far branches. In either case, Pin(b) (=  $n_2$  in the Figure) is contained in the lower-right quadrant relative to q. If M' is a near branch, an analogous argument again shows that Pin(b) is in q's lower-right quadrant. Thus, q is the closest connection between p, Pin(a) and Pin(b).

Except for redundancies and pruning of sub-optimal trees, BB-SORT-C searches over all possible ways to construct a Steiner tree sequentially, such that each sink is added by a closest connection to some edge in the current tree. Thus, we have:

**Theorem B1:** For any positive linear combination of sink delays,  $f = \sum_{i=1}^{k} \alpha_i \cdot t(n_i)$ ,  $\alpha_i > 0 \ \forall i$ , algorithm BB-SORT-C returns a Steiner tree  $T^*$  which minimizes f.

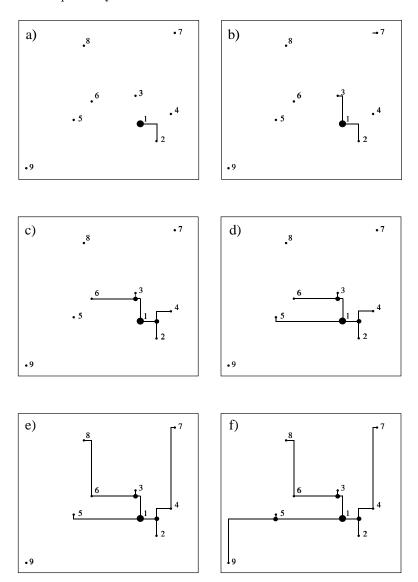

Figure 22: Five possible topologies at any Steiner node q in  $T^*$ . Each diagram shows two sinks  $n_1$  and  $n_2$  below node q in the tree, such that q is the closest connection between  $n_1$ ,  $n_2$  and q's parent p.

**Proof:** Part (i) of the Lemma is true since the construction of Figure 20 removes exactly one sink during each pass through Lines 3 to 9.

To show (ii), let p be the parent of the node q at Line 3 in Figure 20. The first case is when q is a sink or a degree-4 Steiner node in  $T_i$  (as in Figure 22(e)). In this case, edge (p,q) will remain in tree  $T_{i-1}$ . If (p,q) is L-shaped, we must have a connection as in Figure 22(a), where the two children of q are eventually replaced by sinks on the maximal segments with entry point q (i.e.,  $n_1$  and  $n_2$  in the Figure). Both of these sinks have closest connections to (p,q) at q. If (p,q) is a straight edge, let M be the MS containing (p,q), and let a be a child of q in  $T^*$ . The sink Pin(a) is assigned in the Figure 19 template such that the q-Pin(a) path in  $T^*$  will contain only edges in M, edges in branches off of M, or edges in a sequence of far branches off of branches of M. (For example, consider the paths from q to sinks  $n_1$  and  $n_2$  in Figure 22(c)-(e).) Thus, Pin(a) and p cannot be on the same side of a line that passes through q and is perpendicular to M. Consequently, q will be the closest connection between edge (p,q) and Pin(a).

The second case is when q is a degree-3 Steiner node in  $T_i$ . Let a and b be the children of q in  $T^*$  such that Pin(a) and Pin(b) are q's children in  $T_i$ . Without loss of generality, we assume that Pin(q) = Pin(a) and  $n_i = Pin(b)$ . We must show that q is located at the closest connection between nodes p, Pin(a), and Pin(b). There are four possible configurations for connections at q, as shown in parts (a)-(d) of Figure 22.

• In Figure 22(a), edge (p, q) is L-shaped and both Pin(a) and Pin(b) (denoted by  $n_1$  and  $n_2$  in the figure) must be on maximal segments with entry point q; it is easy to see that q is the closest connection

| $T^*$ Decomposition Procedure                                              |  |  |  |  |  |

|----------------------------------------------------------------------------|--|--|--|--|--|

| Input: Optimal delay tree $T^*$                                            |  |  |  |  |  |

| <b>Output:</b> Sequence of sinks $n_1, \ldots n_k$ used to construct $T^*$ |  |  |  |  |  |

| using only closest connections of each $n_i$ to $T_{i-1}$                  |  |  |  |  |  |

| 1. $i = k$                                                                 |  |  |  |  |  |

| 2. Repeat until $i == 0$                                                   |  |  |  |  |  |

| 3. Find a node $q \in T_i$ whose children are all leaves                   |  |  |  |  |  |

| 4. If $q == n_0$ set c to be any child of $n_0$ in $T^*$                   |  |  |  |  |  |

| 5. Else if $q$ has degree 4                                                |  |  |  |  |  |

| 6. Set $c$ to be the child of $q$ in $T^*$ on the MS                       |  |  |  |  |  |

| containing edge $(parent(q), q)$                                           |  |  |  |  |  |

| 7. Else Set c to be a child of q such that $Pin(c) \neq Pin(q)$            |  |  |  |  |  |

| 8. $n_i = Pin(c)$                                                          |  |  |  |  |  |

| $9. 	 T_{i-1} = T_i \backslash n_i$                                        |  |  |  |  |  |

| 10. $i = i - 1$                                                            |  |  |  |  |  |

Figure 20: Procedure to determine a sequence of sinks  $n_1, \ldots, n_k$  which can be used to construct  $T^*$  by a sequence of closest connections from  $n_i$  to tree  $T_{i-1}$ .

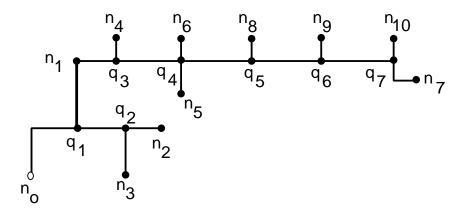

Figure 21: Example of the order in which pins are "peeled" from an optimal-delay Steiner tree  $T^*$ . (Sinks  $n_i$  are peeled from  $T^*$  in reverse order of their subscripts.)

| Pin Assignments for Example Tree |            |                                                                 |  |  |  |

|----------------------------------|------------|-----------------------------------------------------------------|--|--|--|

| Steiner node $q$                 | Pin(q)     | Reason for Assignment                                           |  |  |  |

| $q_1$                            | $n_1$      | $(n_0, q_1)$ is L-shaped (Line 4)                               |  |  |  |

| $q_2$                            | $n_2$      | $n_2$ is on MS containing $(q_1, q_2)$ (Line 6)                 |  |  |  |

| $q_3$                            | $n_4$      | $n_1$ is the entry point to MS containing $(n_1, q_3)$ (Line 8) |  |  |  |

| $q_4$                            | $n_5$      | far branch at $q_3$ and near branch at $q_4$ (Line 15)          |  |  |  |

| $q_5$                            | $Pin(q_6)$ | $q_4$ has degree 4 (Line 11)                                    |  |  |  |

| $q_6$                            | $Pin(q_7)$ | far branch at $q_5$ and no near branch at $q_6$ (Line 16)       |  |  |  |

| $q_7$                            | $n_7$      | far branch at $q_6$ and near branch at $q_7$ (Line 15)          |  |  |  |

Table 12: Pin assignment to Steiner nodes in the example of Figure 21. Line numbers refer to the corresponding line in the Pin assignment procedure of Figure 19.

if q is the source or a sink, then Pin(q) = q; and (ii) if q is a Steiner node, then Pin(q) is chosen according to the template given in Figure 19.

```

Pin(q) Assignment Procedure

Input: Optimal delay tree T^*

Steiner node q \in T^* such that Pin(w) has been assigned

for each w \in T_q^*, w \neq q

Output: Pin(q)

p = parent(q) in T^*

2.

If edge (p, q) is a straight edge

3.

Set M to be the MS containing (p,q)

4.

If edge (p,q) is L-shaped

5.

Set c arbitrarily to be one of q's two children

/* (q has exactly two children, by Lemma B1) */

6.

Else if T_q contains a sink on M

7.

Set c to be the child of q on M

Else if p is the entry point to M

8.

9.

Set B to be the far branch of M at q

/* (such a B exists by Lemma B2) */

10.

Set c to be the child of q on B

11.

Else if p has degree 4

Set c arbitrarily to be one of q's children

12.

13.

Else if there is a near (far) branch of M at p

If there is a far (near) branch B of M at q

14.

15.

Set c to be the child of q on B

16.

Else Set c to be the child of q on M

17.

Pin(q) = Pin(a)

```

Figure 19: Criteria used to associate a sink Pin(q) with each Steiner node q in the optimal-delay tree  $T^*$ . The assignment determines which sink in  $T_q$  will remain in the tree when q is removed from the current tree while "peeling off" sinks from  $T^*$ .

After Pin(q) has been assigned, we can apply the rules described in Figure 20 to peel off sinks, thus determining the sequence in which sinks can be added to construct  $T^*$ . Note that node p in Line 3 of Figure 20 must exist since  $T_i$  is finite and has no cycles. Figure 21 gives an example of the decomposition procedure applied to an eleven-pin net. Sinks in the figure are labeled in reverse order of how the decomposition procedure might peel them off from the tree. (Other orders are possible because the decomposition procedure is not completely deterministic.) Table 12 shows how Pin(q) was assigned for each Steiner node in Figure 21.

We now show that the procedure of Figure 20 gives a sequential decomposition of the optimal-delay tree  $T^*$ , such that each  $T_i$  is constructed by connecting sink  $n_i$  to tree  $T_{i-1}$  by a closest connection to some edge in  $T_{i-1}$ .

**Lemma B5:** There exists a sequence of subtrees  $T_0 = \{n_0\}, T_1, T_2, \ldots, T_k = T^*$  such that for each i,  $1 \le i \le k$ , (i) there is a sink  $n_i \in T_i$  such that  $T_{i-1} = T_i \setminus n_i$ , and (ii) either  $n_i$  is connected to  $n_0$ , or  $n_i$  makes a closest connection in  $T_i$  to some edge in  $T_{i-1}$ .

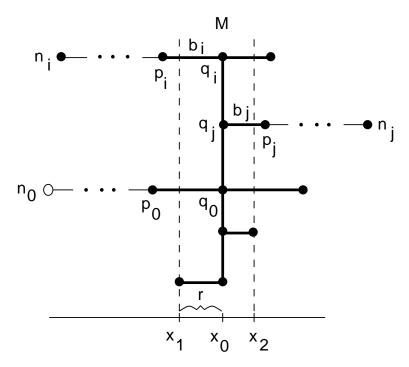

to  $(q_i, p_i)$  is equal to r \* (r/2 + K') + K'', where K' and K'' are again constants. Therefore, the equation for  $t(n_i)$  is

$$t(n_i) = (1 - d) * r^2 + K_1 * r + K_0$$

(9)

where  $K_1$  and  $K_0$  are constants. From Lemma B3, we know that  $d \ge 1$ , implying that  $t(n_i)$  is a concave function of r. Similarly, delay to a sink  $n_i$  along a far branch  $b_i$  off of M will be equal to

$$-d*r^2 + K_1'r + K_0' \tag{10}$$

where again  $K'_1$  and  $K'_0$  are constants; this too is a concave function of r. Finally, delay to any sink whose source-sink path does not contain an edge in M will be linear in r, and thus also a concave function. Since any linear combination of functions that are each concave on a given interval will also be concave on that interval, f is concave in r and is minimized at one of its extreme values, i.e., at r = 0 or  $r = x_2 - x_1$ .

Thus, M may be moved so that it contains a new node, say  $p_i$ . If  $p_i$  is a sink, the lemma is proved. If  $p_i$  is a Steiner node, then because it has degree > 2, there must be a vertical MS incident to  $p_i$ , and this vertical MS must contain a sink since M is the lowest maximal segment not containing a sink. Hence, if  $p_i$  is a Steiner node, the shifted M will also contain a sink.

A direct corollary of Lemma B4 is that all Steiner nodes in the Elmore-optimal Steiner tree are contained in the Hanan grid:

Corollary: Let X be the set of x-coordinates for all pins in N, and let Y be the set of y-coordinates in N. Then if (x, y) is the location of a Steiner node in  $T^*$ ,  $x \in X$  and  $y \in Y$ .

Thus, only a finite number of possible Steiner point locations need to be considered. Hanan's original theorem may be viewed as a special case of this Corollary with the driver on-resistance  $r_d \to \infty$ .

### **B.4.** Decomposition Theorem for $T^*$

To prove that BB-SORT-C will return the optimal-delay tree  $T^*$ , we show that  $T^*$  can be constructed by starting with a tree  $T_0$  containing only  $n_0$ , then successively adding a sequence of sinks  $n_i$ ,  $1 \le i \le k$ , each of which yields a tree  $T_i$  by making a closest connection to some edge in the current tree  $T_{i-1}$ . We show that such a sequence of trees exists by starting with  $T^* = T_k$  and i = k, then "peeling off" an  $n_i$  at each iteration such that  $n_i$  was joined by a closest connection in  $T_i$  to some edge in  $T_{i-1} = T_i \setminus n_i$ .

At each step, we find an interior node  $q \in T_i$  whose children are all leaves. Each of these leaves must be a sink, because all low-degree Steiner nodes (i.e., with degree < 3) are removed from  $T_{i+1} \setminus n_{i+1}$ . We choose one of q's leaves to be the  $n_i$  that is peeled off, and set  $T_{i-1} = T_i \setminus n_i$ . The choice of which leaf should be peeled is guided by the function Pin(q), which specifies one of q's children that should not be peeled off from q. Thus, when q is removed as a low-degree Steiner node, the edge between q and its parent is replaced with an edge between Pin(q) and q's parent. More formally, we define Pin(q) for each node  $q \in T^*$  as follows: (i)

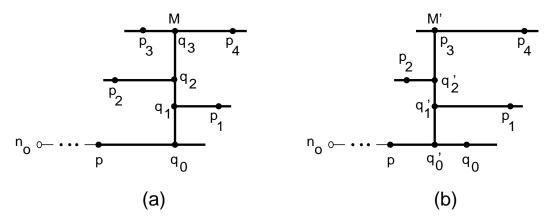

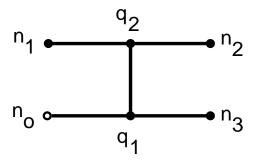

Figure 17: Proof of Lemma B3: (a) Example where |Near(M)| = |Far(M)| for maximal segment M. M can be shifted to M', as shown in (b), to reduce delay at all sinks in the subtree  $T_{q_0}^*$ .

Figure 18: Proof of Lemma B4: because the objective function f is concave in r over the interval  $0 \le r \le x_2 - x_1$ , f will be minimized when the maximal segment M passes through either the gridline at  $x_1$  or the gridline at  $x_2$ .

far side of M such that shifting M to  $x=x_2$  would cause M to intersect some node that is in  $T_{q_0}^*$  but not in M. Let the variable r,  $0 \le r \le x_2 - x_1$ , denote the position of M between the x-coordinates  $x_1$  and  $x_2$ . We will show that minimizing the delay function f implies that either r=0 or  $r=x_2-x_1$ .

Let d = Far(M) - Near(M). Consider the delay to some sink  $n_i$  located along a near branch  $b_i$  off of M which has entry point  $q_i$ . (In general, we let  $q_j$  denote the entry point to branch  $b_j$ .) Delay  $t(n_i)$  is quadratic in r only along the edge  $(p_0, q_0)$  and along the edge  $(q_i, p_i)$ , where  $p_i$  is the child of  $q_i$  on  $b_i$ . To be precise, the delay due to  $(p_0, q_0)$  is equal to r \* (r/2 - d \* r + K), where K is some constant; the delay due

leave delay to all other sinks unchanged, contradicting the optimality of  $T^*$ .

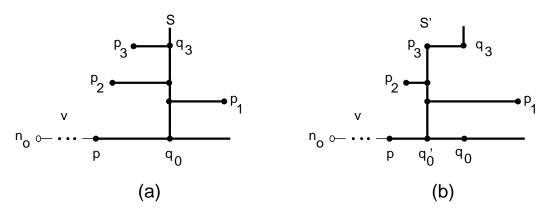

Figure 16: Proof of Lemma B2: Example (a) with |Near(S)| > |Far(S)| for a segment S between  $q_0$  and  $q_3$ ; (b) shows how S can be shifted to S' to reduce delay to all sinks in  $T_{q_0}^*$  and leave delay unchanged at all other sinks.

We can now use Lemma B2 to show that if an MS M has as many near branches as far branches, then it can be shifted so as to reduce delay to some sinks and leave delay to others unchanged. This is because shifting M toward the source will not increase total wirelength and will decrease some source-sink pathlengths and and shift capacitance along some source-sink paths closer to source. Intuitively, this is the proof behind our next lemma.

**Lemma B3:** In the optimal tree  $T^*$ , let M be an MS not containing  $n_0$ . Then |Far(M)| > |Near(M)|.

**Proof:** By Lemma B2,  $|Far(M)| \ge |Near(M)|$ . Suppose that the exact equality |Far(M)| = |Near(M)| holds. Lemma B2 then implies that each endpoint of M has a near branch incident to it as in Figure 17(a) (otherwise, M would contain a subsegment S with all but one endpoint of M and having |Near(S)| > |Far(S)|.) In Figure 17(b) we show how M can be shifted toward the source without increasing total wirelength, while reducing source-sink pathlengths to nodes on the near branches of M and shifting capacitance toward the source for nodes on the far branches of M. Consequently, moving M will reduce delay to all sinks in  $T_{q_0}^*$  and leave delay to all other sinks unchanged (or reduced if the shift reduces total wirelength), thereby contradicting the optimality of  $T^*$ .

**Lemma B4:** In the optimal tree  $T^*$ , any maximal segment must contain either the source or a sink.

**Proof:** (See Figure 18.) Let M be a lowest maximal segment in  $T^*$  which does not contain either the source or a sink, i.e., every MS that is topologically below M contains a sink. Let  $q_0$  be the entry point to M and let  $p_0$  be the parent node of  $q_0$  in  $T^*$ . Consider the possibility of shifting M, either toward the source or away from the source, without passing over any node in  $T_{q_0}^*$  which is not in M. Without loss of generality, assume that M is a vertical segment with x-coordinate  $x_0$ , and with the near side of M having  $x < x_0$ . Let  $x_1 < x_0$  be the be the closest value to  $x_0$  on the near side of M such that shifting M to  $x = x_1$  would cause M to intersect a node that is in  $T_{q_0}^*$  but not in M. Similarly, let  $x_2 > x_0$  be the closest value to  $x_0$  on the

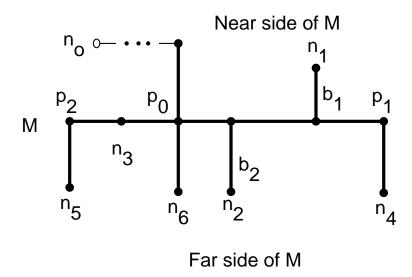

(resp. far) branches. In addition, a sink located on M is defined to be a far branch off of M if none of its children are located on the far side of M (i.e., it is not the entry point to a larger far branch). For any segment S, we use Near(S) (resp. Far(S)) to denote the set of near (resp. far) branches off of the maximal segment containing S. Figure 15 gives an example of an MS M with endpoints  $p_1$  and  $p_2$ , entry point  $p_0$ , and four branches, including near branch  $b_1$ , far branch  $b_2$ , and a far branch consisting only of sink  $n_3$ .

Figure 15: Example of a maximal segment M with entry point  $p_0$ , one near branch  $b_1$ , and four far branches, including  $b_2$ . Note that by definition,  $n_3$  forms a far branch with no edges. Also, edge  $(p_0, n_6)$  does not form a far branch off of M because  $p_0$  is not an entry point to the MS containing  $(p_0, n_6)$ .

Lemmas B2 and B3 establish some properties that must hold for any maximal segment in  $T^*$ . Lemma B4 then uses these properties to show that each maximal segment in  $T^*$  will have a sink located on it. An immediate corollary of Lemma B4 is a generalization of the classic result of Hanan [17] to the Elmore delay objective. (Hanan's original theorem may be viewed as a special case of this Corollary with the driver on-resistance  $r_d \to \infty$ .)

**Lemma B2**: In the optimal tree  $T^*$ , let  $q_0$  be the entry point to a maximal segment M not containing  $n_0$ . Let S be any segment contained in M and having  $q_0$  as an endpoint. Then  $|Far(S)| \ge |Near(S)|$ .

**Proof:** By contradiction. Let S be the smallest segment in M with  $q_0$  as an endpoint so that Near(S) > Far(S). Then a portion of  $T^*$  between  $n_0$  and q' looks like Figure 16(a). Label the branches  $b_1, \ldots, b_j$  in order from entry point  $q_0$ . Figure 16(b) shows how we can shift segment S topologically toward the source; this effectively shifts wire from each near branch to a far branch with is topologically closer to the source (i.e., with a smaller label). Shifting S does not affect tree  $cost^{23}$ , and source-sink path lengths will be unchanged to all sinks except those connected to the tree through branches in Near(S), which will have reduced source-sink path lengths. Consequently, the shift will decrease delay to all sinks below  $q_0$  in  $T^*$  and

<sup>&</sup>lt;sup>23</sup>Unless  $q_0$  is an endpoint for the MS containing edge  $(p, q_0)$ , in which case tree cost will decrease.

will be minimized at x = 0 or x = c. However, we assumed that a is connected to (p, b) and so  $x \neq q = 0$ . The only exception occurs if p has no parent, i.e.,  $p = n_0$ . Since e = (p, b) is an arbitrary edge in  $T^* \setminus a$  to which a is connected, it must be that a makes a closest connection to any edge it is connected to (unless a's parent is  $n_0$ ).

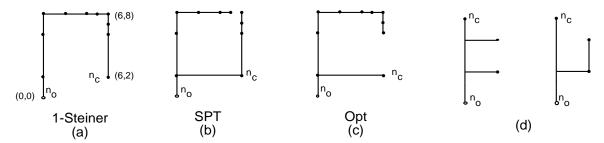

Straightforward corollaries of Lemma B1 include: (i) that any non-source node in the optimal delay tree  $T^*$  must have degree  $\leq 4$ , and (ii) that the possible configurations of edges incident to a Steiner node  $q \in T^*$  are restricted to the five configurations shown in Figure 22. Note that Lemma B1 by itself is not sufficient to prove that BB-SORT-C will return the optimal delay tree. For example, if  $T^*$  connects a four-pin net into an "H" with two degree-3 Steiner nodes  $q_1$  and  $q_2$  (see Figure 14), then the parent of each non-source node v is connected by a closest connection to  $T^* \setminus v$ . However,  $T^*$  cannot be constructed by BB-SORT-C since the "H" cannot be formed by adding the three sinks sequentially by closest connections to the growing tree.

Figure 14: Example of a routing tree T which cannot be constructed by algorithm BB-SORT-C, but which satisfies the condition that each non-source node  $v \in T$  makes a closest connection to each incident edge in  $T \setminus v$ .

#### B.3. Hanan Grid Proof for Steiner Nodes in $T^*$

We root any routing tree T at the source  $n_0$  and for any node  $v \in T$  define  $T_v$  to be the subtree of T rooted at v. We define a segment to be a contiguous set of straight edges in T which are either all horizontal or all vertical; a maximal segment (MS) is a segment not properly contained in any other segment. Let M be an MS in T. The node in M closest to  $n_0$  on a source-sink path containing M is called the entry point to M. A segment containing all points in M to one side of a node v located on M is a half segment with respect to v, and a half segment with respect to the entry point of M is called a branch. A branch v is called a branch off of MS v if v contains v entry point and is perpendicular to v. Note that any given segment, v will divide the plane into two half-planes. If v does not contain v0, then the half-plane containing the edge between v0 entry point and its parent is called the near side of v0 (because it is "nearer" to the source), and the other half-plane is called the far side of v0. (If v0 contains the source, the near and far sides of v0 can be labeled arbitrarily.) Branches off of v0 that are located on its near (resp. far) side are called near

for  $x^2$  is concave in terms of x.

Consider the contribution made by the edge (x, a) to Elmore delay at various sinks  $n_j \in T^*$ . First, consider the case of  $n_j \in T_a^*$ . Delay  $t(n_j)$  is the sum of four functions:  $f_1 = \text{delay from } n_0 \text{ to } p$ ;  $f_2 = \text{delay from } p$  to x due to capacitance in  $T^* \setminus b$ ;  $f_3 = \text{delay from } p$  to x due to capacitance in edge (b, q) and  $T_b^*$ ; and  $f_4 = \text{delay from } x$  to  $n_j$ . Simple application of the Elmore formula for these four functions gives

$$f_1 = K_0 + K_1(K_2 + a - x) (2)$$

$$f_2 = x * (\frac{x}{2} + a - x + C_a + c - x + C_c)$$

(3)

$$f_3 = x * (b - q + C_b) \quad \text{if } x \le q \tag{4}$$

$$f_3 = q * (b - q + C_b) \quad \text{if } x \ge q \tag{5}$$

$$f_4 = (a-x)*(\frac{a-x}{2} + C_a) + K_3$$

(6)

where  $K_0$ ,  $K_1$ ,  $K_2$  and  $K_3$  are constants. To be precise,  $K_0$  is the sum of resistance/capacitance products along the  $n_0$ —p path;  $K_1$  is the sum of resistances from  $n_0$  to p;  $K_2$  equals the total capacitance in  $T_p^*$  minus the edge (x, a); and  $K_3$  is the delay from a to  $n_j$ . Function  $f_1$  is linear in x, while  $f_2$  and  $f_4$  are quadratic in x. The equation for  $f_2 + f_4$  has a negative coefficient for  $x^2$ , and so  $f_2 + f_4$  is concave. Function  $f_3$  is linear and increasing for  $x \leq q$  and remains constant for  $x \geq q$ ; thus,  $f_3$  is also concave in x. Consequently,  $t(n_j) = f_1 + f_2 + f_4 + f_3$  is concave in x.

If  $n_j \in T_c^*$  then  $f_1$ ,  $f_2$ , and  $f_3$  are identical to the case of  $n_j \in T_a^*$ . Function  $f_4$  equals  $(c-x)*(\frac{c-x}{2}+C_c)+K_2$ , where  $K_2$  is the delay from c to  $n_j$ . Again,  $f_1$ ,  $f_3$ , and  $f_2+f_4$  are each concave in x, and so  $t(n_j)$  is concave in x.

If  $n_j \in T_b^*$  or  $n_j = q$ , we can express delay to  $n_j$  in terms of three functions  $f_1$ ,  $f_2$  and  $f_3$ . The definitions of  $f_1$  and  $f_2$  are the same as for  $n_j \in T_a^*$ , and  $f_3$  gives the delay from p to  $n_j$  due to capacitance in  $T^* \setminus a$ . The equation for  $f_1$  is identical to that for  $n_j \in T_a^*$ , while  $f_3$  is a constant in terms of x. Hence,  $f_1$  and  $f_3$  are concave. For  $f_2$ , we have

$$f_2 = x * (a - x + C_a) \quad \text{if } x \le q \tag{7}$$

$$= q * (a - x + C_a) \quad \text{if } x \ge q \tag{8}$$

Any continuous, piece-wise differential function of a real variable is concave as long as its first derivative is monotone decreasing. It is clear that this property holds for  $f_2$ , except possibly at x = q. Let  $f'_2$  be the derivative of  $f_2$ . Then for x < q,  $f'_2(x) = a - 2x + C_a$ , and for x > q,  $f'_2(x) = -q$ . Substituting q for x in these equations, we see that  $f'_2$  is indeed decreasing at x = q (because a > x). Consequently,  $f_2$  is concave in x and so is  $t(n_j)$ .

Delay to any other sink in  $T^*$  is linear (and thus concave) in x. Therefore, because f is a non-negative linear combination of concave functions over the interval  $0 \le x leq c$ , it is also concave over this interval and

an edge  $e \in T \setminus v$  to which v is connected, then v is said to make a closest connection to e in T.

#### **B.2.** Proof of Closest Connections in $T^*$

**Lemma B1:** Let x be the parent of node  $a \in T^*$ ,  $a \neq n_0$ . Then either  $x = n_0$ , or else x is located at the closest connection between a and each edge in  $T^* \setminus a$  that is incident to a in  $T^*$ .

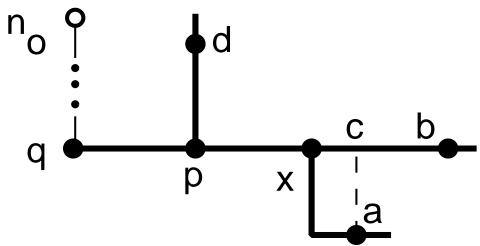

**Proof:** (See Figure 13.) Let  $e = (p, b) \in T^* \setminus a$  be an edge to which a is connected at node x in  $T^*$ . Let c be the location of the closest connection between a and e. Assume that node p has degree three (the proof is nearly identical if p has degree four), and let q be p's parent and d be the other child of p besides x. In our proof, we also assume that  $p \neq n_0$  and that p is the closest point to a on edge edge (q, p). The other cases are handled easily by analogous proofs.<sup>22</sup>

Figure 13: Proof of Lemma B1: Node  $a \in T^*$  is connected to edge  $(p, b) \in T^* \setminus a$  at node x; either  $x = p = n_0$  or x = c, where c is the closest connection between a and (p, b).

For convenience, we overload x, a, b, c, and p to also represent the respective path lengths from q to these nodes or locations. Even though c is not necessarily a node in  $T^*$ , we use  $T_c^*$  to represent the subtree of  $T^*$  below location c. Finally, we use  $C_a$ ,  $C_b$ , and  $C_c$  to represent the tree capacitance in subtrees  $T_a^*$ ,  $T_b^*$ , and  $T_c^*$ , respectively.

It is easy to see that  $x \leq c$ , since otherwise moving x forward to c will reduce or leave unchanged all subtree costs (i.e., capacitance terms) and all path lengths (i.e., resistance terms). We will show that delay function f is concave in terms of x for  $0 \leq x \leq c$ . Our proof invokes several facts from elementary analysis: (1) any concave function defined over a real interval will be minimized at one of the two end points of the interval; (2) multiplying any concave function by a positive constant also gives a concave function; (3) the sum of two concave functions is also concave; and (4) any quadratic function of x with a negative coefficient

$<sup>^{22}</sup>$ If  $p = n_0$ , then a similar argument shows that f is concave between  $p = n_0$  and c, and will be minimized at one of these two points. If some point on (q, p) is closer to a than p, then a similar proof shows concavity for f over the interval between p and c. In this case, it is easy to show  $x \neq p$  because connecting a to a closer point on (q, p) produces a lower value for f than connecting it to p, and so x must be located at c.

Clean\_Up for each node v' added to the queue in Line 6, and the total number of calls to Clean\_Up is  $O(k^2)$ .

## Appendix B: Optimal Steiner ERTs

For minimum-cost Steiner trees, the classic result of Hanan [17] restricts the choice of Steiner nodes to at most  $|N| \cdot |N-1|$  points (the "Hanan grid") and enables finite branch-and-bound methods to determine optimal solutions. Here, we prove an analogous result for trees minimizing any weighted average of sink Elmore delays. Like Hanan, we show that any tree containing a Steiner node which is not a vertex in the Hanan grid can have its edges and Steiner nodes shifted to lie on the Hanan grid. However, we do not shift edges in the same way as Hanan (the edge shifts he uses can be suboptimal in terms of Elmore delay). Indeed, the result of, e.g., Lemma B1 below is obvious when minimizing tree cost, but requires a fairly involved proof when minimizing Elmore delay. Our development of the Hanan grid result becomes complete with the proof of Lemma B4 below. In Lemma B5, we extend our result to show that the branch-and-bound SORT-C method described in Section 4.4 returns the optimal delay Steiner tree.<sup>21</sup>

#### **B.1.** Definitions

We assume that all delays are defined in terms of Elmore delay. We seek to characterize the *optimal* Steiner tree over N, denoted by  $T^*$ , which minimizes the weighted sum of sink delays  $f = \sum_{i=1}^k \alpha_i \cdot t(n_i)$ , with each  $\alpha_i > 0$ . (The case of some  $\alpha_i = 0$  is effectively handled by setting these  $\alpha_i$  to a small positive value.) We assume that  $T^*$  contains no Steiner nodes with degree < 3. For convenience, we normalize time and distance so that unit wire resistance and unit wire capacitance are both equal to one. We also consider a tree to be defined as a set of nodes and edges, so that the notations  $v \in T$  for node v and  $e \in T$  for edge e are well defined. An edge that is completely vertical or horizontal is called a  $straight\ edge$ ; any other edge is called an L-shaped edge.

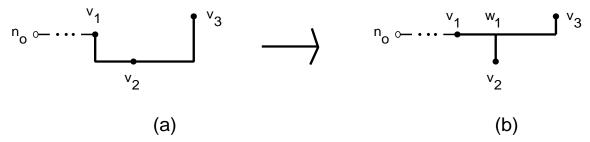

The closest connection between three nodes is the location of the single Steiner node in a minimum-cost Steiner tree over the three nodes. This location is unique and has coordinates given by the medians of the x- and the y- coordinates of the three nodes (if the minimum-cost Steiner tree is a chain, then the closest connection is the middle node). The closest connection between a node v and an edge e is the closest connection between v and the two endpoints of e. Assume that a Steiner tree T over N is rooted at  $n_0$ . We define  $T \setminus v$  to be the tree induced by removing node v and all of its descendants from T, and then removing all degree-2 Steiner nodes from the resulting tree. We say that node  $v \in T$  is connected to an edge  $e \in T \setminus v$  if its parent node in T is located on edge e. If parent(v) is located at the closest connection between v and

$<sup>^{21}</sup>$ The following clarifications should be made about our results. First, we allow the source pin  $n_0$  to have degree > 4, which is in general physically impossible, but can be approximated by merging wires close to the source. Second, the optimal delay Steiner trees will not always be planar, as this is not required by our definition of an optimal-delay tree.

constructs a tree which GSR processes in  $\Omega(k^2)$  time [6]. GSR in practice, however, seems to exhibit close to linear-time complexity, because multiple calls to procedure Clean\_Up occur for very few nodes.

**Theorem A2:** (i) GSR returns a tree containing no V's and no U's, and (ii) GSR runs in  $O(n^2)$  time in the worst case.

**Proof:** (i) Since GSR checks for V's and U's at each node in the tree, the output tree will contain a V or U only if GSR creates one at a node that has already been traversed. A new V or U can be produced at a node v only if the  $n_0 - v$  path length is increased (which is impossible by Theorem 1) or if nodes are removed from the  $n_0 - v$  path.

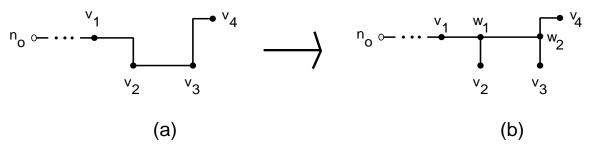

Removing a V at Line 8 in Figure 9 will not introduce a new V or U at  $v_2$  (in Figure 7), because the  $n_0 - v_2$  path length is unchanged and a new Steiner point  $w_1$  is added to this path. Removing a V will not introduce a V at  $v_3$  either, because  $v_1w_1v_3$  is not a V. A U may remain at  $v_3$  after removing the V, but this will be detected later at Line 9.

Removing a U at  $v_4$  in Figure 8 can only introduce a new V or U at  $w_2$ ,  $v_4$ , or one of their descendants, because all other nodes have unchanged source-sink path lengths and no fewer Steiner nodes on their source-sink paths. The subroutine **Clean\_Up** checks for V's and U's at  $w_2$  and  $v_4$ , and recursive calls to **Clean\_Up** will eventually terminate because a new V or U can be introduced only by reducing the number of nodes on the  $n_0$ - $v_4$  path.

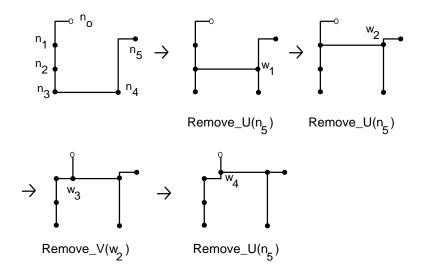

Figure 12: Example in which removing a U at  $n_5$  requires two subsequent U-removals and a V-removal to complete the **Clean\_Up** procedure.

Figure 12 shows how Clean\_Up can require several recursive calls before terminating. However, for any node v', a call to Remove\_U(v') will introduce a new V or U at v' or parent(v') only if it reduces the number of nodes on the  $n_0-v'$  path. Because any Steiner tree connecting k+1 points can contain at most 2k nodes in total, there are O(k) nodes on the  $n_0-v'$  path. Hence, at most O(k) calls can be made to

lengths.

(iii) Assuming constant technology parameters<sup>19</sup>, removing a U or a V can affect Elmore delay along a source-sink path in only three ways: a) changing the length of the path; b) changing tree capacitances along the path (i.e., increasing the wirelength of branches off from the path); and c) shifting tree capacitances along the path (changing where branches connect to the path). Removing a V will reduce some path lengths, reduce tree capacitances, and shift tree capacitances closer to the source, thereby reducing Elmore delay to all pins in the tree. Removing a U reduces path length to node  $v_4$  in Figure 8 and shifts tree capacitance closer to the source for nodes  $v_2$ ,  $v_3$ , and  $v_4$ . (For  $v_3$ , the capacitance that met the  $n_0$ - $v_3$  path at  $v_3$  now meets the path at  $w_1$  and  $w_2$ .) The only effect of removing low-degree Steiner nodes is to reduce total wirelength, which cannot increase delay to any sink.

Figure 10: An example of a net with a source and five sinks for which processing the U's in a bottom-up order returns a tree with one remaining U.

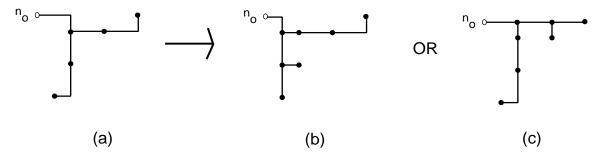

Figure 11: The GSR algorithm with input (a) can produce either tree (b) or tree (c), depending on the order in which the U's are processed.

The order in which U's are removed from the tree is important. If the U's were processed in a bottom-up rather than a top-down order, then new U's could be introduced and the output tree might still contain U's, as in Figure 10.<sup>20</sup> Note also that two different top-down orderings can produce different outputs (although neither will contain any U's; see Figure 11).

We now prove that GSR removes all V's and all U's from any input tree, and that its worst-case time complexity is quadratic. Note that we have constructed a class of nets for which the 1-Steiner heuristic

<sup>&</sup>lt;sup>19</sup>I.e., including unit wire resistance, unit wire capacitance, driver resistance, and sink loading capacitances.

<sup>&</sup>lt;sup>20</sup>By "bottom-up" we mean that each node is processed after all of its children in the tree, while a "top-down" ordering implies that each node is traversed before any of its children.

| GSR Algorithm                                              |  |  |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|--|--|

| Input: Steiner tree $T$ with source $n_0$                  |  |  |  |  |  |  |

| <b>Output:</b> Steiner tree $T$ with all $U$ 's removed    |  |  |  |  |  |  |

| 1. Remove all Steiner nodes of degree $\leq 2$ from $T$ ;  |  |  |  |  |  |  |

| $ 2. 	 Q \leftarrow \{n_0\}; $                             |  |  |  |  |  |  |

| 3. While $Q \neq \emptyset$                                |  |  |  |  |  |  |

| $4. 	 v \leftarrow Dequeue(Q);$                            |  |  |  |  |  |  |

| 5. For each node $v' \in children(v)$ do                   |  |  |  |  |  |  |

| 6. $Q \leftarrow Enqueue(v');$                             |  |  |  |  |  |  |

| 7. If there is a $V$ located at $v'$                       |  |  |  |  |  |  |

| 8. Call <b>Remove_V</b> $(v')$                             |  |  |  |  |  |  |

| 9. If there is a $U$ located at $v'$                       |  |  |  |  |  |  |

| 10. Call $\mathbf{Remove\_U}(v')$                          |  |  |  |  |  |  |

| 11. Call $\mathbf{Clean\_Up}(v')$                          |  |  |  |  |  |  |

| 12. Remove all Steiner nodes of degree $\leq 2$ from $T$ ; |  |  |  |  |  |  |

| Subroutine Clean_Up(node: $v'$ )                           |  |  |  |  |  |  |

| C1. If there is a $V$ located at $parent(v')$              |  |  |  |  |  |  |

| C2. Call <b>Remove_V</b> $(parent(v'))$                    |  |  |  |  |  |  |

| C3. If there is a $U$ located at $v'$                      |  |  |  |  |  |  |

| C4. Call <b>Remove_U</b> $(v')$                            |  |  |  |  |  |  |

| C5. Call Clean_Up $(v')$                                   |  |  |  |  |  |  |

| C6. Else                                                   |  |  |  |  |  |  |

| C7. If there is a $U$ located at $parent(v')$              |  |  |  |  |  |  |

| C8. Call $\mathbf{Remove\_U}(parent(v'))$                  |  |  |  |  |  |  |

| C9. Call $\mathbf{Clean\_Up}(parent(v'))$                  |  |  |  |  |  |  |

Figure 9: Pseudo-code for the Global Slack Removal (GSR) algorithm. Local variables include a queue Q and nodes v and v'. We use children(v) to denote the set nodes with children of v when the tree is rooted at  $n_0$ ; parent(v) denotes the parent of v in the rooted tree. The subroutine  $\mathbf{Remove\_V}(v)$  removes a V located at v as in Figure 7 and  $\mathbf{Remove\_U}(v)$  removes a U located at v as in Figure 8.

We now show that the tree returned by GSR dominates the input tree in terms of total tree cost, path length from the source to each sink, and Elmore delay at each sink. Let cost(T) denote the cost of routing tree T.

**Theorem A1:** Given any tree T as input, GSR will return a tree T' such that (i)  $cost(T') \leq cost(T)$ ; (ii) for each i > 0, the  $n_0$ - $n_i$  path length in T' is less than or equal to the  $n_0$ - $n_i$  path length in T; and (iii) the Elmore delay  $t_{ED}(n_i)$  at each  $n_i$  in T' is less than or equal to the Elmore delay  $t_{ED}(n_i)$  in T.

**Proof:** (i) Removing a V reduces cost in the routing tree; removing a U as in Figure 8 leaves tree cost unchanged; and by the triangle inequality the removal of a low-degree Steiner point will either reduce cost or leave it unchanged. These are the only operations on the tree by GSR.

(ii) **Remove\_V** reduces the source-sink path length to  $v_3$  in the V and to all of its descendents; similarly, **Remove\_U** reduces the source-sink path length to node  $v_4$  in the U. Other source-sink path lengths remain unchanged in either procedure. Removing low-degree Steiner nodes does not affect any source-sink path

without any increase in total tree cost or Elmore delay to any sink. In what follows, we use the term 1-Steiner tree to refer to any tree that can be output by the 1-Steiner algorithm.

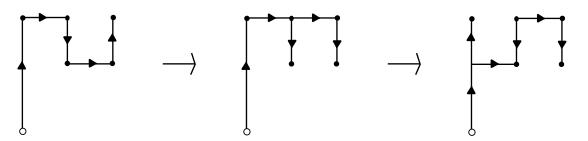

**Definition:** A V is a subpath of three consecutive nodes on a root-leaf path in a routing tree such that the combined edge cost along the subpath is greater than the distance between its two end points (e.g., path  $v_1$ - $v_3$  in Figure 7(a)).

**Definition:** A U is a subpath of four consecutive nodes on a root-leaf path with edge cost greater than the distance between its end points (e.g., path  $v_1$ - $v_4$  in Figure 8(a)).

Figure 7: Removing a single "V" in the GSR Algorithm.

Figure 8: Removing a single "U" in the GSR Algorithm.

Note that the nodes in a V or U can be either Steiner nodes or pins. A V can be removed by introducing a Steiner node which eliminates the overlap between the two adjacent edges, as in Figure 7(b). It is easy to see that, if a U (say  $v_1v_2v_3v_4$ ) does not contain any V's, then its middle edge  $(v_2, v_3)$  must be either completely horizontal or vertical. Consequently, a U containing no V's can be removed by moving the middle edge and adding up to two new Steiner nodes as in Figure 8(b).

Figure 9 describes the GSR algorithm for removing V's and U's from any Steiner tree. We define a U (or V) to be located at node v if v is the node in the U (or V) furthest topologically from the source. Three clarifying points should be noted. (i) GSR uses a "queue" Q which can be implemented arbitrarily as long as each node in the tree is processed before its children. In practice, a simple depth-first ordering suffices. (ii) The procedure **Remove\_U** is invoked only for U's not containing any V's, and is executed as in Figure 8. (iii) All low-degree Steiner nodes of degree  $\leq 2$  are clearly superfluous and are removed, since more U's can be found if they are deleted at the outset. Because U removal can introduce additional low-degree Steiner nodes, they are again removed at the end of the algorithm.

delay objective to connect the remaining sinks). The SERT heuristic can also be applied before critical path information becomes available (an alternative is the ERT spanning tree heuristic, which has lower time complexity but does not introduce Steiner nodes). For nets on non-critical paths, minimizing wire length can take precedence over minimizing delay, hence traditional minimum-cost Steiner heuristics such as 1-Steiner [22] will are likely to be preferred.

Our heuristics which optimize Elmore delay directly are near-optimal in terms of SPICE-computed delay: we showed that our methods give Elmore delay that is nearly optimal, and we also showed that Elmore delay-optimal trees have nearly optimal SPICE delay. For spanning trees with five pins, we estimate that the optimal tree according to Elmore delay will be between 3% and 10% above SPICE-optimal, depending on the technology. Given that our SERT-C heuristic is between 0% and 5% above optimal in terms of Elmore delay for five-pin nets, we estimate that the SPICE delay suboptimality of our SERT-C heuristic ranges from 3% for MCM to about 12% for 0.5  $\mu$ m and about 15% for 1.2 and 2.0  $\mu$ m CMOS IC technologies.

Current work addresses interesting extensions of the CS-Steiner and ERT approaches to incorporate wiresizing, address general-cell layout with arbitrary routing region costs, and exploit the inherent parallelizability of our approaches. Similar approaches may also apply to clock routing, although the extension is non-trivial because of larger net sizes and the addition of a minimum skew objective. Finally, we leave as an open problem the reduction in time complexity of the ERT constructions.

## 6 Acknowledgements

We are grateful to the authors of [38] for use of their Two-Pole simulator code. Professor Ernest S. Kuh and Dr. Kamal Chaudhary provided many helpful comments regarding modeling and experimental methodology. Mr. Ashok Vittal of UC Santa Barbara gave many helpful comments and criticisms on the proofs in an earlier draft, and we also thank the anonymous referees for many detailed comments. Professors Jim Aylor and Michael Shur, and Mr. Sudhakar Muddu, all provided invaluable assistance with SPICE simulation methodology. Part of this work (ABK) was performed during a Spring 1993 sabbatical visit to UC Berkeley; support from NSF MIP-9117328 and the hospitality of Professor Ernest S. Kuh and his research group is gratefully acknowledged.

# Appendix A: Global Slack Removal

Recall from Section 3.1 that Global Slack Removal (GSR) is an efficient post-processing enhancement to the CS-Steiner approach. The worst-case complexity of GSR is  $O(k^2)$ , although we believe the average-case complexity to be very close to O(k). (GSR) is a linear-time postprocessing enhancement to the CS-Steiner approach. GSR shifts edges in the 1-Steiner output to maximize the monotonicity of all source-sink paths

|           | IC1    |          |        |          | IC2              |          |         |          |

|-----------|--------|----------|--------|----------|------------------|----------|---------|----------|

|           | N      | = 5      | N      | N  = 7   |                  | N  = 5   |         | = 7      |

|           | delay  | $\cos t$ | delay  | $\cos t$ | delay            | $\cos t$ | delay   | $\cos t$ |

| SORT-C    | 1.0    | 1.111    | 1.0    | 1.112    | 1.0              | 1.161    | 1.0     | 1.158    |

| SERT-C    | 1.042  | 1.046    | 1.083  | 1.047    | 1.049            | 1.120    | 1.114   | 1.106    |

| (Std Err) | (.004) |          | (.006) |          | (.006)           |          | (.009)  |          |

| 1-Steiner | 1.117  | 1.0      | 1.200  | 1.0      | 1.228            | 1.0      | 1.362   | 1.0      |

|           |        | IC       | C3     | MCM      |                  |          | CM      |          |

|           | N      | = 5      | N      | = 7      | N  = 5 $ N  = 5$ |          | = 7     |          |

|           | delay  | $\cos t$ | delay  | $\cos t$ | delay            | $\cos t$ | delay   | $\cos t$ |

| SORT-C    | 1.0    | 1.175    | 1.0    | 1.165    | 1.0              | 1.296    | 1.0     | 1.262    |

| SERT-C    | 1.046  | 1.140    | 1.112  | 1.112    | 1.000            | 1.296    | 1.001   | 1.256    |

| (Std Err) | (.006) |          | (.010) |          | (.000)           |          | (.0001) |          |

| 1-Steiner | 1.275  | 1.0      | 1.429  | 1.0      | 1.455            | 1.0      | 1.634   | 1.0      |

Table 11: Empirical study of average sub-optimality of the SERT-C heuristic in terms of Elmore delay, using IC1, IC2, IC3 and MCM parameters. Simulations were run on 200 random nets for each net size. Delay is normalized to BB-SORT-C delay and tree cost is normalized to 1-Steiner cost. Standard errors for average SERT-C delays are shown in parentheses.

### 5 Conclusions

We have addressed a critical-sink routing tree (CSRT) formulation which arises when critical-path information becomes available during the timing-driven layout process. Two new classes of CSRT constructions are proposed: (i) the CS-Steiner method, which modifies a minimum Steiner tree to accommodate an identified critical sink, and (ii) the SERT-C method, which begins with a connection from the source to the critical sink and then grows a tree so as to minimize the increase in Elmore delay to the critical sink. Each of these algorithms is efficient, and offers very significant performance improvements over existing performance-driven routing tree constructions. We note that the greedy "Elmore routing tree" (ERT) approach underlying the SERT-C algorithm seems quite powerful. In particular, the approach encompasses a "generic" SERT Steiner router which outperforms all previous performance-driven routing algorithms in the literature. The ERT approach is also the first to consistently, and directly, optimize the Elmore delay formula itself, rather than an objective which heuristically abstracts Elmore delay. Since Elmore routing trees are efficiently computed, our approaches may lead to basic new utilities that can be integrated within existing performance-driven global routing codes. Assessments of the near-optimality of our Steiner constructions have led to a new characterization of Elmore-optimal Steiner trees, and to a new decomposition theorem for minimum-cost and minimum-Elmore delay Steiner trees; both of these results are of independent interest.

Which of our routing heuristics is most useful will depend on the application. The CS-Steiner heuristics H0 and HBest yield the smallest delay values for a single critical sink, but have high time complexity which may make them impractical for repeated wiring of large nets. Our SERT-C heuristic has time complexity of only  $\Theta(k^2 log k)$  and is readily extended to the case of nets with multiple critical sinks (e.g., first apply SERT with its min-max delay objective to the critical sinks, then apply SERT-C with a weighted average

mines optimal trees with respect to any given linear combination of Elmore delays to critical sinks. We also present an entirely new "peeling decomposition" of any optimal Elmore delay Steiner tree into a sequence of subtrees, each of which adds a sink by a "closest connection" to some edge in the previous tree.

When the driver resistance  $r_d$  is very large, the optimal Elmore delay tree is a minimum-cost Steiner tree (recall Equation (1); also see [5]). As a consequence, our results extend very naturally to the well-studied problem of minimum-cost Steiner tree construction, and the restriction of Elmore-optimal Steiner nodes to the Hanan grid both generalizes and extends Hanan's original results. (As Hanan did for minimum-cost Steiner trees, we prove that every Steiner node in an Elmore-optimal tree is connected to one sink by a horizontal segment of edges, and to another sink by a vertical segment of edges. However, our techniques (Lemmas B1 - B4 in Appendix B) are much more powerful in order to address the optimality of the Steiner tree with respect to Elmore delay.) Our peeling decomposition and its extension to minimum-cost Steiner trees are of independent interest since they provide both a new characterization of, and a new means of generating, such trees.

Based on the results of Appendix B, we achieve a simple modification to our BBORT method which finds an optimal Steiner routing tree for any linear combination of Elmore delays to critical sinks. Rather than considering connections from each sink  $n_i$  outside the current tree to each sink  $n_i$  inside the tree as in BBORT, the Branch-and-Bound method for Steiner Optimal Routing Trees with Critical Sinks (BB-SORT-C) considers connections from  $n_j$  to each edge created when  $n_i$  was added to the tree. In other words, each node  $n_i$  already contained in T is replaced as a possible connection point by each of the edges created when  $n_i$  was added to the tree earlier. Again we use branch-and-bound pruning to reduce the complexity of the search.<sup>17</sup>

Table 11 compares Elmore delay for trees constructed by the SERT-C algorithm with optimal Elmore delay trees found by BB-SORT-C for each of the four technologies. The size of nets used in the comparison is limited to nets with six sinks (i.e., seven pins) because of the exponential time complexity of BB-SORT-C. For nets with seven pins, our results show that SERT-C achieves Elmore delay that is on average within 11.1% of optimal for the IC1 technology; results for IC2, IC3, and MCM parameters are very similar. The table also gives average tree costs for our constructions and the standard error of our estimate for the ratio between SERT-C and SORT-C delays. We see that the SERT-C algorithm does not perform as well as the ERT algorithm in terms of nearness to optimality for the types of delay measures we have considered. Nevertheless, our results provide strong guidance for future efforts in performance-driven routing: even if future work improves the near-optimality of critical sink routing constructions, Table 11 shows that any future improvement in Elmore delay will be at most from 8% to 12% for nets with up to seven pins.

<sup>&</sup>lt;sup>17</sup>Because we consider connections to up to three edges for each sink in the growing tree, our BB-SORT-C will introduce some redundancies in the tree topologies; we check for possible redundancies and prune the search at each redundant tree we find

<sup>18</sup> Average running times for each 5-pin net (in seconds) are 0.006 (BB-SORT-C), 0.0004 (SERT-C), 0.0014 (SERT), and 0.0012 (1-Steiner). Average running times for 7-pin nets are 0.44 (BB-SORT-C), 0.0007 (SERT-C), 0.0055 (SERT) and 0.0035 (1-Steiner).

|            |              | IC                   | C1                                                                                             |               | IC2          |                      |                            |               |

|------------|--------------|----------------------|------------------------------------------------------------------------------------------------|---------------|--------------|----------------------|----------------------------|---------------|

|            | N  =         | = 5                  | N  = 7                                                                                         |               | N  = 5       |                      | N  = 7                     |               |

|            | delay        | $\cos t$             | delay                                                                                          | $\cos t$      | delay        | $\cos t$             | delay                      | $\cos t$      |

| ORT        | 1.0          | 1.103                | 1.0                                                                                            | 1.133         | 1.0          | 1.140                | 1.0                        | 1.175         |

| ERT        | 1.007        | 1.104                | 1.017                                                                                          | 1.142         | 1.010        | 1.159                | 1.022                      | 1.215         |

| (Std Err)  | (.0015)      |                      | (.0021)                                                                                        |               | (.0017)      |                      | (.0022)                    |               |

| SPT        | 1.085        | 1.290                | 1.130                                                                                          | 1.395         | 1.058        | 1.290                | 1.096                      | 1.395         |

| MST        | 1.169        | 1.0                  | 1.282                                                                                          | 1.0           | 1.272        | 1.0                  | 1.451                      | 1.0           |

|            |              |                      |                                                                                                |               |              |                      |                            |               |

|            |              | I                    | <b>3</b>                                                                                       |               |              | M                    | СМ                         |               |

|            | N            | I(<br>= 5            |                                                                                                | = 7           | N  :         | M(= 5                |                            | = 7           |

|            | N  delay     |                      |                                                                                                | = 7 $cost$    | N :          |                      |                            | = 7<br>cost   |

| ORT        |              | = 5                  | N                                                                                              |               |              | = 5                  | N  =                       |               |

| ORT<br>ERT | delay        | $= 5$ $\cos t$       | N  delay                                                                                       | cost          | delay        | $= 5$ $\cos t$       | N  = delay                 | cost          |

|            | delay<br>1.0 | = 5<br>cost<br>1.146 | $ \begin{array}{ c c } \hline  N  \\ \hline \text{delay} \\ \hline 1.0 \\ \hline \end{array} $ | cost<br>1.190 | delay<br>1.0 | = 5<br>cost<br>1.432 | N  = delay 1.0             | cost<br>1.547 |

| ERT        | 1.0<br>1.011 | = 5<br>cost<br>1.146 | $ \begin{array}{c c}  N  \\ \hline \text{delay} \\ \hline 1.0 \\ \hline 1.027 \\ \end{array} $ | cost<br>1.190 | 1.0<br>1.009 | = 5<br>cost<br>1.432 | N  = delay<br>1.0<br>1.024 | cost<br>1.547 |

Table 10: Elmore delays and wirelengths of various constructions using IC1, IC2, IC3 and MCM parameters. Simulations were run on 200 random nets for each net size. Tree cost is normalized to MST cost and delays are normalized to ORT delay. Standard errors for ERT delay are shown in parentheses.

of 0.21%, indicating a 95% confidence interval between 1.3% and 2.1% (i.e., an interval of within two times the standard error of the average).

Technology IC3 gives our worst results in terms of the optimality of ERTs. For the IC3 parameters and 7-pin nets, ERT gives an average value within 2.7% of ORT with a 95% confidence interval of between 2.2% and 3.2%. For MCM parameters, the Elmore-based ERT constructions are also very close to optimal: on average, they are within 2.4% of ORT delay for 7-pin nets. Finally, our tables compare the delays of the SPT construction with those of the ERT and MST solutions; the SPT outperforms the MST, but not the ERT, in terms of Elmore delay.

#### 4.4 Elmore-Optimality of Steiner Tree Constructions

We have shown that our spanning tree constructions are nearly optimal when when we optimize the maximum Elmore delay over all sinks in the net. Because Steiner constructions give lower delay values than spanning trees in general, we close this section with a similar comparison for our SERT-C and SERT Steiner constructions. At first, this comparison appears very complicated because there are infinitely many possible locations for Steiner nodes. Indeed, while it is well-known that the result of Hanan [17] restricts the choice of Steiner nodes in a minimum-cost Steiner tree to at most  $k \cdot (k+1)$  points, no such characterization has been established for a Steiner tree with optimal Elmore delay. In Appendix B, we present new theoretical results which restrict the choice of Steiner nodes in Elmore-optimal trees to exactly the same finite "Hanan grid" that contains the Steiner nodes of minimum-cost trees. This allows a finite algorithm which detererror of the average difference between ERT and ORT delays is equivalent to the standard error of average ERT delay.

avoids testing any topology more than once by requiring that sinks be added in the order of a breadth-first traversal of the tree (if two sinks are connected to the same parent node, then the sink with smaller index must be added to the tree first). It is easy to verify that according to this convention, any tree topology will imply a unique ordering of the sinks. Consequently, although BBORT tries all possible orderings of sinks, it calculates delay at most once for each tree topology. In Figure 6, lines 7 through 9 comprise the core of the branch-and-bound methodology used: if the delay in the current tree T' is greater than or equal to  $t_{min}$  (the current best-known delay for a complete tree), then procedure Add\_Edges terminates and the algorithm backtracks. Otherwise, if T' is a complete tree, then  $t_{min}$  is set to the delay of T', or if T' is a partial tree, then Add\_Edges recursively adds more edges to T'.

```

BBORT Algorithm

Input: signal net N with source n_0 \in N

Output: optimal-delay tree T_{opt} over N

1. T = (V, E) = (\{n_0\}, \emptyset)

2. t_{\min} = \infty

3. Call Add_Edges(T)

Output T_{opt}

Procedure Add_Edges(Tree: T = (V, E))

While there exist v \in V and u \notin V such that

T' = (V \cup \{u\}, E \cup \{(u, v)\}) is a new tree topology Do

Compute tree delay t(T')

If t(T') < t_{\min} Then

7.

If |T'| = |N| Then T_{opt} = T'; t_{min} = t(T')

8.

9.

Else Call Add_Edges(T')

```

Figure 6: Branch-and-Bound Optimal Routing Tree (BBORT) algorithm (recursive implementation).

To track all of the above simulation results, we have run BBORT trials on random sets of 200 nets for each of several net sizes. Our inputs are evaluated using the same four sets of technology parameters discussed previously. Table 10 compares Elmore delays of the BBORT and ERT constructions, as well as of the minimum spanning tree (MST) and shortest path tree (SPT) constructions, for each of the four technologies. Delay for each tree is normalized to the ORT delay of the same net. Tree costs are similarly normalized to the MST cost of each net.

In the table, we see that ERTs over seven pins in the IC1 technology have an average maximum Elmore delay only 1.7% greater than optimal, while MSTs have average Elmore delay 28.2% greater than optimal. For smaller nets, ERTs are even better: for nets with five pins, ERT delays are only 0.7% above optimal on average, while MSTs are 16.9% above optimal. Our confidence in the average difference computed between ERTs and ORTs is very high: for instance, the 1.7% difference obtained for 7 pins has a standard error<sup>16</sup>

<sup>&</sup>lt;sup>15</sup>The SPT construction is the tree which minimizes cost subject to each source/sink path having minimum length, i.e., it is a Steiner arborescence, or A-tree [11, 30].

<sup>&</sup>lt;sup>16</sup> As used here, the term  $standard\ error$  is defined as follows. For a random variable X, let  $\hat{X} = \sum_{i=1}^{n} X_i$  be an estimator for the expected value of X. The standard error of  $\hat{X}$  is an estimate of its standard deviation over multiple sample sets, and is equal to the standard deviation of X divided by  $\sqrt{n}$ . Because delays are recorded as ratios to the ORT delay, the standard

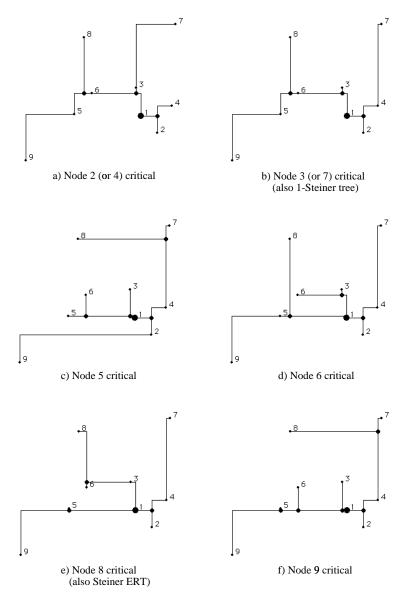

Figure 5: SERT-C tree constructions for a single 9-pin net, showing variation of solution with choice of critical sink  $n_c$ .

#### 4.3 Elmore-Optimality of Spanning Tree Constructions

We have seen that the ERT constructions yield greatly improved signal delay when compared to previous methods. An obvious question is whether we still need to seek methods that better minimize Elmore delay. Thus, we have implemented a branch-and-bound algorithm which finds optimal generic routing trees according to Elmore delay. Starting with a trivial tree containing only the source pin, we incrementally add one edge at a time to the growing tree and evaluate the maximum sink delay. If this value exceeds the maximum sink delay in any complete candidate tree seen so far, we prune the search and backtrack to select a different edge at the previous step. A recursive implementation of this Branch-and-Bound Optimal Routing Tree (BBORT) search is shown in Figure 6. BBORT attempts to add sinks in all possible orders, but

and H0), and it does not require any simulator calls as does HBest.

Figure 4: Example of the progressive SERT Steiner tree construction for a 9-terminal net using IC2 parameters. The source pin is labeled 1, and sinks are numbered in order of distance from the source.

Figures 4 and 5 illustrate the SERT and SERT-C algorithms for a 9-pin signal net using the IC2 technology parameters. Figure 4 shows the progressive growth of the SERT construction. Figure 5 contains the trees produced by SERT-C for the various choices of critical node. The tree constructed when  $n_c$  is node 3 or node 7 is also the 1-Steiner tree, and the tree constructed when  $n_c$  is node 8 is the same as the generic SERT result.

|                        |        | IC                     | C1       | IC       | C2       |

|------------------------|--------|------------------------|----------|----------|----------|

|                        |        | N  = 5                 | N  = 9   | N  = 5   | N  = 9   |

|                        | MST    | 0.645 ns               | 0.984 ns | 0.395 ns | 0.609 ns |

| $\operatorname{Crit}.$ | AHHK   | -9.6%                  | -16.3%   | -13.7%   | -23.0%   |

| Sink                   | ERT    | -12.1%                 | -16.3%   | -19.6%   | -25.9%   |

| Delay                  | 1Stein | 0.549 ns               | 0.848 ns | 0.331 ns | 0.520 ns |

|                        | SERT   | -3.3%                  | -11.6%   | -7.9%    | -19.4%   |

|                        | SERT-C | -5.3%                  | -15.3%   | -13.0%   | -26.5%   |

|                        | MST    | $0.758 \; \mathrm{ns}$ | 1.213 ns | 0.485 ns | 0.792 ns |

| Max                    | AHHK   | -12.4%                 | -19.5%   | -16.5%   | -25.3%   |

| Delay                  | ERT    | -14.5%                 | -21.0%   | -21.4%   | -30.1%   |

|                        | 1Stein | 0.627 ns               | 1.028 ns | 0.393 ns | 0.664 ns |

|                        | SERT   | -4.5%                  | -14.7%   | -8.1%    | -22.0%   |

|                        | SERT-C | -3.0%                  | -8.6%    | -3.8%    | -10.8%   |

|                        | MST    | 1.64 cm                | 2.43 cm  | 1.64 cm  | 2.43 cm  |

|                        | AHHK   | +16%                   | +9%      | +16%     | +9%      |

| Ave WL                 | ERT    | +10%                   | +15%     | +18%     | +25%     |

|                        | 1Stein | 1.48 cm                | 2.18 cm  | 1.48 cm  | 2.18 cm  |

|                        | SERT   | +6%                    | +9%      | +11%     | +18%     |

|                        | SERT-C | +6%                    | +6%      | +15%     | +11%     |

|        |        | IC       | 23                    | MO      | CM      |

|--------|--------|----------|-----------------------|---------|---------|

|        |        | N  = 5   | N  = 9                | N  = 5  | N  = 9  |

|        | MST    | 0.262 ns | 0.403 ns              | 2.82 ns | 4.80 ns |

| Crit.  | AHHK   | -11.5%   | -25.1%                | -22.3%  | -39.2%  |

| Sink   | ERT    | -21.8%   | -29.8%                | -52.8%  | -67.1%  |

| Delay  | 1Stein | 0.218 ns | 0.342 ns              | 2.31 ns | 4.09 ns |

|        | SERT   | -9.2%    | -21.9%                | -41.6%  | -61.6%  |

|        | SERT-C | -16.1%   | -30.7%                | -43.3%  | -66.0%  |

|        | MST    | 0.326 ns | $0.533   \mathrm{ns}$ | 3.86 ns | 7.05 ns |

| Max    | AHHK   | -17.8%   | -27.0%                | -24.1%  | -36.8%  |

| Delay  | ERT    | -23.6%   | -33.2%                | -45.6%  | -60.1%  |

|        | 1Stein | 0.262 ns | 0.444 ns              | 3.06 ns | 5.92 ns |

|        | SERT   | -9.2%    | -24.1%                | -30.1%  | -51.9%  |

|        | SERT-C | -4.6%    | -10.8%                | -14.1%  | -15.4%  |

|        | MST    | 1.64 cm  | 2.43 cm               | 16.4 cm | 24.3 cm |

|        | AHHK   | +16%     | +9%                   | +4%     | 1.07    |

| Ave WL | ERT    | +19%     | +27%                  | +61%    | 2.15    |

|        | 1Stein | 1.48 cm  | 2.18 cm               | 14.8 cm | 21.8 cm |

|        | SERT   | +13%     | +22%                  | +66%    | +127%   |

|        | SERT-C | +16%     | +14%                  | +28%    | +22%    |

Table 9: Two-Pole simulation results for Elmore routing tree variants. Spanning ERT constructions are compared with MST and AHHK; Steiner SERT and SERT-C constructions are compared with 1-Steiner. All choices of critical sink are random, and all results are averaged over 100 random nets. MST and 1-Steiner results are reported in the physical units (nanoseconds or centimeters) while other results are reported as percent differences from corresponding MST or 1-Steiner results.

Since maximum sink delays still decrease, it is likely that overall skew in the routing tree will be reduced even when we treat the critical-sink formulation. Finally, we note that the SERT-C router produces very similar delays and costs compared to the HBest and H0 variants of CS-Steiner discussed in the previous subsection. However, SERT-C is more practical than HBest or H0 since it runs in  $O(k^2 \log k)$  time (versus the  $O(k^3)$  complexity of the best practical implementation of the 1-Steiner heuristic that is called by HBest

$n_i$  as the critical sink.

Variants H0 and HBest significantly reduce delay to the critical sink, particularly in larger nets and for MCM interconnect technology where output driver and wire resistances are low. In other words, the simple strategy of connecting the critical node via a path with low branching factor is very successful for these cases. Of course, this strategy will produce larger routing cost.<sup>13</sup>

#### 4.2 Elmore Routing Trees

We constructed Elmore routing trees for the same sets of random inputs used in the CS-Steiner experiments. Delay simulation results, again obtained using the Two-Pole simulator, are presented in the upper parts of Table 9. For comparison, the table includes data for the minimum spanning tree and AHHK tree [1] constructions.

Our results show that even as generic net-dependent routers, the ERT methods we propose are highly effective, beyond their relative efficiency and ease of implementation. For nets with 9 sinks, the spanning tree ERT construction reduces critical sink delay versus the MST construction by 16%, 26%, and 30% in the respective IC technologies and by 67% in the MCM technology. ERT also improves upon AHHK for most of the technologies, with reductions of 0% (IC1), 4% (IC2), 6% (IC3), and 46% (MCM). These results are particularly impressive because our AHHK data follows the experimental methodology in [1], which generates output trees for 21 different values of the c parameter and then chooses the best tree found for each signal net instance.<sup>14</sup>

The Steiner ERT variant also performs well as a generic high-performance router. For 9-pin nets, SERT improves critical sink delay versus the 1-Steiner routing by 19% and 62% for the IC2 and MCM technologies, respectively. The percentage reductions in maximum delay are somewhat greater for the IC technologies, but somewhat smaller for MCM interconnects. It should be noted that for the MCM technology, the ERT and SERT constructions tend to be star-like, producing tree costs significantly higher than those of the 1-Steiner construction. In practice, when delay is not an overriding concern, the user may recapture wirelength by simulating a larger output driver resistance.

Finally, even more significant reductions in delay can be achieved when a critical sink has been identified per the original CSRT formulation. The SERT-C algorithm improves over the SERT results by an *additional* reduction in delay at the critical sink of 5%, 7% and 6% for the three IC technologies, and 8% for MCM. Identification of a critical sink has clear advantages in terms of tree cost, particularly for MCM routing: the SERT-C trees have much less cost than the SERT outputs, while still improving the delay to the critical sink.