# Detecting Bugs in Register Allocation

YUQIANG HUANG and BRUCE R. CHILDERS University of Pittsburgh and MARY LOU SOFFA University of Virginia

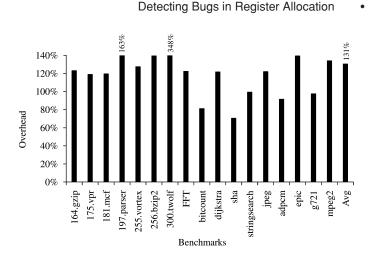

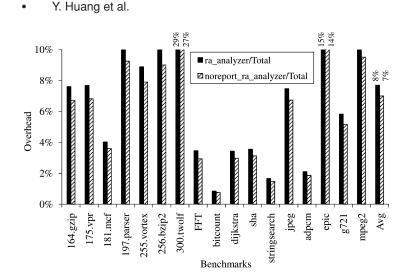

Although register allocation is critical for performance, the implementation of register allocation algorithms is difficult, due to the complexity of the algorithms and target machine architectures. It is particularly difficult to detect register allocation errors if the output code runs to completion, as bugs in the register allocator can cause the compiler to produce incorrect output code. The output code may even execute properly on some test data, but errors can remain. In this article, we propose novel data flow analyses to statically check that the value flow of the output code from the register allocator is the same as the value flow of its input code. The approach is accurate, fast, and can identify and report error locations and types. It is independent of the register allocator and uses only the input and output code of the register allocator. It can be used with different register allocators, including those that perform coalescing and rematerialization. The article describes our approach, called SARAC, and a tool that statically checks a register allocation and reports the errors and their types that it finds. The tool has an average compile-time overhead of only 8% and a modest average memory overhead of 85KB. Our techniques can be used by compiler developers during regression testing and as a command-line-enabled debugging pass for mysterious compiler behavior.

Categories and Subject Descriptors: D.3.4 [**Programming Languages**]: Processors—*Code generation, compilers, optimization*; D.2.4 [**Software Engineering**]: Software/Program Verification—*Validation*; D.2.5 [**Software Engineering**]: Testing and Debugging—*Debugging aids, diagnostics*

General Terms: Languages, Verification

Additional Key Words and Phrases: Register allocation

#### **ACM Reference Format:**

Huang, Y., Childers, B. R., and Soffa, M. L. 2010. Detecting bugs in register allocation. ACM Trans. Program. Lang. Syst. 32, 4, Article 15 (April 2010), 36 pages.

$DOI = 10.1145/1734206.1734212 \ http://doi.acm.org/10.1145/1734206.1734212$

DOI 10.1145/1734206.1734212 http://doi.acm.org/10.1145/1734206.1734212

Authors' addresses: Y. Huang (corresponding author), B. R. Childers, Department of Computer Science, University of Pittsburgh, 210 S. Bouquet St. Rm. 6404, Pittsburgh, PA 15260; email: yuqiangh@cs.pitt.edu; M. L. Soffa, Department of Computer Science, University of Virginia, PO Box 400740, 151 Engineer's Way, Olsson Hall, Rm. 206, Charlottesville, VA 22904.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org. © 2010 ACM 0164-0925/2010/04-ART15 \$10.00

## 15:2 • Y. Huang et al.

# 1. INTRODUCTION

One of the most critical compiler transformations is register allocation, as a good register allocator can make a dramatic improvement in program performance [Briggs et al. 1994; George and Appel 1996]. One study reported that careful register allocation can improve performance by one order of magnitude [Poletto and Sarkar 1999]. Thus, considerable effort has been given to developing new allocation algorithms or variants of existing ones [Bernstein et al. 1989; Bradlee et al. 1991; Briggs et al. 1992, 1994; Chaitin 1982; Chow and Hennessy 1990; George and Appel 1996; Gupta et al. 1989; Pinter 1993; Poletto and Sarkar 1999; Santhanam and Odnert 1990; Smith et al. 2004]. Given the many algorithms and the complexity of modern processor architectures, implementing register allocation is often a complex and error-prone task. It is particularly difficult to detect and locate errors in an erroneous output program of the register allocator if the program runs to completion. Various research efforts have proposed techniques to ensure the register allocation for a given program is correct [Jaramillo et al. 2002; McNerney 1991; Nandivada et al. 2007; Necula 2000; Pereira 2006]. In this article, we describe a novel technique to check the correctness of register allocation using only the input and output to the register allocator and to report the location and types of errors found. This technique is useful throughout the lifetime of a compiler; however, it is especially helpful during the development period.

Bugs can cause the compiler to fail on some input programs, but not on others. The generated code may have errors, although the compiler does not crash. Such latent bugs will not be discovered until a particular test input causes the program to fail, which could happen after the compiler is released. Assuming that a test input catches a bug, the developer may believe that the bug is in the program itself, rather than the compiler. She will spend much time and effort tracking down the bug to only discover that it is in the compiler and cannot be readily fixed. All of this leaves the developer in the unfortunate situation of having little confidence in the correctness of the generated code because bugs may remain even after testing.

The research community has recognized the difficulty of implementing compiler optimizations, including register allocation, and has proposed techniques to address the situation. Necula [2000] proposed a symbolic evaluation approach to check the allocator's output code against its input code. However, this approach reports false alarms and increases the compile-time by up to four times. Jaramillo et al. [2002] proposed a dynamic checking approach that runs the allocator's input and output code. It compares values in the input and output to check that they are the same. However, it does not guarantee the correctness of the allocator's output unless *all* paths are exercised by test inputs. Nandivada et al. [2007] proposed a framework for designing and verifying register allocation algorithms; the major aim of this framework is to prove the soundness of the type system.

In this article, we propose a new approach, called SARAC, which uses *static analyses* to check the value flow (values of variables) of the allocator's output [Dor et al. 2004; Steffen et al. 1990] with the value flow of its input. SARAC

reports the location and type of errors in the output code due to an incorrect allocation. The analyses check that the value flow of the output code matches the value flow of the input code. SARAC traverses all program paths, using data flow analysis to gather information about the output code. It then checks the value flow of variables using the gathered information. A checking step verifies that the value flow of the input code is preserved in the output code, according to data dependencies, once the allocator has assigned registers and possibly spilled registers. The information collected during the analyses is used to determine error types and locations. Other errors involving register types and instruction set architecture constraints are still possible. Identifying errors in the value flow is an important step toward a tool that fully checks and reports any bugs in the output of the register allocator.

SARAC has several desirable characteristics. It gives hints to the compiler engineer to help her diagnose and fix bugs in the allocator. It is accurate and does not rely on knowledge about the allocator implementation. It can be used with different register allocation algorithms, including those that perform coalescing and rematerialization. Such independence from the register allocator suggests that a single error analysis tool can be built and employed for different allocators (in different compilers and target machines). It uses data flow analyses and can be easily implemented. Finally, the approach has minimal performance and memory overhead, making it efficient and practical. A prototype tool, called *ra-analyzer*, that implements SARAC has an average compile-time overhead of 8% and an average memory requirement of 85KB. Both the performance and memory usage of *ra-analyzer* scale well with function body size, the number of operands, and the complexity of the Control Flow Graph (CFG). Our techniques can be used by compiler developers during regression testing and as a command-line-enabled debugging pass for mysterious compiler behavior.

This article makes several contributions, including:

- —an efficient way (SARAC) to statically check that the value flow after register allocation is the same as before register allocation and to identify and report the location and type of bugs, independently of the register allocator;

- -data flow equations that analyze value locations, stale values, and evicted values using only the input and output code of a register allocator to provide information about the type of register allocation errors;

- —techniques to support register allocators that perform coalescing, rematerialization, and register aliasing;

- —a tool (*ra-analyzer*) that implements SARAC in SUIF's back-end optimizer (MachSUIF [Smith and Holloway]) for the Intel IA-32 instruction set architecture;

- —a thorough evaluation of our techniques in *ra-analyzer* and MachSUIF, including validation, performance, and memory overhead, and scalability with program complexity.

The article is organized in the following way. The next section describes how register allocation preserves the value flow of the input code. The third section presents algorithms for gathering and using data flow information to check for

# 15:4 • Y. Huang et al.

correctness. The fourth section describes and evaluates *ra-analyzer*. The fifth section discusses related work, and the final section concludes the article.

# 2. REGISTER ALLOCATION

This section describes our register allocator model, including the input and output code to the allocator. It also gives the motivation and background for our static analyses that catch and identify bugs in the register allocation.

## 2.1 Register Allocation Model and Assumptions

We assume that a set of intermediate code instructions is input to the register allocator and the output is a set of intermediate code instructions with registers assigned to the operands. We assume the input code is semantically correct relative to the source-code. The register allocator is a global allocator that allocates registers at the function level. It has a limited number of registers and can inject spill code through copy instructions (e.g., loads, stores, and register copies). It can also perform register coalescing to remove copy instructions. Since we focus on value flow, we assume the register allocator uses correct types and obeys the constraints imposed by the machine instruction set. The calling convention that we use for the register allocator is caller-save (calleesave would work as well). We assume the register allocator does not incorporate other optimizations (e.g., instruction scheduling) [Bradlee et al. 1991; Pinter 1993], and it does not change the structure of the Control Flow Graph (CFG) or the order of instructions within basic blocks. The core function of the register allocator is to assign *locations* (registers or memory slots) to hold *values* of variables.

As typical of most back-end optimizers, we further assume that register promotion is done in a pass prior to register allocation [Cooper and Lu 1997]. Thus, aliasing, assignment through pointers, array accesses, and related phenomena have been handled and expanded into low-level code by the register promotion pass and are not the concern for our technique. For example, in the most conservative situation, a variable whose address is taken will be loaded before any use of the variable and stored after any definition of the variable. The input code to the register allocator has these load and store operations (to move values between memory and virtual registers) [Cooper and Lu 1997]. Global and array values will have similar explicit loads and stores. These loads and stores will not be removed by the register allocator. Our technique treats these load and store operations like other computational operations in the input intermediate code. We also assume that values are not mutated during store operations; however, memory addressing modes are allowed for destination operands in CISC-style instructions.

Our technique treats the register allocator as a black box; that is, we only consider the input code to the register allocator and the output. We assume that two variables cannot be assigned to the same register if one is live at a program point where the other is defined, where liveness is defined by a variable being used after the current point. It should be noted that if another definition of liveness is used, such as a variable is live if it is both defined before and used

after the current point, then our technique may report a register allocation error when in fact there is none. This situation would occur, for example, when one branch of a conditional defines a variable X and the other branch defines a variable Y. After the merge point, one path uses X and another path uses Y. Using our definition of liveness, X and Y would have to be in different registers while the alternative definition of liveness could place both X and Y in the same register.

To simplify the following discussion, we often use an instruction identification number (ID) to represent an instruction. We use RTL to give actual instructions in examples [Benitez and Davidson 1988; Davidson and Fraser 1984; GCC]. Although RTL is used for notational convenience, our techniques can work with other intermediate representations that have the characteristics described next.

The input and output to the register allocator is intermediate code (IR) instructions. The intermediate code is a set of instructions  $\{i_0, i_1, \ldots\}$ , where an instruction i = (id, op, defs, uses) is a 4-tuple and id is the instruction identification number. In the definition of instruction i, defs is the ordered set of operands defined by i and uses is the ordered set of operands used by i. The order of operands in defs and uses is the order in which they appear in instruction i. The operands in the intermediate code are the set Operands = Registers $\cup Memory\_Slots \cup Variables \cup Immediates$ . The Registers set contains all the usable hardware registers in a target machine. In RTL, r[x] refers to register x. The Memory\\_Slots set represents memory locations in the activation record, with constant stack pointer manipulations. In RTL, M[loc] refers to memory slot loc. The Variables set represents source variables, compiler temporary variables, and virtual registers. The Immediates set represents constant values.

In the definition of instruction *i*, *op* is the opcode, which is defined as:

- -copy for copies, including load, store, and copy between registers or variables. A copy instruction "propagates" a value from its use to its definition. The definition and use operand of a copy instruction belong to *Registers*, *Memory\_Slots*, or *Variables*. In RTL, a load is shown as "r[x]=M[loc]", a store is "M[loc]=r[x]", and a register-to-register copy is "r[x]=r[y]".

- *—call* for function calls; if a call has return values, they are in the *defs* set of the call instruction.

- -comp for all other types of instructions, including arithmetic/logic, jump, branch, return, and parameter passing instructions. Load and store operations in the input intermediate code are also handled as comp instructions. A parameter passing instruction initializes a parameter to the value defined in the caller. Using RTL notation, a parameter passing instruction is defined as "x=parameter", indicating that x is a parameter and defined by the caller.

An instruction of *call* or *comp* type is considered by the allocator as defining a "new" unique value for each of its definition operands. The "new" value can be represented by a unique symbolic name, say *v*. Collectively, we call these two

15:6 • Y. Huang et al.

type instructions as *noncopy* type instructions. A *copy* type instruction, on the other hand, is considered as only propagating a value without defining a "new" value.

A set of functions is also defined to manipulate the IR code. These are:

- $-isCopy(i) \rightarrow Boolean: If i = (id, copy, defs, uses), return true; otherwise, return false.$

- -isCall $(i) \rightarrow$  Boolean: If i = (id, call, defs, uses), return true; otherwise, return false.

- $-id(i) \rightarrow Integer$ : Given i = (id, op, defs, uses), return id.

- $-opcode(i) \rightarrow \{copy, call, comp\}$ : Given i = (id, op, defs, uses), return op.

- $-defs(i) \rightarrow ordered set of Operands: Given i = (id, op, defs, uses), return defs.$

- $-uses(i) \rightarrow ordered set of Operands: Given i = (id, op, defs, uses), return uses.$

- -isAlloc(Operand)  $\rightarrow$  Boolean: If  $Operand \in Registers \cup Memory\_Slots \cup Variables$ , return *true*; otherwise, return *false*.

- -isCallerSave(*Operand*)  $\rightarrow$  *Boolean*: This function returns *true* if the operand given as a parameter belongs to *Registers* and is also caller-save; otherwise, it returns *false*. A caller-save register may be overwritten during the execution of a function call and, thus, must be saved by the caller.

The functions defs() and uses() return the ordered definition/use set of an instruction. The other functions are self-explanatory.

Since the purpose of a register allocator is to allocate registers to an instruction's operands, a *one-to-one* associating relation (i.e., a *mapping*) exists for the *noncopy* type instructions between the input and output of the register allocator. Given an input instruction i of *noncopy* type and its associated output instruction i', a register allocator maintains the following property.

id(i) = id(i'), opcode(i) = opcode(i'), |defs(i)| = |defs(i')|, and |uses(i)| = |uses(i')|.

This property states that, for each *noncopy* instruction, its associated output instruction has the same identification number, the same opcode, and the same defs/uses set size. Therefore, the operands of an input *noncopy* instruction i and its transformed output i' also have a *one-to-one* operand associating relation. The details of how SARAC generates these mappings are presented in Section 3.1.

#### 2.2 Example

To discuss register allocation, we give an example in Figure 1, which counts the number of integer divisors for some number, m. We use this example throughout the article. In Figure 1, the number after each instruction is the instruction identification number (ID). The *copy* instructions are indicated, and all the instructions not indicated are of *noncopy* type.

In the example, we assume that r[1] is assigned by the allocator to hold variable m and r[2] is used to hold other variables as necessary. Figure 1(a) shows the source program, while Figure 1(b) shows the input intermediate code to the register allocator. Figure 1(c) gives the output code that should be generated by

#### (a) Source Code (b) Input to Allocator m=parameter; 0 /\*Program function - count number c=0: 1 of divisors to variable m that is d=1; 2 passed as an argument\*/ PC=((m<=0)?L3:PC+4); 3 L1:t=m%d; 4 c=0; PC=((t!=0)?L2:PC+4);5 for (d=1; d<=m; d++) { if (m%d == 0) c=c+1;6 L2:p=d; /\*coalesced in output\*/ 7 ср C++; d=p+1; 8 } 9 t=d<=m; PC=((t==1)?L1:PC+4); 10 L3: (c) Correct Output from Allocator (d) Incorrect Output from Allocator M[m]=parameter; 0 Ω M[m]=parameter; r[1]=M[m]; 20 cp ~[1]\_M[m] • 20 cm

|    | op                                                                        |

|----|---------------------------------------------------------------------------|

| 1  |                                                                           |

| 21 | ср                                                                        |

| 2  |                                                                           |

| 22 | ср                                                                        |

| 3  |                                                                           |

| 23 | ср                                                                        |

| 4  |                                                                           |

| 5  |                                                                           |

| 24 | ср                                                                        |

| 6  |                                                                           |

| 25 | ср                                                                        |

| 26 | ср                                                                        |

| 8  | -                                                                         |

| 27 | ср                                                                        |

| 9  | -                                                                         |

| 10 |                                                                           |

|    |                                                                           |

|    | 1<br>21<br>22<br>3<br>23<br>4<br>5<br>24<br>6<br>25<br>26<br>8<br>27<br>9 |

Fig. 1. Example: source, input to register allocator, correct and incorrect output where the number after each instruction is the instruction ID, and *cp* indicates that an instruction is a *copy*.

the register allocator, assuming it is correctly implemented. Finally, Figure 1(d) gives output code that may be generated by a register allocator with a bug(s).

In this code, there are a few important items to notice. In Figure 1(b), instruction "p=d" is removed from the correct/incorrect output code due to coalescing. A number of *copy* instructions are also injected into the correct/incorrect output. Each *noncopy* instruction in the input stays in the correct/incorrect output code. Figure 1(d) shows the effect of a bug in the register allocator. In this code, two incorrect code edits were made by the register allocator. The first incorrect edit occurs to instruction 4, where the wrong register has been assigned to the second source operand. The other incorrect edit happens at instruction 25, where the wrong memory location is used for the spill. The example also shows the instructions where these errors are manifested. The instruction where an error is manifested is not necessarily the instruction where the incorrect edit is made. For example, the incorrect edit at instruction 25 is manifested as errors 2 and 3 at instructions 6 and 8.

15:8 • Y. Huang et al.

#### 2.3 Value Flow Preservation by Register Allocation

A correct allocation of registers must preserve the input code's semantics, particularly the data dependencies and the values of these dependencies, or the *value flow* [Dor et al. 2004; Steffen et al. 1990]. The *copy* type instructions only "propagate" a value, and the *noncopy* type instructions define a "new" unique value for each definition. Every input *noncopy* instruction will be mapped to an instruction in the output code. Instructions of *copy* type can be injected or removed by the register allocator. Intuitively, an allocation has correct value flow if the "values" defined/used by every *noncopy* instruction in the output are the same as the "values" defined/used by the mapped input instruction.

To discuss how the allocator may maintain or violate value flow, we use two data-dependency-related definitions. In the definitions, we use the notation "*i*.*x*=" to indicate the definition of operand *x* in instruction *i* and "*i*. = *x*" to indicate the use of operand *x* in *i*. We also use the notation "*i*.*x*<sub>n</sub> = *x*<sub>m</sub>" to indicate a *copy* type instruction *i* that uses  $x_m$  and defines  $x_n$ .

*Definition* 1. A *du-pair*  $(i_0.x =, i_1. = x)$  in a program function is a 2-tuple, such that:

- (i) isAlloc(x) is true,

- (ii) there is a definition of x at instruction  $i_0$ ,

- (iii) there is a use of x at instruction  $i_1$ , and

- (iv) x defined at  $i_0$  reaches  $i_1$ ; that is, there is a path from  $i_0$  to  $i_1$  such that there is no other definition of x along the path.

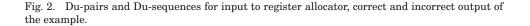

The preceding definition describes a data dependency (e.g., reaching definitions) with our definition-use terms. Figure 2 displays the complete list of du-pairs for the example function in Figure 1. For instance, in Figure 2(a), the du-pair (2.d=,4.=d) indicates that d is defined at instruction 2 and then used at instruction 4.

Definition 2. Given the du-pairs (Du-pairs) for a function, a *du-sequence*  $(i_0.x_0 =, i_1.x_1 = x_0, \ldots, i_n.x_n = x_{n-1}, i_{n+1} = x_n)$  is a (n + 2)-tuple, where  $n \ge 0$ , such that:

- (i)  $\neg$ isCopy( $i_0$ ) is true,

- (ii)  $\neg$ isCopy( $i_{n+1}$ ) is true,

- (iii) isCopy( $i_k$ ) is true, where  $n \ge k \ge 1$ , and

- (iv)  $(i_k.x_k =, i_{k+1}. = x_k) \in \text{Du-pairs}$ , where  $n \ge k \ge 0$ .

Definition 2 specifies a du-sequence as a sequence of instructions where the start and end instructions are of *noncopy* type and the instructions in between are of *copy* type. A unique symbolic value, say v, is defined by an instruction of *noncopy* type. It is then propagated by a series of *copy* type instructions and finally used by a *noncopy* instruction. A "new" unique symbolic value may also be defined and used without being propagated by copy instructions. We use **start**(du-sequence) to denote the beginning of a du-sequence (" $i_{0.x_0}$ =") and **end**(du-sequence) to denote the end (" $i_{n+1}$ . =  $x_n$ "). Figure 2 displays the

ACM Transactions on Programming Languages and Systems, Vol. 32, No. 4, Article 15, Pub. date: April 2010.

#### (a) Du-pairs of Input

#### (b) Du-sequences of Input

- {(0.m=, 3.=m), (0.m=,4.=m), (2.d=, 4.=d), (8.d=,4.=d), (4.t=,5.=t), (1.c=,6.=c), (6.c=,6.=c), (2.d=,7.=d), (8.d=, 7.=d), (7.p=,8.=p), (8.d=,9.=d), (0.m=,9.=m), (9.t=,10.=t)}

- $\{(0, m=, 3, =m),$ (0.m=,4.=m), (2.d=, 4.=d), (8.d=, 4.=d), (4.t=, 5.=t), (1.c=,6.=c), (6.c=,6.=c), (2.d=,7.p=d,8.=p), (8.d=,7.p=d,8.=p), (8.d=,9.=d), (0.m=, 9.=m), (9.t=,10.=t)}

#### (c) Du-pairs of Correct Ouput

$\{ (0.M[m] = , 20.=M[m]) , \}$ (1.r[2]=,21.=r[2]), (2.r[2]=,22.=r[2]), (20.r[1]=,3.=r[1]), (22.M[d]=,23.=M[d]), (27.M[d] = , 23.=M[d]), (20.r[1]=, 4.=r[1]),(23.r[2]=, 4.=r[2]), (4.r[2]=,5.=r[2]), (21.M[c]=, 24.=M[c]),(25.M[c]=,24.=M[c]), (24.r[2]=, 6.=r[2]),(6.r[2]=,25.=r[2]), (22.M[d]=,26.=M[d]), (27.M[d] = , 26.=M[d]), (26.r[2]=,8.=r[2]), (8.r[2]=,27.=r[2]), (8.r[2]=,9.=r[2]), (20.r[1]=, 9.=r[1]),(9.r[2]=,10.=r[2])}

(e) Du-pairs of Incorrect Ouput

(9.r[2] = , 10. = r[2])

#### (d) Du-sequences of Correct Output

```

\{ (0.M[m] =, 20.r[1] = M[m], 3.=r[1] \}, \}

(0.M[m] =, 20.r[1] = M[m], 4.=r[1]),

(2.r[2]=, 22.M[d]=r[2], 23.r[2]=M[d], 4.=r[2]),

(8.r[2]=,27.M[d]=r[2],23.r[2]=M[d],4.=r[2]),

(4.r[2]=,5.=r[2]),

(1.r[2]=,21.M[c]=r[2],24.r[2]=M[c],6.=r[2]),

(6.r[2]=,25.M[c]=r[2],24.r[2]=M[c],6.=r[2]),

(2.r[2]=,22.M[d]=r[2],26.r[2]=M[d],8.=r[2]),

(8.r[2]=,27.M[d]=r[2],26.r[2]=M[d],8.=r[2]),

(8.r[2]=,9.=r[2]),

(0.M[m] =, 20.r[1] = M[m], 9.=r[1]),

(9.r[2]=,10.=r[2])}

```

#### (f) Du-sequences of Incorrect Output

| <pre>{(0.M[m]=, 20.=M[m]),<br/>(1.r[2]=, 21.=r[2]),<br/>(2.r[2]=, 22.=r[2]),<br/>(20.r[1]=, 3.=r[1]),<br/>(22.M[d]=, 23.=M[d]),<br/>(27.M[d]=, 23.=M[d]),<br/>(20.r[1]=, 4.=r[1]),<br/>(4.r[2]=, 5.=r[2]),<br/>(21.M[c]=, 24.=M[c]),<br/>(24.r[2]=, 6.=r[2]),<br/>(6.r[2]=, 25.=r[2]),<br/>(22.M[d]=, 26.=M[d]),<br/>(25.M[d]=, 26.=M[d]),<br/>(27.M[d]=, 26.=M[d]),<br/>(26.r[2]=, 8.=r[2]),</pre> | <pre>{(0.M[m]=,20.r[1]=M[m],3.=r[1]),<br/>(0.M[m]=,20.r[1]=M[m],4.=r[1]),<br/>(4.r[2]=,5.=r[2]),<br/>(1.r[2]=,21.M[c]=r[2],24.r[2]=M[c],6.=r[2]),<br/>(2.r[2]=,22.M[d]=r[2],26.r[2]=M[d],8.=r[2]),<br/>(6.r[2]=,25.M[d]=r[2],26.r[2]=M[d],8.=r[2]),<br/>(8.r[2]=,27.M[d]=r[2],26.r[2]=M[d],8.=r[2]),<br/>(8.r[2]=,9.=r[2]),<br/>(0.M[m]=,20.r[1]=M[m],9.=r[1]),<br/>(9.r[2]=,10.=r[2])}</pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>(26.r[2]=,8.=r[2]),<br/>(8.r[2]=,27.=r[2]),<br/>(8.r[2]=,9.=r[2]),<br/>(20.r[1]=,9.=r[1]),</pre>                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                               |

15:10 • Y. Huang et al.

complete list of du-sequences for the example function in Figure 1. For example, in Figure 2(b), the du-sequence (2.d=,7.p=d,8.=p) states that a "new" unique value is defined by *noncopy* instruction 2 (i.e., "d=1"), propagated by *copy* instruction 7 (i.e., "p=d"), and finally used by *noncopy* instruction 8 (i.e., "d=p+1").

When the allocator correctly maintains the data dependency of the input code, each input du-sequence has one or more associated output dusequences. The start of the input du-sequence associates to the start of the output du-sequence; the end of the input du-sequence associates to the end of the output du-sequence. For instance, consider Figures 2(b) and 2(d). The input code to the register allocator has the du-sequence (2.d=,7.p=d,8.=p) and the correct output code has the du-sequence (2.r[2]=,22.M[d]=r[2],26.r[2]=M[d],8.=r[2]). These du-sequences are associated in that "2.d=" associates to "2.r[2]=" and "8.p=" associates to "8.=r[2]". In other words, the input definition operand d (of instruction 2) is mapped to the output definition r[2] and the input use p (of instruction 8) is mapped to the output use r[2].

Multiple du-sequences may connect to each other by sharing the same start or ending instruction. That is, a start definition may propagate along multiple du-sequences to reach different ending uses; likewise, an ending use may be reachable along multiple du-sequences from different start definitions. For instance, Figure 2(b) has two input du-sequences (1.c=,6.=c) and (6.c=,6.=c)that have the same ending instruction. During register allocation, the allocator must make the two defined values of c available in (at least) one common register (memory slot) before the merge point. This action ensures that both definitions reach the common use. Figure 2(d) shows the two correct output du-sequences(1.r[2]=,21.M[c]=r[2],24.r[2]=M[c],6.=r[2]) and (6.r[2]=,25.M[c]=r[2],24.r[2]=M[c],6.=r[2]), where both defined values for c are available in M[c] before the merge point. From the perspective of the register allocator, multiple definitions that reach the same use may be considered as different versions of a value. We next define a *du-sequence-web* to consist of connected sequences and a helper definition called *connected*.

Definition 3. Given two du-sequences s and s', **singly-connected**(s, s') is true if  $s \neq s'$  and  $start(s) = start(s') \lor end(s) = end(s')$ . The relationship "connected" is the transitive closure of singly-connected sequences; that is, if **singly-connected**( $s_0$ ,  $s_1$ ) is true and **singly-connected**( $s_1$ ,  $s_2$ ) is true, then **connected**( $s_0$ ,  $s_2$ ) is true.

Definition 4. A du-sequence-web is a set W of du-sequences,  $\{s_1, \ldots, s_n\}$ , such that:

(i)  $\forall s_i \in W, \forall s_j \in W, s_i \neq s_j$ , then connected(s<sub>i</sub>, s<sub>j</sub>) is true, and

(ii)  $\forall s_i \in W, \forall s \notin W$ , then connected $(s_i, s)$  is false.

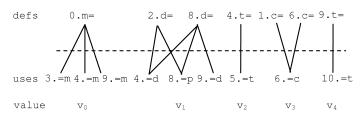

Figure 3 shows the various ways that du-sequences can be connected, using shared definitions or uses for the input function in Figure 1. The graphs imposed by the connections of du-sequences are also shown. For instance, in Figure 3(a),  $\{(1.c=,6.=c), (6.c=,6.=c)\}$  represents the du-sequence-web that involves

#### (a) Du-sequence-webs of Input

```

{ { (0.m=, 3.=m), (0.m=, 4.=m), (0.m=, 9.=m) },

{ (2.d=, 4.=d), (8.d=, 4.=d), (2.d=, 7.p=d, 8.=p),

(8.d=, 7.p=d, 8.=p), (8.d=, 9.=d) },

{ (4.t=, 5.=t) }

{ (1.c=, 6.=c), (6.c=, 6.=c) },

{ (9.t=, 10.=t) } }

```

#### (b) Visual Effect for Du-sequence-webs of Input

Fig. 3. Du-sequence-webs for input to register allocator of the example.

variable c (with a given value  $v_3$ ). Also, {(4.t=,5.=t)} and {(9.t=,10.=t)} have only one du-sequence.

# 2.4 Sources of Errors

A bug in the register allocator that causes the output program (but not the compiler) to crash or produce a wrong result is manifested through incorrect code edits that can be made by the allocator. For the register allocator model defined in Section 2.1, the possible incorrect edits are:

- (1) *incorrect register (or memory slot) assignment*: the wrong register (or memory slot) is used for an operand in a *noncopy* instruction;

- (2) *incorrect instruction of copy type*: a value is spilled or copied incorrectly by using the wrong register or memory slot in a *copy* instruction;

- (3) missing instruction of copy type: a value is not spilled or copied when needed.

These edits can violate the value flow of the input code by causing the dusequences from the input function to not associate to the output du-sequences from the transformed function or vice versa. The incorrect edits can allow the program to run to completion but produce a wrong result. If there are no expected correct program results for comparison, the impact of the incorrect edits on the program's value flow will not be detected. Even if it is noticed that the program being compiled produces a wrong result, there is no obvious starting point to isolate where the incorrect edits occurred. Thus, these incorrect edits can pose a challenge to the compiler engineer.

Note the distinction between an "incorrect edit" and an "error": An incorrect edit is the cause of an error. The incorrect edit defines where the error was introduced, but it is not necessarily the place where the error is manifested. An incorrect edit may not manifest itself as an error until a value affected by the edit is used, which is the instruction at the end of a du-sequence. For

## 15:12 • Y. Huang et al.

instance, in Figure 1(d), the incorrect edit at instruction 25 is not manifested until instructions 6 and 8.

The incorrect edits can lead to three error types: *wrong operand error, stale value error*, or *eviction error*. Although these errors all involve value flow violations, we distinguish between them to report causal information about an error. The three errors are defined as follows:

- —A *wrong operand error* occurs when a register or memory slot is referenced that does not hold the needed value. The value is actually held in some other location(s). This error is usually caused by an incorrect register assignment.

- —A *stale value error* happens when a register or memory location is referenced that holds an old version of the needed value. A wrong or missing spill is a common cause.

- —An *eviction error* occurs when a value is referenced that is not held in any location. This error is usually caused by a wrong spill.

For each type of error, there is an instance in the incorrect output of Figure 1(d). First, there is a wrong operand error at instruction 4. This error is caused by an incorrect register assignment at instruction 4, where d is assigned to r[1] instead of r[2]. Thus, there is no definition of d that is used at instruction 4 and a wrong value (of m) is used instead. As shown in Figure 2, the input du-sequences (2.d=,4.=d) and (8.d=,4.=d) do not have the associated output du-sequences. The "new" defined value of d is available in r[2] at instruction 4, but it is not correctly used. Second, there is a stale value error at instruction 6. This error is introduced by the wrong spill at instruction 25, where r [2] is spilled to M[d], rather than to M[c]. Thus, there is no du-sequence for c along the loop's back edge that reaches the use at instruction 6. A stale value for c is used instead. That is, the input du-sequence (6.c=,6.=c) does not have an associated output du-sequence. At instruction 6, only the stale value of c (previously defined at instruction 1) is available in r[2]. Finally, there is an eviction error at instruction 8. This error is also caused by the wrong spill at instruction 25. During the execution of the incorrect code, right before instruction 25, M[d] is the only location that holds the value of d. At instruction 25, the value of d is evicted from M[d] due to the wrong spill. Therefore, no location holds d after instruction 25 and the value of d cannot be loaded into r [2] at instruction 26. Finally, an eviction error is caught at instruction 8, where the value of d is referenced. As shown in Figure 2(f), the output du-sequence (6.r[2]=,25.M[d]=r[2],26.r[2]=M[d],8.=r[2]) does not have an associated input du-sequence.

# 3. ERROR ANALYSIS FOR REGISTER ALLOCATION

To find register allocation errors, we developed a Static and Automatic Register Allocation Checking technique, called SARAC. Intuitively, the technique checks if the du-sequences in the register allocator's input function match the du-sequences in the allocator's output. However, to report error type rather than just detect errors, the approach first constructs du-sequences for the allocator's input function. A unique value, named v, is given to each input

#### Detecting Bugs in Register Allocation • 15:13

1: SARAC(input,output) {

2: //Step 1: mapping generation

3: Map mappings = mapGen(input,output);

4: //Step 2: data flow analysis

5: Dataflow sets = defAnalysis(output,mappings);

6: //Step 3: check the allocation

7: errAnalysis(output,mappings,sets);

8: }

#### Fig. 4. Pseudocode for SARAC steps.

du-sequence-web. The unique value v is then mapped to the output definition and use. At the output definition point, v is considered as the new defined value; at the use point, v is the value that is expected to be used. Then, a data flow analysis on the output function propagates v from the definition point along *copy* instructions to the use of v by a *noncopy* instruction. Finally, a check is done to verify that the value flowing into the use is actually the expected one. The data flow analysis on the output function implicitly constructs the output du-sequences, and it also collects information about error types.

SARAC has three steps as shown in Figure 4. First, mapping information is generated by a step called **mapGen** using input and output functions to the allocator. Then, iterative forward data flow analysis, called **defAnalysis**, is performed on the output function using the mapping information. This analysis collects three types of data flow sets that are used to check the correctness of the output and to report error locations and types. Finally, a linear scan, called **errAnalysis**, is done to find and report value flow violations in the output function with the collected data flow sets.

# 3.1 Mapping Generation (mapGen)

SARAC needs to collect what values (represented by a name, v) are defined/used in the input code to the register allocator and what values are actually defined/used in the output code. First, the input du-sequences are constructed and each du-sequence-web is assigned a unique value, named v. Associations (i.e., mappings) between input and output *noncopy* instruction definitions/uses are generated. An associated definition in the output code for a *noncopy* instruction is considered as defining v. An associated use in the output code for a *noncopy* instruction is expected to use v.

To express the mapping information, we use the following grammar.

```

\begin{array}{l} <\!\!mapping\!\!>:=id:\!\!posn:<\!\!dou\!\!>:<\!\!out\!\!>\mapsto<\!\!in\!\!>\\ <\!\!dou\!\!>:=DEF|USE\\ <\!\!out\!\!>:=location \mid \# \, constant\\ <\!\!in\!\!>:=value \mid \# \, constant\\ \\ where\\ id - the \, identification \, number \, for \, noncopy \, instructions\\ posn - operand \, number \, in \, an \, instruction's \, definition \, or \, use \, set\\ location - a \, register \, or \, memory \, slot\\ value - a \, given \, unique \, name \, representing \, value(s) \end{array}

```

For example, in Figure 1, the instruction "r[2]=0" in the output code associates to "c=0 in the input code. Therefore, the mapping for the definition operand

#### 15:14 • Y. Huang et al.

r [2] at instruction 1 is  $1:1:DEF:r[2] \rightarrow v_3$ , where r [2] is a *location* and  $v_3$  is a *value*, which is the unique name given to the du-sequence-web involving "1.c=" (see Figure 3). A mapping can also associate immediate constants in the output and input. For instance, there is a mapping  $1:1:USE:\# 0 \rightarrow \# 0$  that gives the association between the constants at output instruction "r[2]=0" and input instruction "c=0". A mapping is generated for all *noncopy* instructions in the output. No mapping is generated for a *copy* instruction.

As shown in Figure 5, mapGen() generates mappings between the allocator's input and output code, where the allocator is viewed as a black box. First, the input function is processed to traverse each du-sequence-web. This traversal replaces each definition/use in the start/end instructions with a given unique name, v. Then, for each output *noncopy* instruction, its mapped input instruction is retrieved. The retrieval is based on the input instruction's identification number, which is the same as the mapped output instruction. We note that the input and output code is not necessarily in a specific order to retrieve the mapped instructions. Finally, each definition/use in every output *noncopy* instruction is mapped to its associated definition/use in the input, which has been replaced with a unique name v.

The mappings are used by both defAnalysis and errAnalysis. defAnalysis uses the mappings to track values and their name associations. errAnalysis uses the mappings to detect errors at uses and to report error causes. Although a complete mapping has an instruction ID, operand number, and an identifier to distinguish between definitions and uses, we use an abbreviation (i.e., *location* $\mapsto$ *value*) to simplify the discussion of the data flow equations for SARAC. For example, the output code in Figure 1 has an instruction "r[2]=0" that is associated to the input instruction "c=0". We abbreviate the complete mappings as simply r[2]  $\mapsto$  c and 0  $\mapsto$  0 in this case.

# 3.2 Data Flow Analysis (defAnalysis)

To check if the register allocation is correct and to determine error locations and types, defAnalysis gathers information about the behavior of the register allocator using the output code and the mappings. defAnalysis gathers three types of information at all points in the program: (1) the values that are currently held in all locations (registers and memory), (2) the stale values, and (3) the evicted values. Note if we only wanted to know whether a register allocation is correct, we would not need the eviction information. Because we also want to report the error types to help isolate a bug, all three types of information are gathered. We develop a data flow algorithm to gather the information by using the mappings to get the values in the input code associated with locations in the output code. For example, when output instruction 2, "r[2]=1", in Figure 1 is processed, the mapped destination operand v<sub>1</sub> (that replaces d) is retrieved from the mappings. This mapping is used to derive three pieces of information. First, the current value of v<sub>1</sub> is defined in r[2]. Second, the value v<sub>3</sub> in r[2] is evicted. Finally, any previous value of v<sub>1</sub> in other locations is stale.

This information is collected in three data flow sets: the Location set (L), the Stale set (ST) and the Eviction set (E). Each set consists of triples (l, v, c), where

```

1: mapGen(input,output) {

2:

replaceValue(input);

3:

Map mappings:=\emptyset;

4:

foreach (Instruction i'∈output) {

5:

if (¬isCopy(i')=true) {

6:

Integer id := id(i');

Instruction i := getInstr(input,id);

7:

8:

for (k=1; k≤|defs(i)|; k++) {

9:

Opnd l := getSetElemt(defs(i'),k);

10:

Opnd v := getSetElemt(defs(i),k);

11:

mappings:=mappingsU"id:k:DEF: l→v";

12:

}

13:

for (k=1; k≤|uses(i)|; k++) {

14:

Opnd l := getSetElemt(uses(i'),k);

15:

Opnd v := getSetElemt(uses(i),k);

16:

mappings:=mappings∪"id:k:USE: l→v";

17:

}

18:

}

19:

}

20:

return mappings;

21: }

22: replaceValue(input) {

23:

DuSeqS duseqs := Du-Sequences(input);

foreach (DuSeq duseq∈duseqs) {

2.4:

25:

Def def := start(duseq);

26:

if (def is visted)

27:

continue;

28:

//provide a unique name for a web

29:

Variable v := genName();

30:

traverseWeb(input,def,v,duseqs);

31:

}

32: }

//replace the start/end opnds in a du-sequence web by v

33: traverseWeb(input,def,v,duseqs) {

34:

if (def is visited) then return;

35:

Mark def as visited;

36:

Integer id := getId(def); //def="id.x="

Opnd x := getOpnd(def);

37:

38:

Instruction i := getInstr(input,id);

39:

replaceDefValue(i,x,v); //replace x with v at i

//follow ending uses for du-sequences starting with def

40:

foreach (DuSeg duseg∈dusegs and start(duseg)=def) {

41:

42:

Use use := end(duseq);

43:

if (use is visited) then continue;

44:

Mark use as visited;

45:

Integer id := getId(use); //use="id.=x"

46:

Opnd x := getOpnd(use);

47:

Instruction i := getInstr(input,id);

48:

replaceUseValue(i,x,v); //replace x with v at i

49:

//follow starting defs for du-sequences ending with use

50:

foreach (DuSeq duseq∈duseqs and end(duseq)=use) {

51:

Def def := start(duseq);

traverseWeb(input,def,v,duseqs);

52:

53: }}

```

Fig. 5. Pseudocode for mapping generation.

15:16 • Y. Huang et al.

l is a location (register or memory) from the output code, v is a value (name) from the input code, and c is a vector consisting of instructions. The instructions in c indicate how the relationship between l and v is built and have different semantics in three different sets; this information will help debugging when an error is exposed. The semantics of (l, v, c) for L, ST and E are defined as follows.

- The Location set L records the fact that location l holds v. The vector c records a du-sequence for v; that is, it incrementally records the intervening copy operations in a du-sequence such that when the data flow equations reach a fixed point, there will be sequential descriptions for every du-sequence in the program.

- The Stale set ST records that location l holds a stale v. When the data flow equations reach a fixed point, the vector c incrementally records the non-copy instruction that makes v become stale and the copy instructions that propagate stale v to location l.

- —The Eviction set E records that v has been evicted from location l. For E, c is always a single-instruction vector, and that instruction kills v from l.

In a triple (l, v, c), we use the notation \* to indicate a *don't care* value; that is, any value in a field in the triple matches with a \*.

3.2.1 Data Flow Equations. A forward data flow analysis is used to compute L, ST, and E. We assume a control flow graph representation for the output code of the register allocator.

Our data flow equations extend the traditional dataset operations due to the third field of the triple, which is a vector. We redefine " $\cap$ " and "-" to handle the vector field *c*.

$$P \cap Q = \{(l,v,c) \mid ((l,v,c) \in P \land (l,v,*) \in Q) \lor ((l,v,*) \in P \land (l,v,c) \in Q)\}$$

(1)

$$P - Q = \{(l, v, c) \mid (l, v, c) \in P \land (l, v, *) \notin Q\}$$

(2)

These two operators are similar to the normal set operators, but the operations are based only on the first two fields in the triple. The third field c is handled in a special way. We also use the traditional " $\cup$ " definition.

$$P \cup Q = \{(l, v, c) \mid (l, v, c) \in P \lor (l, v, c) \in Q\}$$

(3)

Computing the Location Set (L).

$$L_gen[i] = \{(l, v, \langle i \rangle) \mid \neg isCopy(i) \land l \in defs(i) \land l \mapsto v\}$$

(4)

*L\_gen[i]* is computed when the processed instruction *i* is of *noncopy* type. For each such instruction, each of its definitions is considered as defining a new value (i.e., the mapped *v*). Therefore, a triple  $(l, v, \langle i \rangle)$  is generated for each definition operand *l*. For instance, when instruction 6, "r[2]=r[2]+1, in Figure 1(d) is processed, a triple (r[2], v<sub>3</sub>, <6>) is generated in *L\_gen[i]* due to r[2]  $\mapsto$  v<sub>3</sub>.

L.kill[i] considers that the execution of *i* destroys the value in each of its definition operands and that crossing a function might destroy the value in

ACM Transactions on Programming Languages and Systems, Vol. 32, No. 4, Article 15, Pub. date: April 2010.

each caller-save register.

$$L\_kill[i] = \{ (l, *, *) | l \in defs(i) \lor (isCall(i) \land isCallerSave(l)) \}$$

$$(5)$$

Without knowledge about the usage of caller-save registers from the callee function, the global register allocator assumes that every caller-save register would be overwritten within the callee function. Therefore, the same assumption applies when checking the register allocation.

For value propagation of *copy* instructions, an operator  $\oplus$  is defined as follows.

$$P \oplus i = \left\{ (l_d, v, \langle i_1, \dots, i_k, i \rangle) \middle| \begin{array}{c} \exists (l_s, v, \langle i_1, \dots, i_k \rangle) \in P \land \\ isCopy(i) \land \{l_d\} = defs(i) \land \{l_s\} = uses(i) \end{array} \right\}$$

(6)

The operator states that, if the source of a *copy* instruction holds a value that is indicated by  $(l_s, v, \langle i_1, \ldots, i_k \rangle) \in P$ , the same value will be propagated to the definition operand of that *copy* instruction. The vector  $\langle i_1, \ldots, i_k, i \rangle$  is also modified to record the chain of value definition and propagation, which will result in a du-sequence.

Given the Gen, Kill and IN sets, *L\_out[i]* is computed as follows.

$$L\_out[i] = L\_gen[i] \cup (L\_in[i] \oplus i) \cup (L\_in[i] - L\_kill[i])$$

$$\tag{7}$$

The value propagation of *copy* type instructions is conducted when computing  $L_out[i]$ . For example, when instruction 21, "M[c]=r[2]", in Figure 1(d) is processed, it is known that  $(r[2], v_3, <1>)$  is in  $L_in[21]$ . Therefore, a triple  $(M[c], v_3, <1, 21>)$  is generated to indicate the fact that  $v_3$  is defined in r[2] at instruction 1 and is copied to M[c] at instruction 21. Finally,  $L_out[i]$  records all the locations (registers and memory) that hold a value up to instruction *i*, regardless of whether the value is current or stale.

Computing the Stale Set (ST).

$$ST\_gen[i] = L\_gen[i] \tag{8}$$

$ST\_gen[i]$  is the same as  $L\_gen[i]$ . For instructions of *noncopy* type, every definition operand l is considered as having a new value (i.e., v) defined. Therefore, the new definition of v makes the previous v held in any other location stale. All the locations (other than l) that hold a previous v will be discovered from  $L\_in[i]$ .

*ST\_kill[i]* is computed identically as *L\_kill[i]*.

$$ST\_kill[i] = L\_kill[i] \tag{9}$$

The operator • for finding stale values is defined as follows.

$$P \bullet Q = \{(l', v, \langle i \rangle) | (l, v, \langle i \rangle) \in P \land (l', v, *) \in Q \land l \neq l'.\}$$

$$(10)$$

For instance, when instruction 6, "r[2]=r[2]+1", in Figure 1(d) is processed, the definition operand r[2] is mapped to  $v_3$  and (M[c],  $v_3$ , <1, 21>) is retrieved from *L\_in[6]*. Due to the new definition of  $v_3$  into r[2], the previous  $v_3$  in M[c] is now stale. Therefore, a triple(M[c],  $v_3$ , <6>) is generated.

*ST\_out[i]* is computed as follows.

$$ST\_out[i] = (ST\_gen[i] \bullet L\_in[i]) \cup (ST\_in[i] \oplus i) \cup (ST\_in[i] - ST\_kill[i])$$

(11)

15:18 • Y. Huang et al.

In the equation, the operator  $\oplus$  is applied to propagate the stale value. For a *copy* type instruction, if its source operand holds a stale value, then the value propagated into its definition is also stale. Whether the value in the source of a *copy* is stale or not is discovered from  $ST_{in}[i]$ . For example, when instruction 24, "r[2] = M[c]", in Figure 1(d) is processed, it is known that (M[c],  $v_3$ , <6>) is in  $ST_{in}[24]$  along the loop's back edge. Therefore, a triple (r[2],  $v_3$ , <6, 24>) is generated to record the fact that  $v_3$  in M[c] is stale due to the new definition of  $v_3$  at instruction 6 and is copied to r[2] at instruction 24 along the loop's back edge.

Computing the Eviction Set (E).

The equations for computing *E* are closely related to those for *L*.

$$E_{gen}[i] = \{(l, *, \langle i \rangle) | (l, *, *) \in L_{kill}[i]\}$$

(12)

$$E_kill[i] = L_gen[i] \tag{13}$$

*E\_gen[i]* records that any value saved in l will be evicted because of i. What value actually evicted will be discovered from  $L_in[i]$ .  $E_kill[i]$  indicates that a new value is defined into the definition(s) of a *noncopy* instruction i.

To discover the actually evicted value, the operator  $\Diamond$  is defined as follows.

$$P \diamond Q = \{(l, v, \langle i \rangle) | (l, *, \langle i \rangle) \in P \land (l, v, *) \in Q\}$$

$$(14)$$

*E\_out[i]* is computed as follows.

$E\_out[i] = ((E\_gen[i] \diamond L\_in[i]) \cup E\_in[i]) - (E\_kill[i] \cup (L\_in[i] \oplus i))$ (15)

The operator  $\oplus$  is used here to discover the value propagated into the destination of a *copy* instruction *i*, which essentially kills a triple in *E*. Please also note that a triple in *E*\_gen[*i*] can also be in *E*\_kill[*i*]. For instance, *E*\_gen[*i*] and *E*\_kill[*i*] may both have  $(l, v, \langle i \rangle)$ . This situation happens when a previous instruction defines v in l and the following instruction *i* redefines v in *l*. In this case,  $(l, v, \langle i \rangle)$  should not be in *E*\_out[*i*] because v is still in *l* after executing instruction *i*. The association order in the equation enforces this semantics.

3.2.2 The defAnalysis Algorithm. Given the mapping information, def-Analysis analyzes the output code of the register allocator and returns the data flow sets L, ST, and E. The algorithm is shown in Figure 6. It implements a forward iterative data flow analysis.

In the algorithm, the function **setInitialization**() is called to initialize the IN sets of L, ST, and E for each basic block. As in standard iterative data flow analysis, the initialization value for IN (i.e., empty,  $\phi$ , or universal, U) depends on which set operation (e.g., intersection or union) is applied at merge points in the control flow graph and whether a basic block is a CFG entry node. Given the initial IN sets, setInitialization(), calls computeLocalFlow() to compute the OUT sets for each basic block. The function **computeLocalFlow**() implements the data flow equations from Section 3.2.1. The data flow equations are executed in the order that they were discussed in Section 3.2.1.

In the iterative steps, **mergeFlow()** is called to execute set operations on L, ST, and E at a merge point. The code on lines 29-31 performs the set operations

```

1: defAnalysis(output, mappings) {

2:

Dataflow sets;

3:

foreach (Block B∈output)

4:

setInitialization(B,mappings,sets.L,sets.ST,sets.E);

5:

change := true;

6:

while (change) {

7:

change := false;

foreach (Block B∈output and B≠Binitial) {

8:

9:

oldsets := sets_in[B];

10:

mergeFlow(output, B, sets.L, sets.ST, sets.E);

11:

if (oldsets ≠ sets_in[B]) {

12:

change := true;

13:

computeLocalFlow(B, mappings, sets.L, sets.ST, sets.E);

14:

}

15:

}

16:

}

17:

return sets;

18: }

19: setInitialization(B, mappings, L, ST, E) {

20:

if (B = B_{initial}) {

L_{in}[B] := \emptyset; ST_{in}[B] := \emptyset; E_{in}[B] := \emptyset;

21:

22:

} else {

23:

L_{in}[B] := U; ST_{in}[B] := \emptyset; E_{in}[B] := \emptyset;

24:

ł

25:

computeLocalFlow(B, mappings, L, ST, E);

26: }

27: mergeFlow(output, B, L, ST, E) {

28:

//P \in Predecessors(B)

29:

L_in[B] := \cap L_out[P];

30:

ST_in[B] := \bigcup ST_out[P];

31:

E_{in}[B] := \bigcup E_{out}[P];

32:

//the following computes and uses L_inconsistent

33:

L_union := \cup L_out[P];

34:

L_inconsistent := { (l, v, \langle B \rangle) | \forall (l, v, *) \in (L_union-L_in[B]) };

35:

E_{in}[B] := E_{in}[B] \cup L_{inconsistent};

36:

ST_in[B] := ST_in[B]-L_inconsistent;

37: }

```

Fig. 6. Pseudocode for data flow analysis algorithm.

on L, ST, and E. First, at the merge point to block B,  $L_{in}$  is computed by  $\cap$ on  $L_{outs}$  of all predecessors to B. A correct register allocation has the same value in a common location along any preceding path for a later common use. Therefore,  $\cap$  removes any "inconsistent triples" where the same location holds different values in different paths. For example, a triple from one path might show that r[1] holds x, but the other path indicates that r[1] does not hold x. Second,  $ST_{in}$  is computed as the union on  $ST_{outs}$  of all predecessors to B. The union is performed because if the value is stale along any path to the merge point, it is possible that the stale value might be used later. Hence, the union

15:20 • Y. Huang et al.

operation preserves the fact that the value is stale along some path. Finally,  $E_{in}$  is computed as the union of  $E_{outs}$  of all predecessors to  $B_{ein}[B]$  holds a value's history of most recent evictions from any location along all preceding paths.

As shown on lines 33–35 of Figure 6, the function mergeFlow() also collects the inconsistent L datasets, where a common location at a merge point holds the different values from the preceding paths. With a correct register allocation, different values cannot flow past merge points in a common location. Thus, it is safe to assume that these different values are evicted from the common location at the merge. The merge point (the label of a block) is also recorded to indicate where the inconsistency is exposed, and the resulting datasets are collected into the E set to help error reporting.

The data flow equations in Section 3.2.1 indicate that ST records a subset of L. In other words, ST records the locations that hold a stale value and L records all the locations that hold any value. As  $L_{inconsistent}$  is not recorded in  $L_{in}$ , there is no reason to continuously record it in  $ST_{in}$ . For optimization,  $L_{inconsistent}$  is removed from  $ST_{in}$  at line 36 in the pseudocode.

# 3.3 Checking and Reporting (errAnalysis)

Once L, ST, and E are collected, they are used to check the output code. The error analysis step ensures that the value flow from the input is preserved in the output. The algorithm for identifying and reporting errors is shown in Figure 7.

The errAnalysis algorithm iterates over all instructions in the output code. It calls **useCheck(**) when processing every *noncopy* instruction. A *copy* type instruction is implicitly checked due to the value propagation performed in defAnalysis. useCheck verifies whether all uses in each *noncopy* instruction are correct in terms of the input value flow. It reports the error location and type for any value flow violations. For each use l, it consults the mappings to determine which value l should use. When l actually holds v, which is recorded as a triple (l, v, \*) in  $L_in$ , useCheck further verifies if v in l is stale. Next, useCheck checks if v is in other locations. If so, then a wrong operand is used. Otherwise, an eviction error must have occurred. The history of v's most recent eviction from any location is reported.

#### 3.4 SARAC Applied to the Example

Based on the example in Figure 1, this section illustrates how SARAC works. We describe how SARAC can detect the errors in the incorrect output code (Figure 1(d)) from the example.

3.4.1 *Mapping Information*. When mapGen() is applied to the input and the incorrect output code in Figure 1, the mappings generated are as in Figure 8. The mappings in bold are the ones that relate to the instructions where there are errors. For example, at output instruction 4, the mapping indicates that the second register source operand, r[1], expectedly holds  $v_0$ .

```

1: errAnalysis(output, mappings, sets) {

2:

L:=sets.L; ST:=sets.ST; E:=sets.E;

3:

foreach (Block B∈output) {

4:

foreach (Instruction i∈B) {

5:

if (¬isCopy(i)=true)

6:

useCheck(i,mappings,L,ST,E);

7:

}

8:

}

9: }

10: useCheck(i,mappings,L,ST,E) {

11:

foreach (Opnd l∈uses(i)) {

12:

Opnd v := getMapping(i, l, mappings);

13:

if ((l,v,*) \in L_in[i]) {

14:

if ((1,v,c)∈ST_in[i])

15:

ε := "iuses stale value, c made v in l become stale";

16:

else

17:

\varepsilon := null;

18:

} elsif ((l',v,c)∈L_in[i] and (l',v,*)∉ST_in[i])

\epsilon := "iuses wrong operand, but c defined v in l'";

19:

20:

else {

21:

\forall(l',v,c)\inE_in[i];

22:

ε := "iuses evicted value, c evicted v from l'";

23:

}

24:

}

25: }

```

Fig. 7. Pseudocode for checking algorithm.

```

0:1:DEF:M[m] \mapsto v_0

1:1:DEF:r[2] \mapsto v<sub>3</sub>

1:1:USE:#0 → #0

2:1:DEF:r[2] \mapsto v_1

2:1:USE:#1 → #1

3:2:USE:#0 → #0

3:1:USE:r[1] \mapsto v_0

4:1:DEF:r[2] \mapsto v_2

4:1:USE:r[1] \rightarrow v_0

4:2:USE:r[1] → v<sub>1</sub> //err1

5:1:USE:r[2] \mapsto v_2

5:2:USE:#0 → #0

6:1:DEF:r[2] \mapsto v_3

6:1:USE:r[2] → v<sub>3</sub> 6:2:USE:#1 → #1 //err2

8:1:USE:r[2] → v<sub>1</sub> 8:2:USE:#1 → #1 //err3

8:1:DEF:r[2] \mapsto v_1

9:1:DEF:r[2] \mapsto v_4

9:1:USE:r[2] \mapsto v_1

9:2:USE:r[1] \mapsto v<sub>0</sub>

10:1:USE:r[2] \mapsto v<sub>4</sub> 10:2:USE:#1\mapsto #1

```

Fig. 8. Mappings between the incorrect ouput and input code in Figure 1.

3.4.2 Data Flow Sets. When the defAnalysis algorithm converges, L, ST, and E have been computed at each instruction of the output code. Figure 9 shows the data flow sets for some selected points in the incorrect output. Figure 9 uses solid horizontal lines to mark different basic blocks of the output. Consider two merge points in the example. First, the merge point (L1) shows the joined data flow sets of two blocks, which end by instructions 3 and 10. Similarly, the merge (L2) shows the joined data flow sets from instructions 5 and 25. The data flow sets are not changed when there is no destination operand in an instruction. In the figure, the data flow sets after instruction 22 are the same as the ones

### 15:22 • Y. Huang et al.

| Places        | Location Set (L)                                                                                                                                                                                                                                                                                                                                                         | Stale Set (ST)                                               | Eviction Set (E)                                                                                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| After<br>22/3 | (M[m], v <sub>0</sub> , <0>), (r[1], v <sub>0</sub> , <0, 20>),<br>(M[c], v <sub>3</sub> , <1, 21>), (r[2], v <sub>1</sub> , <2>),<br>(M[d], v <sub>1</sub> , <2, 22>)                                                                                                                                                                                                   |                                                              | (r[2],v <sub>3</sub> ,<2>)                                                                                                                                                                                      |

| L1            | (M[m],v <sub>0</sub> ,<0>),(r[1],v <sub>0</sub> ,<0,20>),<br>(M[c],v <sub>3</sub> ,<1,21>),(M[d],v <sub>1</sub> ,<2,22>),<br>(M[d],v <sub>1</sub> ,<8,27>)                                                                                                                                                                                                               | (M[c],v <sub>3</sub> ,<6>)                                   | $ \begin{array}{l} (r[2], v_3, <2>), (M[d], v_3, ), \\ (r[2], v_2, <24>), (r[2], v_2, ), \\ (r[2], v_3, ), (r[2], v_1, <9>), \\ (r[2], v_1, ), (r[2], v_4, ) \end{array} $                                      |

| After<br>23   | <pre>(M[m], v<sub>0</sub>, &lt;0&gt;), (r[1], v<sub>0</sub>, &lt;0, 20&gt;),<br/>(M[c], v<sub>3</sub>, &lt;1, 21&gt;), (M[d], v<sub>1</sub>, &lt;2, 22&gt;),<br/>(M[d], v<sub>1</sub>, &lt;8, 27&gt;), (r[2], v<sub>1</sub>, &lt;2, 22, 23&gt;),<br/>(r[2], v<sub>1</sub>, &lt;8, 27, 23&gt;)</pre>                                                                      | (M[c],v <sub>3</sub> ,<6>)                                   | $(r[2], v_3, <2>), (M[d], v_3, ), (r[2], v_2, <24>), (r[2], v_2, ), (r[2], v_3, ), (r[2], v_4, )$                                                                                                               |

| After<br>4/5  | $ \begin{array}{l} (M[m],v_0,<\!\!0\!\!>),(r[1],v_0,<\!\!0,20\!\!>),\\ (M[c],v_3,<\!\!1,21\!\!>),(M[d],v_1,<\!\!2,22\!\!>),\\ (M[d],v_1,<\!\!8,27\!\!>),(r[2],v_2,<\!\!4\!\!>) \end{array} $                                                                                                                                                                             | (M[c],v <sub>3</sub> ,<6>)                                   | <pre>(r[2],v<sub>3</sub>,&lt;2&gt;),(M[d],v<sub>3</sub>,<l2>),<br/>(r[2],v<sub>3</sub>,<l2>),(r[2],v<sub>1</sub>,&lt;4&gt;),<br/>(r[2],v<sub>4</sub>,<l1>)</l1></l2></l2></pre>                                 |

| After<br>24   | $\begin{array}{l} (\texttt{M[m]},\texttt{v}_0,<\texttt{O}>),(\texttt{r[1]},\texttt{v}_0,<\texttt{O},2\texttt{O}>),\\ (\texttt{M[c]},\texttt{v}_3,<\texttt{1},2\texttt{1}>),(\texttt{M[d]},\texttt{v}_1,<\texttt{2},2\texttt{2}>),\\ (\texttt{M[d]},\texttt{v}_1,<\texttt{8},2\texttt{7}>),(\texttt{r[2]},\texttt{v}_3,<\texttt{1},2\texttt{1},2\texttt{4}>) \end{array}$ | (M[c],v <sub>3</sub> ,<6>),<br>(r[2],v <sub>3</sub> ,<6,24>) | (M[d], v <sub>3</sub> , <l2>), (r[2], v<sub>1</sub>, &lt;4&gt;),<br/>(r[2], v<sub>2</sub>, &lt;24&gt;), (r[2], v<sub>4</sub>, <l1>)</l1></l2>                                                                   |

| After<br>6    | <pre>(M[m], v<sub>0</sub>, &lt;0&gt;), (r[1], v<sub>0</sub>, &lt;0, 20&gt;),<br/>(M[c], v<sub>3</sub>, &lt;1, 21&gt;), (M[d], v<sub>1</sub>, &lt;2, 22&gt;),<br/>(M[d], v<sub>1</sub>, &lt;8, 27&gt;), (r[2], v<sub>3</sub>, &lt;6&gt;)</pre>                                                                                                                            | (M[c],v <sub>3</sub> ,<6>)                                   | (M[d], v <sub>3</sub> , <l2>), (r[2], v<sub>1</sub>, &lt;4&gt;),<br/>(r[2], v<sub>2</sub>, &lt;24&gt;), (r[2], v<sub>4</sub>, <l1>)</l1></l2>                                                                   |

| After<br>25   | (M[m],v <sub>0</sub> ,<0>),(r[1],v <sub>0</sub> ,<0,20>),<br>(M[c],v <sub>3</sub> ,<1,21>),(r[2],v <sub>3</sub> ,<6>),<br>(M[d],v <sub>3</sub> ,<6,25>)                                                                                                                                                                                                                  | (M[c],v <sub>3</sub> ,<6>)                                   | (r[2],v <sub>1</sub> ,<4>),(r[2],v <sub>2</sub> ,<24>),<br>(r[2],v <sub>4</sub> , <l1>),(M[d],v<sub>1</sub>,&lt;25&gt;)</l1>                                                                                    |

| L2            | (M[m],v <sub>0</sub> ,<0>),(r[1],v <sub>0</sub> ,<0,20>),<br>(M[c],v <sub>3</sub> ,<1,21>)                                                                                                                                                                                                                                                                               | (M[c],v <sub>3</sub> ,<6>)                                   | $ \begin{array}{l} (r[2], v_3, <2>), (r[2], v_1, <4>), \\ (r[2], v_2, <2<), (r[2], v_4, ), \\ (M[d], v_1, <25>), (M[d], v_1, ), \\ (r[2], v_2, ), (r[2], v_3, ), \\ (M[d], v_3, ) \end{array} $                 |

| After<br>26   | (M[m],v <sub>0</sub> ,<0>),(r[1],v <sub>0</sub> ,<0,20>),<br>(M[c],v <sub>3</sub> ,<1,21>)                                                                                                                                                                                                                                                                               | (M[c],v <sub>3</sub> ,<6>)                                   | $ \begin{array}{l} (r[2], v_3, <2>), (r[2], v_1, <4>), \\ (r[2], v_2, <24>), (r[2], v_4, ), \\ (M[d], v_1, <25>), (M[d], v_1, ), \\ (r[2], v_2, ), (r[2], v_3, ), \\ (M[d], v_3, ) \end{array} $                |

| After<br>9/10 | (M[m],v <sub>0</sub> ,<0>),(r[1],v <sub>0</sub> ,<0,20>),<br>(M[c],v <sub>3</sub> ,<1,21>),(M[d],v <sub>1</sub> ,<8,27>),<br>(r[2],v <sub>4</sub> ,<9>)                                                                                                                                                                                                                  | (M[c],v <sub>3</sub> ,<6>)                                   | <pre>(r[2],v<sub>3</sub>,&lt;2&gt;),(r[2],v<sub>2</sub>,&lt;24&gt;),<br/>(M[d],v<sub>3</sub>,<l2>),(r[2],v<sub>2</sub>,<l2>),<br/>(r[2],v<sub>3</sub>,<l2>),(r[2],v<sub>1</sub>,&lt;9&gt;)</l2></l2></l2></pre> |

Fig. 9. Data flow sets at selected instructions of the incorrect output in Figure 1.

after instruction 3. These data flow sets are also the same for instructions after 4 and 5 and for instructions after 9 and 10.

3.4.3 *Identify Errors.* Incorrect edits in the incorrect output of Figure 1 are identified by errAnalysis using the data flow sets (Figure 9) and the mappings (Figure 8). The incorrect edits are: an incorrect register assignment at instruction 4 and a wrong spill at 25.

At instruction 4, mappings indicate that the second source operand r[1] is expected to hold  $v_1$ . However, after instruction 23, *L* reports that  $v_1$  is actually in r[2]. Therefore, a wrong operand error is reported. *L* also reports that  $v_1$ flows into r[2] along two paths. First,  $v_1$  is defined at instruction 2, spilled to M[d] at 22, and reloaded into r[2] at 23. Second,  $v_1$  is defined at 8, spilled to M[d] at 27, and reloaded into r[2] at 23. This information will help a compiler engineer discover that  $v_1$  is in r[2] at instruction 4 and r[2] should have been used as the second source operand. A register assignment error is identified.

At instruction 6, the mapping information states that source operand r[2] should hold  $v_3$ . After instruction 24, the *L* set indicates that r[2] does in fact hold  $v_3$ . However, *ST* reports that the value of  $v_3$  in r[2] is stale. Triple

$(r[2], v_3, <6, 24>)$  in *ST* indicates that the value of  $v_3$  in memory is stale due to the new definition of  $v_3$  (into r[2]) at instruction 6. The stale value of  $v_3$  is loaded into r[2] at instruction 24. Another triple in *ST*, (M[c],  $v_3, <6>$ ), indicates that the value of  $v_3$  in M[c] remains stale because the newly defined  $v_3$  is never spilled to M[c] along the loop's back edge. This error is attributed to the wrong spill code edit at 25, where the newly defined  $v_3$  (in r[2]) is incorrectly spilled to M[d].

At instruction 8, the mappings show that the source operand r [2] should hold  $v_1$ . The *L* set, however, tells that  $v_1$  is not in any location. An eviction error is reported. The *L* set after instruction 26 shows that no value is loaded into r [2] by the load instruction 26. There is no value in M[d] when the control flow merges at L2, which is indicated by triples (M[d],  $v_1$ , <L2>) and (M[d],  $v_3$ , <L2>) in *E*. That is,  $v_1$  is evicted from M[d] due to inconsistencies among the *L* sets from the predecessors. The preceding path ending at instruction 5 shows that  $v_1$  is in M[d], which is indicated by triples (M[d],  $v_1$ , <2, 22>) and (M[d],  $v_1$ , <8, 27>) in *L*. The other path ending at instruction 25 shows that  $v_3$  is in M[d], which is indicated by triples (M[d] flowing past L2. Triple (M[d],  $v_3$ , <6, 25>) in *L*. Therefore, the values in M[d] are inconsistent and there is no valid value in M[d] flowing past L2. Triple (M[d],  $v_3$ , <6, 25>) in *L* shows how  $v_3$  flows into M[d].  $v_3$  is defined in r [2] at instruction 6 and spilled to the wrong memory location M[d] at 25. The eviction error is caused by the wrong spill edit at instruction 25.

#### 3.5 Extensions

Two important extensions to a register allocator are rematerialization [Briggs et al. 1992, 1994; Chaitin 1982; George and Appel 1996] and register aliasing [Smith et al. 2004]. This section describes how SARAC supports these extensions.

3.5.1 *Rematerialization*. Rematerialization improves spill code by recomputing values rather than reloading them from memory. The recomputed values are not touched by the register allocator; only the rematerialized instructions are moved (usually the instruction ID is changed). Rematerialization is done for constant expressions in the code, such as integer constants in load-immediate instructions and address offsets.

To handle rematerialization, our approach is extended to minimally use information from the allocator. The assumption about strict independence from the register allocator is relaxed to let the allocator indicate to SARAC the mapping information used for rematerialized instructions. The mapping information given by the register allocator is not necessarily assumed to be correct. Any incorrect rematerialization will be exposed and caught by SARAC's data flow analyses.

3.5.2 *Register Aliasing.* Many processor architectures allow registers from different subregister classes to overlap. Such overlapping registers are defined as a "register alias set" [Smith et al. 2004]. For instance, the Intel IA-32 has registers AL and AH in the 8-bit register class. These two registers overlap with registers AX in the 16-bit register class and EAX in the 32-bit register class.

15:24 • Y. Huang et al.

The "register alias set" of AL and AH is {AL, AX, EAX} and {AH, AX, EAX} respectively. The register allocator has to consider the overlap when assigning subregister classes because a write to a register will destroy the value in any register of its alias set.