## **Trace-Based Dynamic Binary Parallelization**

A Dissertation

Presented to the Faculty of the School of Engineering and Applied Science University of Virginia

> In Partial Fulfillment of the requirements for the Degree Doctor of Philosophy (Computer Science)

> > by

Jing Yang June 2012

© 2012 Jing Yang

# Abstract

With the number of cores increasing rapidly but the performance per core increasing slowly at best, software must be parallelized in order to improve performance. Manual parallelization is often prohibitively time-consuming and error-prone (especially due to data races and memory-consistency complexities), and some portions of code may simply be too difficult to understand or refactor for parallelization. Most existing automatic parallelization techniques are performed statically at compile time and require source code to be analyzed, leaving a large fraction of software behind. In many cases, some or all of the source code and development tool chain is lost or, in the case of third-party software, was never available. Furthermore, modern applications are assembled and defined at run time, making use of shared libraries, virtual functions, plugins, dynamically-generated code, and other dynamic mechanisms, as well as multiple languages. All these aspects of separate compilation prevent the compiler from obtaining a holistic view of the program, leading to the risk of incompatible parallelization techniques, subtle data races, and resource over-subscription. All the above considerations motivate dynamic binary parallelization (DBP).

This dissertation explores the novel idea of trace-based DBP, which provides a large instruction window without introducing spurious dependencies. We hypothesize that traces provide a generally good trade-off between code visibility and analysis accuracy for a wide variety of applications so as to achieve better parallel performance. Compared to the raw dynamic instruction stream (DIS), traces expose more distant parallelism opportunities because their average length is typically much larger than the size of the hardware instruction window. Compared to the complete control flow graph (CFG), traces only contain control and data dependencies on the execution path which is actually taken. More importantly, while DIS-based DBP typically only exploits fine-grained parallelism and CFG-based DBP typically only exploits coarse-grained parallelism, traces can be used as a unified representation of program execution to seamlessly incorporate the exploitation of both coarse- and fine-grained parallelism.

We develop Tracy, an innovative DBP framework which monitors a program at run time and

### Abstract

dynamically identifies hot traces, parallelizes them, and caches them for later use so that the program can run in parallel every time a hot trace repeats. Our experimental results have demonstrated that for floating point benchmarks, Tracy can achieve an average speedup of 1.99x, 1.39x better than the speedup achieved by Core Fusion, one representative of DIS-based DBP techniques. Although the average speedup achieved by Tracy is only 1.08x better than the speedup achieved by CFG-based DBP, Tracy can speed up all floating point benchmarks while CFG-based DBP fails to parallelize three out of eight applications at all. The performance of Tracy is not always better than the performance of existing DIS- and CFG-based DBP techniques. However, it takes the first step to dynamically parallelize the binary executable without using either the raw DIS or the complete CFG. Thus, this dissertation is expected have a broad impact on future researchers who explore other representations of program execution for DBP purposes.

## Approval Sheet

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science)

Jing Yang

This dissertation has been read and approved by the Examining Committee:

Mary Lou Soffa, Advisor

Kamin Whitehouse, Advisor

Kevin Skadron, Committee Chair

Westley Weimer

Mircea Stan, Minor Representative

Accepted for the School of Engineering and Applied Science:

James H. Aylor, Dean, School of Engineering and Applied Science

June 2012

To my parents, Yifeng Yang and Yajuan Dai.

# Acknowledgments

For my advisors, Prof. Mary Lou Soffa, Prof. Kamin Whitehouse and Prof. Kevin Skadron, who continuously stimulated my interests in research and encouraged me during those hard times. Their invaluable advice and selfless supports in both professional and personal matters will be forever remembered in the rest of my life.

For my parents, Yifeng Yang and Yajuan Dai, who always respected and supported my choices. Daddy, I believe you are watching over me all the time from heaven.

For my wife, Dr. Meng Wang, who gives me endless love and understands me more than anyone else. I promise that our life will become much better from now on.

For my committee members, Prof. Westley Weimer and Prof. Mircea Stan, who followed my research for several years and always provided insightful suggestions and comments.

For my academic brothers and sisters, Shukang Zhou, Prof. Wei Le, Dr. Apala Guha, Na Zhang, Nguyet Nguyen, Dr. Jason Mars, Dr. Lingjia Tang, Wei Wang, and Tanima Dey, who spent many hours with me in the lab coding, debuging, and fighting for paper deadlines. Your jokes and encouragement made my graduate life much more colorful and enjoyable.

For my friends, Jingbin Zhang, Prof. Shan Lin, Weide Zhang, Dr. Jiakang Lu, Dr. Jiayuan Meng, Dr. Hengchang Liu, Yu Yao, Dr. Tao Long, Ning Zhang, Xiaopu Wang, Dr. Jun Liu, Prof. Roseanne Ford, Dr. Naveen Kumar, Dr. Daniel Williams, Dr. Gogul Balakrishnan, Dr. Franjo Ivancic, Dr. Naoto Maeda, Dr. Aarti Gupta, and Dr. Weihong Li, who spent a lot of good time with me at the University of Virginia and NEC Laboratories America.

# Contents

| $\mathbf{C}$ | onter                | nts                                                                                                      | $\mathbf{vi}$  |

|--------------|----------------------|----------------------------------------------------------------------------------------------------------|----------------|

|              | List                 | of Tables                                                                                                | viii           |

|              | List                 | of Figures                                                                                               | ix             |

| 1            | Intr                 | roduction                                                                                                | 1              |

| _            | 1.1                  | Problems of State-of-the-Art DBP                                                                         | $\overline{2}$ |

|              | 1.2                  | Challenges of Trace-Based DBP                                                                            | 4              |

|              | 1.4                  | 1.2.1       Trace Construction and Prediction                                                            | 4              |

|              |                      | 1.2.1       Trace Construction and Prediction         1.2.2       Trace Optimization and Parallelization | 5              |

|              | 1.3                  | Research Overview                                                                                        | 6              |

|              | 1.3                  | Contributions of the Dissertation                                                                        | 9              |

|              |                      |                                                                                                          |                |

|              | 1.5                  | Organization of the Dissertation                                                                         | 10             |

| <b>2</b>     | Bac                  | kground and Related Work                                                                                 | 11             |

|              | 2.1                  | Evolution of Traces                                                                                      | 11             |

|              | 2.2                  | Software Dynamic Translation                                                                             | 12             |

|              | 2.3                  | Manual Parallelization                                                                                   | 14             |

|              | 2.4                  | Automatic Parallelization                                                                                | 15             |

|              |                      | 2.4.1 Static Source Parallelization                                                                      | 16             |

|              |                      | 2.4.2 Static Binary Parallelization                                                                      | 17             |

|              |                      | 2.4.3 Dynamic Source Parallelization                                                                     | 17             |

|              |                      | 2.4.4 Dynamic Binary Parallelization                                                                     | 18             |

|              |                      |                                                                                                          |                |

| 3            | $\operatorname{Lim}$ | nit Study on Parallelizing Traces                                                                        | <b>21</b>      |

|              | 3.1                  | Overcoming Inherent Handicaps of Static Parallelization                                                  | 21             |

|              | 3.2                  | Limit Study Setup                                                                                        | 22             |

|              |                      | 3.2.1 Recording Execution Sequences                                                                      | 23             |

|              |                      | 3.2.2 Analyzing Execution Sequences to Construct Repeating Traces                                        | 24             |

|              |                      | 3.2.3 Parallelizing Execution Sequences                                                                  | 26             |

|              |                      | 3.2.4 Modeling Parallel Execution Time                                                                   | 28             |

|              |                      | 3.2.5 Verifying Parallel Execution Sequences                                                             | 29             |

|              | 3.3                  | Experimental Results                                                                                     | 29             |

|              |                      | 3.3.1 Analysis of Trace Construction                                                                     | 30             |

|              |                      | 3.3.2 Analysis of Trace Parallelization                                                                  | 34             |

|              |                      | 3.3.3 Analysis of Constant Propagation and Value Prediction                                              | 35             |

|              | 3.4                  | Summary                                                                                                  | 35             |

|              | -                    |                                                                                                          | ~ -            |

| 4            |                      | e Tracy Framework                                                                                        | 37             |

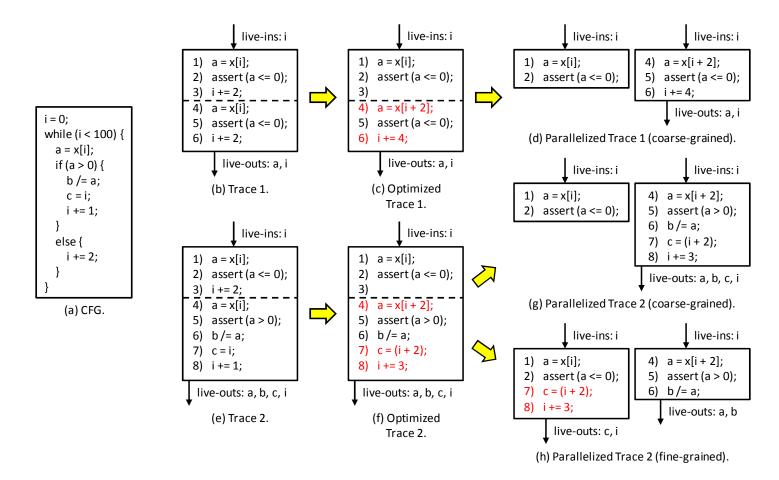

|              | 4.1                  | Motivating Example                                                                                       | 39             |

|              | 4.2                  | Execution Model Justification                                                                            | 39             |

|              | 4.3                  | Hardware Architecture                                                                                    | 41             |

|              |                      | 4.3.1 Supporting Low-Latency Intra-Cluster Communication                                                 | 42             |

|              |                      | 4.3.2 Supporting Multi-Trace Execution                                                                   | 43             |

|                                     | 4.4   | Summary                                                              | 45         |  |

|-------------------------------------|-------|----------------------------------------------------------------------|------------|--|

| 5 Trace Construction and Prediction |       |                                                                      |            |  |

|                                     | 5.1   | Extending Branch Promotion                                           | 47         |  |

|                                     | 5.2   | Exploiting Hierarchical Code Structures                              | 51         |  |

|                                     |       | 5.2.1 Selecting Starting and Ending Points                           | 53         |  |

|                                     |       | 5.2.2 Appending Retired Instructions                                 | 54         |  |

|                                     |       | 5.2.3 Inserting into the Trace Cache                                 | $54 \\ 54$ |  |

|                                     | ۲۹    |                                                                      |            |  |

|                                     | 5.3   | Adaptive Speculation                                                 | 55         |  |

|                                     | 5.4   | Experimental Setup                                                   | 56         |  |

|                                     |       | 5.4.1 Architectures                                                  | 56         |  |

|                                     |       | 5.4.2 Algorithms                                                     | 57         |  |

|                                     |       | 5.4.3 Benchmarks                                                     | 57         |  |

|                                     |       | 5.4.4 Evaluation Methodology                                         | 58         |  |

|                                     | 5.5   | Experimental Results                                                 | 59         |  |

|                                     | 5.6   | Summary                                                              | 62         |  |

|                                     | 0.0   |                                                                      | 02         |  |

| 6                                   | Tra   | ce Optimization                                                      | 64         |  |

|                                     | 6.1   | Symbolic Execution                                                   | 66         |  |

|                                     | 6.2   | Memory Disambiguation                                                | 70         |  |

|                                     | 6.3   | Experimental Setup                                                   | 72         |  |

|                                     | 6.4   | Experimental Results                                                 | 75         |  |

|                                     | -     |                                                                      |            |  |

|                                     | 6.5   | Summary                                                              | 76         |  |

| 7                                   | Tra   | ce Parallelization                                                   | 77         |  |

| •                                   | 7.1   | Exploiting ILP                                                       | 77         |  |

|                                     | 7.2   | Exploiting LLP                                                       | 78         |  |

|                                     | 7.3   | Combining ILP and LLP.                                               | 80         |  |

|                                     |       |                                                                      |            |  |

|                                     | 7.4   | Experimental Setup                                                   | 81         |  |

|                                     | 7.5   | Experimental Results                                                 | 81         |  |

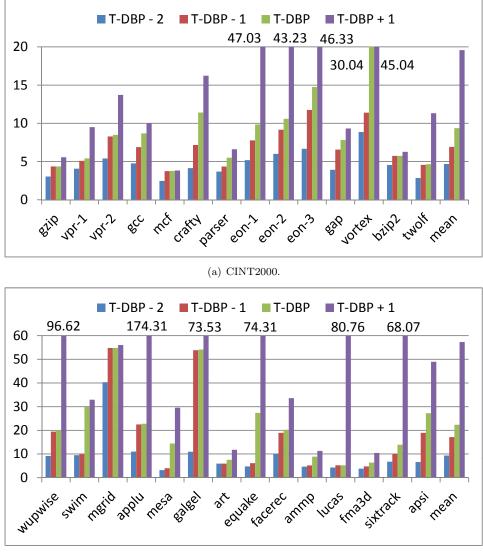

|                                     |       | 7.5.1 Overall Performance using Different Parallelization Startegies | 83         |  |

|                                     |       | 7.5.2 Upgrading to OoO Cores                                         | 86         |  |

|                                     |       | 7.5.3 Comparing to DIS- and CFG-Based DBP Techniques                 | 88         |  |

|                                     |       | 7.5.4 Changing System Configurations and Architectural Parameters    | 90         |  |

|                                     |       | 7.5.5 Isolating Overheads and Benefits                               | 100        |  |

|                                     | 7.6   | Summary                                                              | 101        |  |

|                                     |       | v                                                                    |            |  |

| 8                                   | Con   | nclusions and Future Work                                            | 103        |  |

|                                     | 8.1   | Merits of the Dissertation                                           | 104        |  |

|                                     | 8.2   | Future Work                                                          | 105        |  |

|                                     |       | 8.2.1 Balancing and Integrating Coarse- and Fine-Grained Parallelism | 106        |  |

|                                     |       | 8.2.2 Resource Allocation                                            | 107        |  |

|                                     |       | 8.2.3 Portability and Robustness to Runtime Dynamics                 | 107        |  |

|                                     |       |                                                                      |            |  |

|                                     |       |                                                                      | 108        |  |

|                                     |       | 8.2.5 Combining Tracy with Native Parallelization                    | 108        |  |

|                                     |       | 8.2.6 Implementing Tracy on Contemporary Hardware                    | 109        |  |

| Bi                                  | bliog | graphy                                                               | 110        |  |

# List of Tables

| 4.1<br>4.2   | In the MESI cache conherence protocol, each cache line is in one of four states: 1) mod-<br>ified, 2) exclusive, 3) shared, and 4) invalid                                                                                                                                                                                                                                                                                                                                                                     | 44<br>44 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.3          | State transfer of the cache line in the MESI cache conherence protocol when respond-<br>ing to messages initialized from the snoopy bus                                                                                                                                                                                                                                                                                                                                                                        | 44       |

| 5.1          | This table shows 1) the total size of unique traces that commit at least once, 2) the average length of traces that commit in each correct prediction, 3) the percentage of committed traces that are longer than 400 instructions, 4) the trace prediction accuracy, 5) the average size of the candidate trace pool and the average sorted rank of the committed trace in that pool, and 6) the percentage of instructions executed by the unmodified program that are covered by correctly predicted traces | 49       |

| 5.2          | Parameter definition of the trace construction algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51       |

| $5.3 \\ 5.4$ | Architectural parameters of $\text{Tracy}_{34}^4$ -io2.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57<br>57 |

| $5.4 \\ 5.5$ | Algorithmic parameters of trace construction and prediction. $\ldots$ $\ldots$ $\ldots$ This table shows trace-related statistical analysis of Tracy <sup>4</sup> <sub>34</sub> -io2, including 1) the                                                                                                                                                                                                                                                                                                         | 97       |

|              | percentage of instructions executed by the unmodified program that are covered by correctly predicted traces, 2) the number of traces in the trace cache, 3) the trace misprediction rate, 4) the average number of candidate traces for each prediction, and 5) the average length of the trace that commits in each correct prediction                                                                                                                                                                       | 60       |

| 5.6          | This table summarizes trace-related statistical analysis of 1) $\text{Tracy}_{10}^4$ -io2, 2) $\text{Tracy}_{18}^4$ -io2, and 3) $\text{Tracy}_{34}^4$ -io2, including 1) the percentage of instructions executed by the unmodified program that are covered by correctly predicted traces, 2) the number of traces in the trace cache, 3) the trace misprediction rate, 4) the average number of candidate traces for each prediction, and 5) the average length of the trace that                            |          |

|              | commits in each correct prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61       |

| 7.1<br>7.2   | Extra architectural parameters of 2-issue OoO cores                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81       |

| 7.3          | tions that are covered by any correctly predicted traces                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83       |

|              | proved performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87       |

# List of Figures

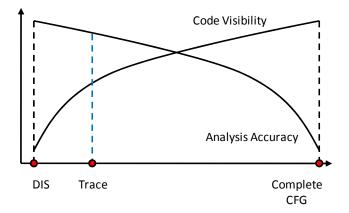

| 1.1        | Design spectrum of the representation of program execution on which parallelization is performed. Compared to DIS and complete CFG, Trace has the potential to provide a large instruction window without introducing spurious dependencies.                                                                                                | 3  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

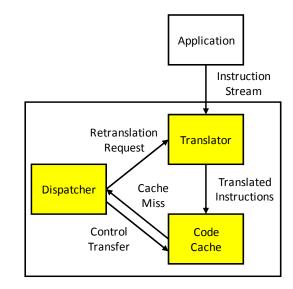

| 2.1<br>2.2 | Generic SDT systems contain three algorithmic components and transparently ma-<br>nipulate the binary executable while it is running                                                                                                                                                                                                        | 13 |

| 2.2        | code that cannot be parallelized is listed under each category                                                                                                                                                                                                                                                                              | 15 |

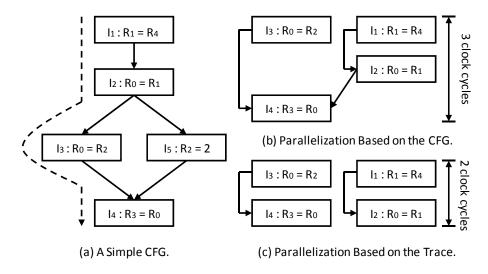

| 3.1        | Analysis of the trace (dashed arrow) produces fewer true dependencies than analysis of the CFG, leading to improved parallel performance.                                                                                                                                                                                                   | 22 |

| 3.2        | The idealized trace construction algorithm finds the most frequently repeating pat-<br>terns of instructions in the entire execution sequence, as shown in the example. The<br>handicapped version does not construct traces across boundaries between application                                                                          | 22 |

| 3.3        | and library code                                                                                                                                                                                                                                                                                                                            | 25 |

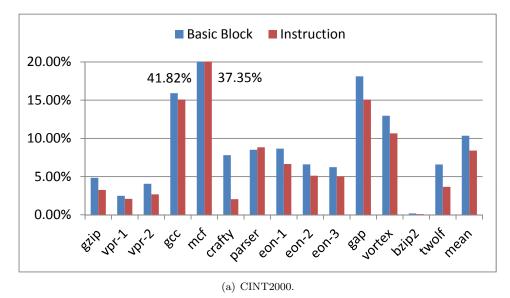

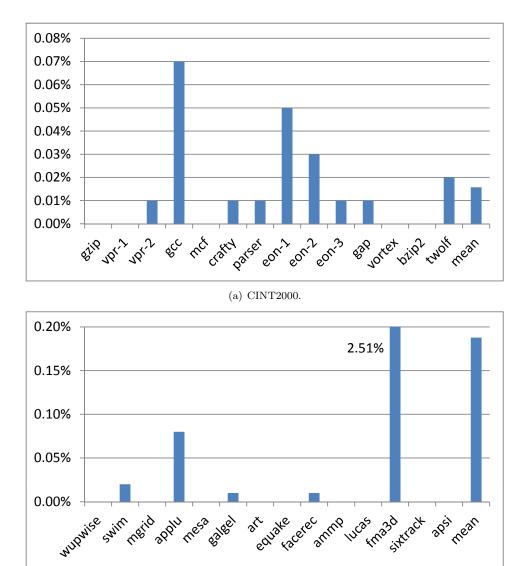

| 3.4        | for integer benchmarks and 3.49x for floating point benchmarks on average An average of 10.32% basic blocks or 8.40% instructions for integer benchmarks and 17.91% basic blocks or 11.12% instructions for floating point benchmarks belong to                                                                                             | 31 |

| 3.5        | libraries                                                                                                                                                                                                                                                                                                                                   | 32 |

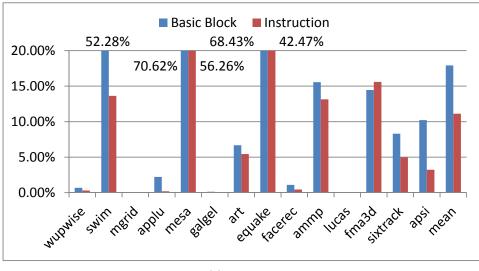

| 3.6        | blocks for floating point benchmarks                                                                                                                                                                                                                                                                                                        | 33 |

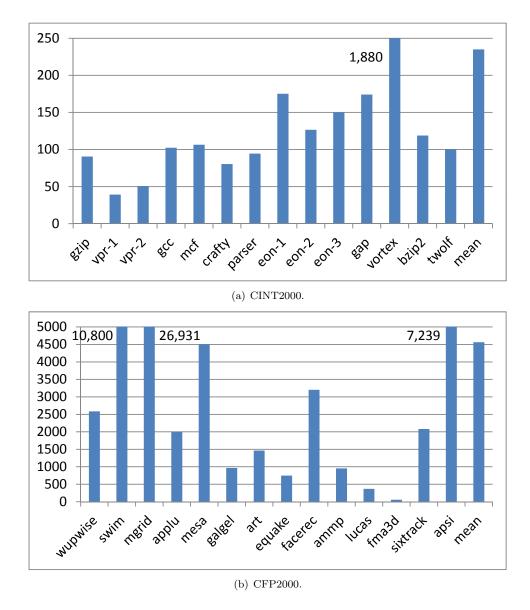

| 4.1        | floating point benchmarks are not formed into traces                                                                                                                                                                                                                                                                                        | 34 |

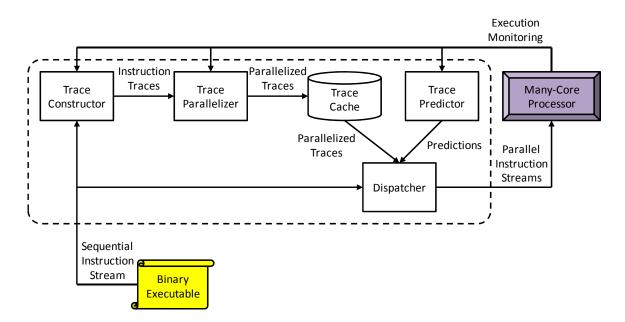

|            | parallel instruction streams.                                                                                                                                                                                                                                                                                                               | 37 |

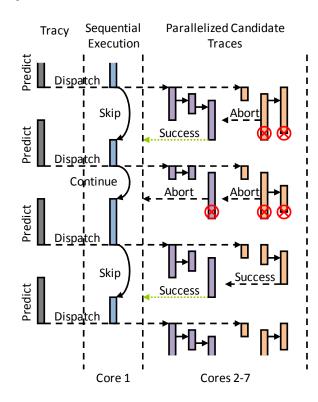

| 4.2        | Tracy uses one core for trace management plus sequential execution, and the remain-<br>ing cores for speculative execution of parallelized candidate traces.                                                                                                                                                                                | 38 |

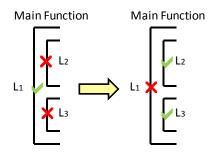

| 4.3        | Based on multi-trace execution, Tracy can successfully parallelize some applications when CFG-based DBP techniques fail to.                                                                                                                                                                                                                 | 40 |

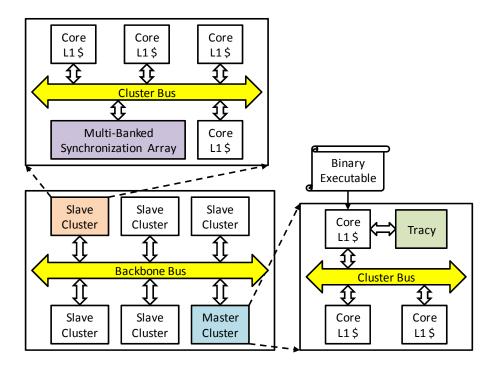

| 4.4        | Tracy assumes that a many-core chip is organized into master clusters with a specially-                                                                                                                                                                                                                                                     |    |

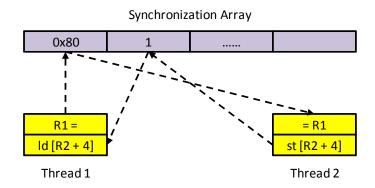

| 4.5        | instrumented core and slave clusters that contain synchronization arrays Each entry in the synchronization array is correlated to a unique register or memory reference that needs to be synchronized. While the actual value of each synchronized register is explicitly transferred through the array, a boolean value is just enough for | 42 |

|            | a pair of dependent memory references to maintain the correct order                                                                                                                                                                                                                                                                         | 42 |

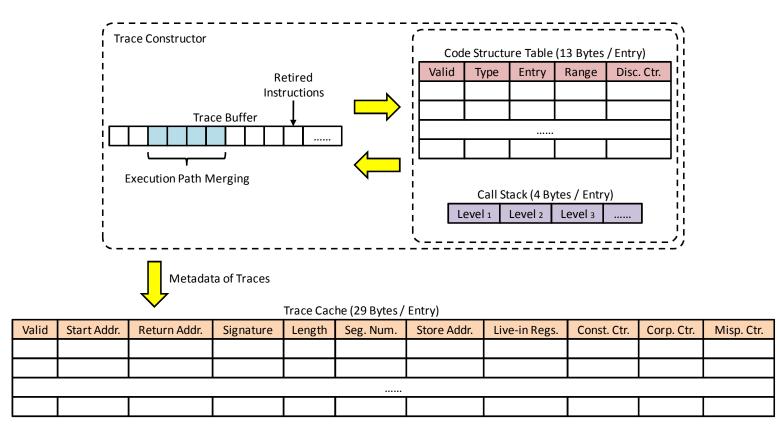

| 5.1  | Tracy constructs traces at the retire stage of each instruction. It stores traces in main memory and their metadata in the set associative trace cache on chip                                                                                                                                                                                          | 52       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.2  | Tracy starts to exploit code structures in the outermost scope, and only enters the next level if necessary.                                                                                                                                                                                                                                            | 53       |

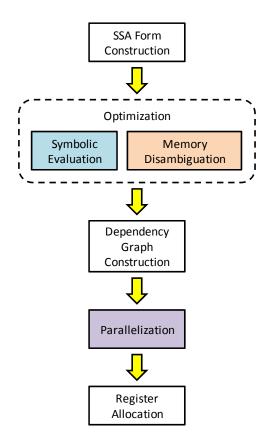

| 6.1  | Tracy optimizes and parallelizes the constructed trace in five steps                                                                                                                                                                                                                                                                                    | 64       |

| 6.2  | Tracy divides all MIPS instructions into four categories: 1) memory loads, 2) memory stores, 3) instructions that only perform integer arithmetic and logical operations (including control transfer instructions that test integer registers), and 4) all other instructions. Tracy uses different strategies to symbolically evaluate instructions in | 67       |

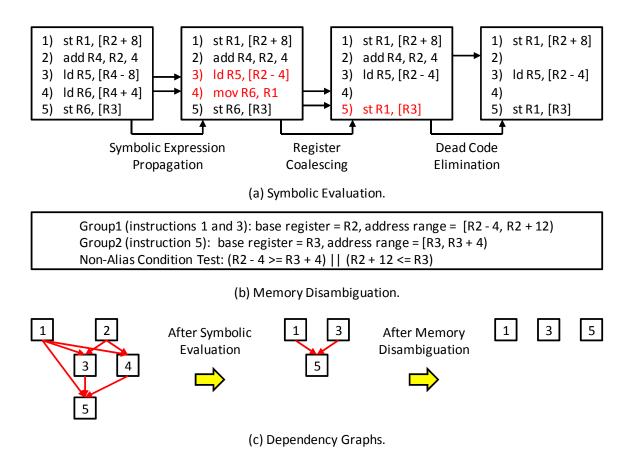

| 6.3  | different categories                                                                                                                                                                                                                                                                                                                                    | 67<br>69 |

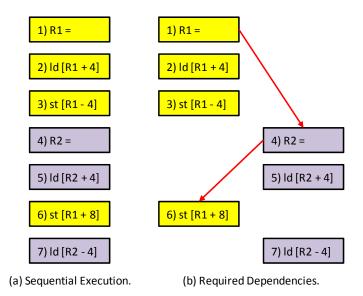

| 6.4  | Tracy inserts extra dependencies to ensure that every monitored base register receives the correct value.                                                                                                                                                                                                                                               | 71       |

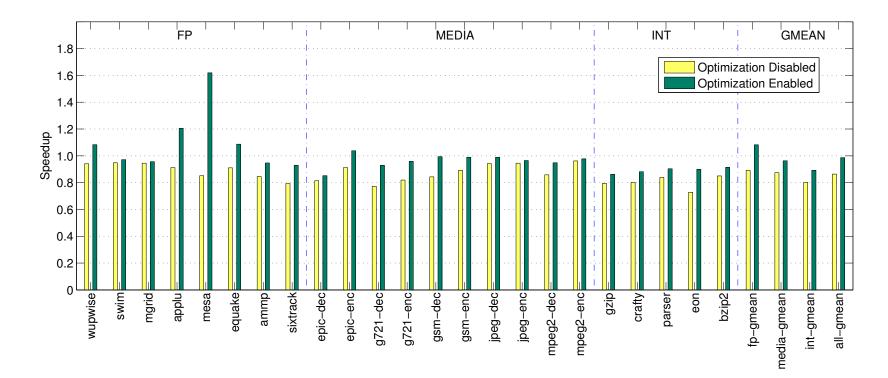

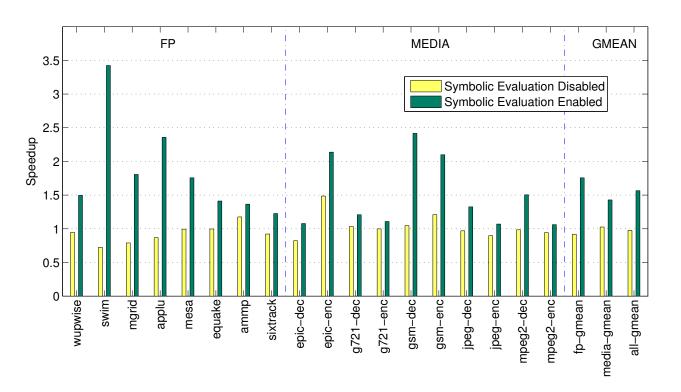

| 6.5  | This figure shows the speedup of $\text{Tracy}_{34}^4$ -io2 when 1) optimization is disabled, and 2) optimization is enabled. Results are normalized to ST-io2.                                                                                                                                                                                         | 73       |

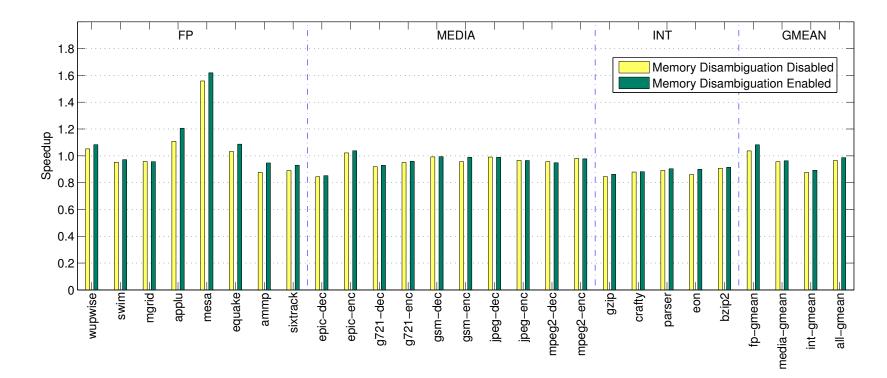

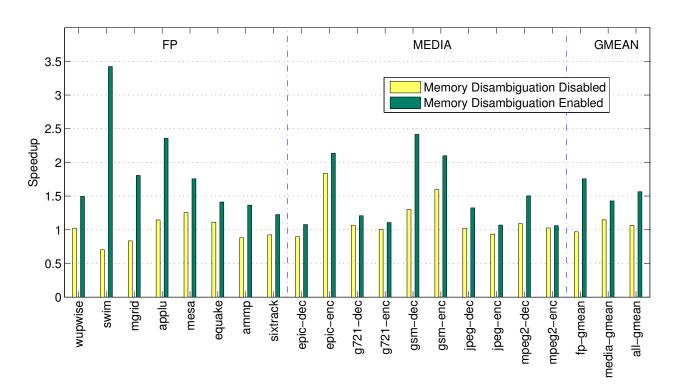

| 6.6  | This figure shows the optimization-only speedup of $\text{Tracy}_{34}^4$ -io2 when 1) memory dis-<br>ambiguation is disabled, and 2) memory disambiguation is enabled. Results are nor-                                                                                                                                                                 |          |

|      | malized to ST-io2.                                                                                                                                                                                                                                                                                                                                      | 74       |

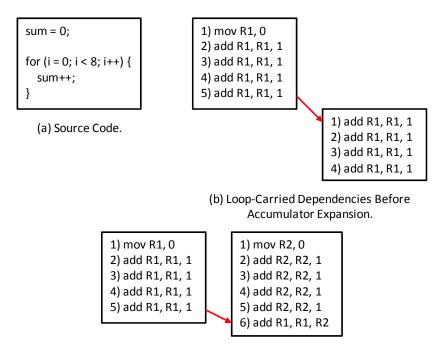

| 7.1  | Accumulator expansion replaces the single shared accumulator with multiple private accumulators.                                                                                                                                                                                                                                                        | 79       |

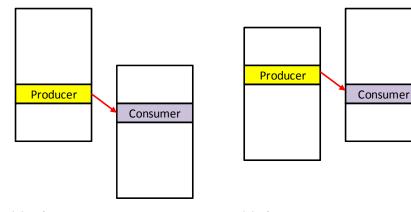

| 7.2  | Dependent code motion pushes every producer to be executed earlier and every con-<br>sumer to be executed later.                                                                                                                                                                                                                                        | 79       |

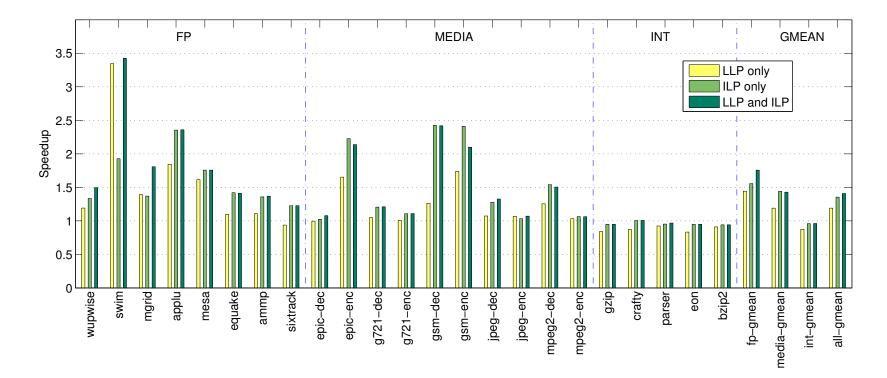

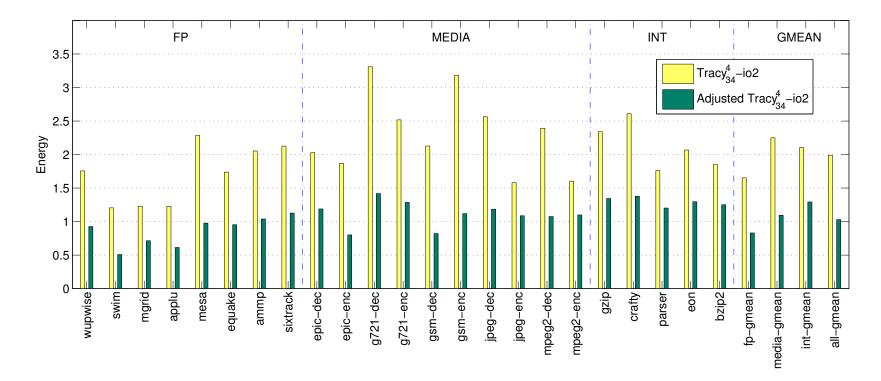

| 7.3  | This figure shows the speedup of $\text{Tracy}_{34}^4$ -io2 when it is configured to exploit 1) LLP only, 2) ILP only, and 3) both LLP and ILP. Results are normalized to ST-io2                                                                                                                                                                        | 82       |

| 7.4  | This figure shows the energy consumption of $\text{Tracy}_{34}^4$ -io2 when it is configured to exploit both LLP and ILP. Results are normalized to ST-io2. The adjusted energy consumption is achieved by counting in "system leakage" from other machine components and power supply inefficiencies.                                                  | 84       |

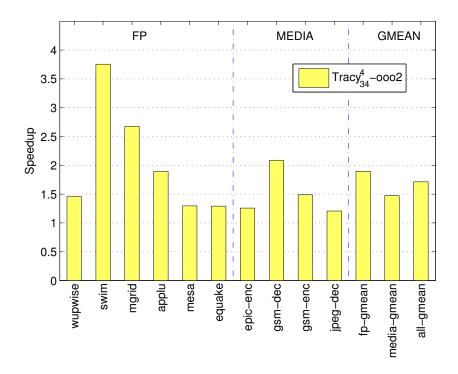

| 7.5  | This figure shows the speedup of $\operatorname{Tracy}_{34}^4$ -ooo2 when it is configured to exploit both LLP and ILP. Results are normalized to ST-ooo2.                                                                                                                                                                                              | 86       |

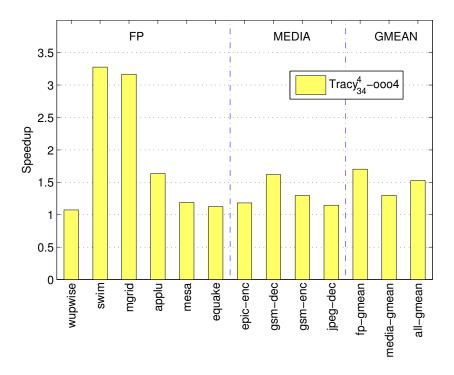

| 7.6  | This figure shows the speedup of $\operatorname{Tracy}_{34}^4$ -ooo4 when it is configured to exploit both LLP and ILP. Results are normalized to ST-ooo4.                                                                                                                                                                                              | 87       |

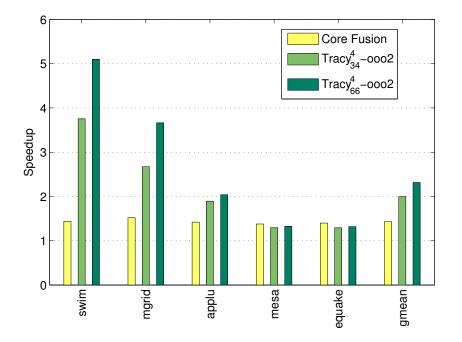

| 7.7  | This figure compares the performance of Core Fusion, one representative of DIS-based DBP, with $\text{Tracy}_{34}^4$ -0002 and $\text{Tracy}_{66}^8$ -0002 when they are configured to exploit both LLP and ILP. Results are normalized to ST-0002.                                                                                                     | 88       |

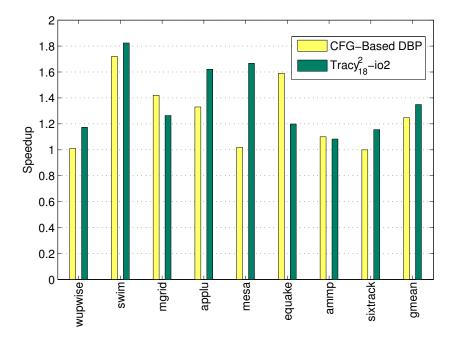

| 7.8  | This figure compares the performance of CFG-based DBP with $\text{Tracy}_{18}^2$ -io2 when it is configured to exploit both LLP and ILP. Results are normalized to ST-io2.                                                                                                                                                                              | 90       |

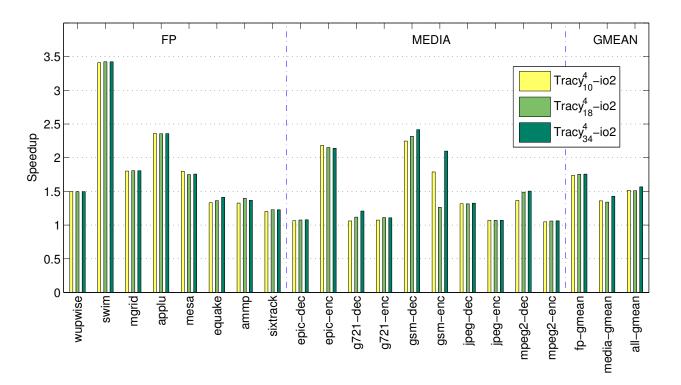

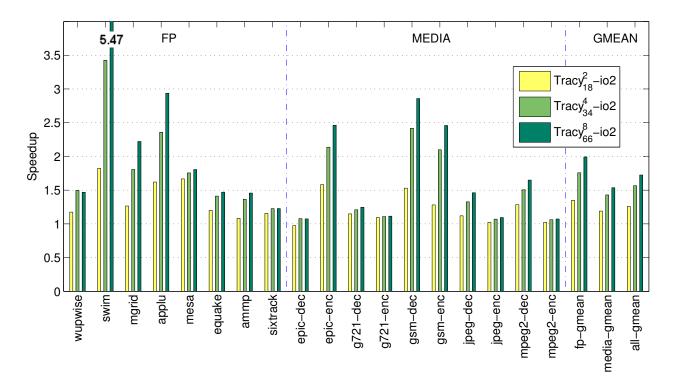

| 7.9  | This figure shows the speedup of 1) $\text{Tracy}_{10}^4$ -io2, 2) $\text{Tracy}_{18}^4$ -io2, and 3) $\text{Tracy}_{34}^4$ -io2 when they are configured to exploit both LLP and ILP. Results are normalized to                                                                                                                                        |          |

| 7.10 | ST-io2 This figure shows the speedup of 1) $\text{Tracy}_{18}^2$ -io2, 2) $\text{Tracy}_{34}^4$ -io2, and 3) $\text{Tracy}_{66}^8$ -io2 when they are configured to exploit both LLP and ILP. Results are normalized to                                                                                                                                 | 91       |

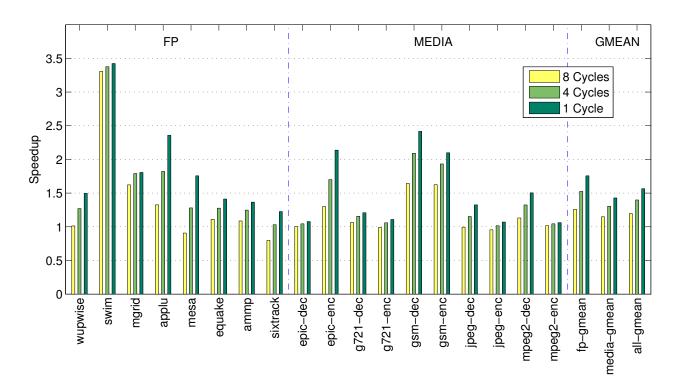

| 7.11 | ST-io2 This figure shows the speedup of $\text{Tracy}_{34}^4$ -io2 when the synchronization has access latency of 1) 8 clock cycles, 2) 4 clock cycles, and 3) 1 clock cycle. The system is                                                                                                                                                             | 92       |

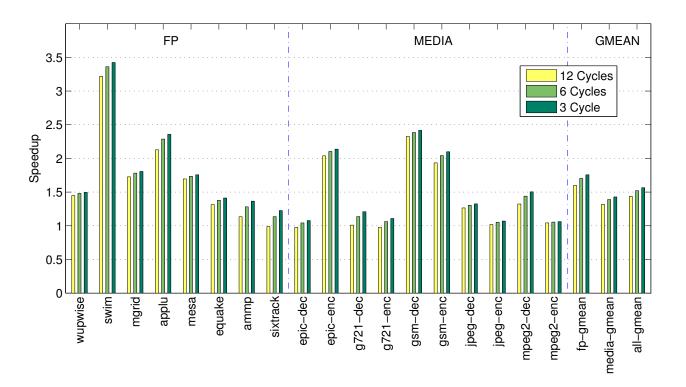

| 7.12 | configured to exploit both LLP and ILP. Results are normalized to ST-io2 This figure shows the speedup of $Tracy_{34}^4$ -io2 when the backbone bus has transfer                                                                                                                                                                                        | 93       |

|      | delay of 1) 12 clock cycles, 2) 6 clock cycles, and 3) 3 clock cycle. The system is configured to exploit both LLP and ILP. Results are normalized to ST-io2.                                                                                                                                                                                           | 94       |

| 7.13 | 13 This figure shows the speedup of $\text{Tracy}_{34}^4$ -io2 when 1) symbolic evaluation is disabled, |    |  |

|------|---------------------------------------------------------------------------------------------------------|----|--|

|      | and 2) symbolic evaluation is enabled. The system is configured to exploit both LLP                     |    |  |

|      | and ILP. Results are normalized to ST-io2.                                                              | 96 |  |

| 7.14 | This figure shows the speedup of $\text{Tracy}_{34}^4$ -io2 when 1) memory disambiguation is            |    |  |

|      | disabled, and 2) memory disambiguation is enabled. The system is configured to                          |    |  |

|      | exploit both LLP and ILP. Results are normalized to ST-io2.                                             | 97 |  |

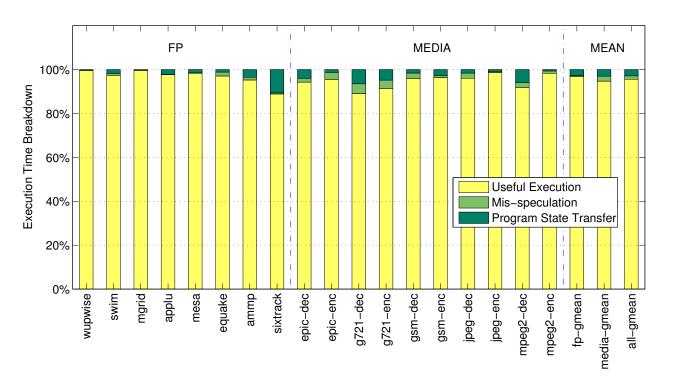

| 7.15 | This figure shows the execution time overhead of $\text{Tracy}_{34}^4$ -io2 caused by mis-speculation   |    |  |

|      | and program state transfer. The system is configured to exploit both LLP and ILP.                       |    |  |

|      | Useful execution includes the time spent on both sequential execution and parallel                      |    |  |

|      | execution that is speculated correctly.                                                                 | 98 |  |

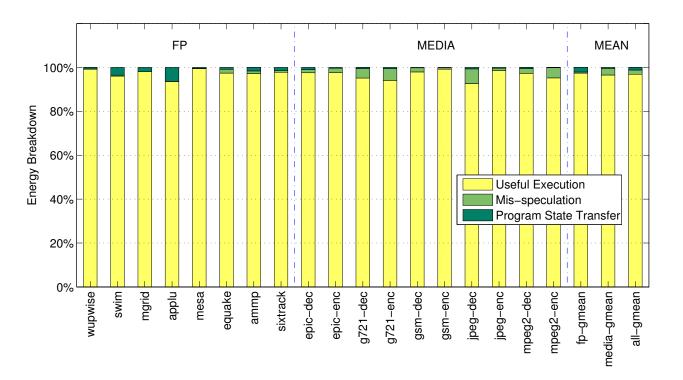

| 7.16 | This figure shows the energy overhead of $\text{Tracy}_{34}^4$ -io2 caused by mis-speculation and       |    |  |

|      | program state transfer. The system is configured to exploit both LLP and ILP. Useful                    |    |  |

|      | execution includes the time spent on both sequential execution and parallel execution                   |    |  |

|      | that is speculated correctly.                                                                           | 99 |  |

|      |                                                                                                         |    |  |

# Chapter 1

# Introduction

As a consequence of the diminishing returns for increasing complexity, microarchitecture designers have started to increase the number of cores on a single chip instead of trying to increase its singlethreaded performance. Computers with four to eight cores are already ubiquitous and trends suggest that core counts will continue to grow for the foreseeable future [1]. While the computational capability of the chip continues to double every 18 months in accordance with Moore's Law, the performance of individual cores has largely stagnated due to limitations on area, power consumption, and heat dissipation.

With the number of cores increasing rapidly but the performance per core increasing slowly at best, software must be parallelized in order to improve performance. Manual parallelization typically yields the best speedups because the programmer can choose new algorithms and data structures that are more amenable to parallelism. However, manual parallelization is often prohibitively timeconsuming and error-prone (especially due to data races and memory-consistency complexities), and some portions of code may simply be too difficult to understand or refactor for parallelization. Code is only parallelized when the return on investment is sufficient.

There has also been considerable research on automatic parallelization. However, most existing automatic parallelization techniques are performed statically (i.e., at compile time) and require source code to be analyzed, suffering three serious problems. First, in many cases, some or all of the source code and development tool chain is lost or, in the case of third-party software, was never available. During the Y2K crisis, it was estimated that some companies were missing as much as 60 percent of their source code [2]. Second, modern applications are assembled and defined at run time, making use of shared libraries, virtual functions, plugins, dynamically-generated code, and other dynamic mechanisms, as well as multiple languages. All these aspects of separate compilation prevent the compiler from obtaining a holistic view of the program, leading to the risk of incompatible parallelization techniques, subtle data races, and resource over-subscription. Third, compile-time analysis has to conservatively respect all control and data dependencies on the control flow graph (CFG). This deters parallelization, because many of these dependencies may not be on the execution path which is actually taken. All the above considerations motivate binary code parallelization at run time, which we call *dynamic binary parallelization (DBP)*. Without effective techniques that can operate on binary code, a large fraction of software will be left behind. And without the ability to parallelize at run time, opportunities for parallelism are curtailed.

### 1.1 Problems of State-of-the-Art DBP

Prior research on DBP has been largely limited. Existing DBP technologies are generally divided into two main categories: parallelizing the raw dynamic instruction stream (DIS) [3, 4, 5] and parallelizing the dynamically-generated CFG [6, 7, 8, 9, 10].

DIS-based techniques use extra hardware to combine multiple cores to work cooperatively as a wider core. Native out-of-order (OoO) execution could also be considered as a DIS-based technique, which has been widely adopted by modern microarchitectures. Focusing on exploiting instruction level parallelism (ILP), this technology has wide applicability, because ILP typically exists through-out the entire program (with different amounts). Limited by branch prediction accuracy and instruction window size, however, this technology generally fails to exploit distant or coarse-grained parallelism, resulting in relatively mediocre speedups.

On the other hand, CFG-based techniques expose a global view of the program and allow discovery of more coarse-grained loop and thread level parallelism (LLP and TLP), which have the potential to produce much larger speedups. However, analysis on the CFG must be conservative and consider the large number of possible paths of program execution, some of which may be rarely executed. This requires the compiler to respect control and data dependencies that do not appear in the actual execution path, inhibiting parallelization and requiring extensive speculation. When source code is not available, this problem is exaggerated due to the lack of high-level information (e.g., types, variables, data structures), which is essential to achieve accurate alias analysis. Furthermore, when coarse-grained parallelism is hard to exploit, CFG-based techniques typically lack the capability to extract fine-grained parallelism instead and just execute the program sequentially. Thus, it is

Figure 1.1: Design spectrum of the representation of program execution on which parallelization is performed. Compared to DIS and complete CFG, Trace has the potential to provide a large instruction window without introducing spurious dependencies.

not surprising that most of the existing CFG-based techniques [6, 7, 10] have failed to parallelize at least half applications in the selected benchmark suite.

Although DIS- and CFG-based techniques are complementary to each other, no prior research has tried to implement both technologies under a unified system. Such a system may achieve large speedups from code regions that contain coarse-grained LLP or TLP, and exploit ILP from the remainder of the program. This combination is quite vital. As Amdahl's Law shows, even a small fraction of non-parallelizable code can drastically inhibit overall speedups. Asymmetric architectures [11, 12] try to address this problem by providing one or more large, OoO cores on the chip for sequential execution modes, and a larger number of simple, in-order (IO) cores to maximize throughput. Due to chip area constraints, however, this organization reduces the number of total cores on the chip, hurting the performance of code regions where plentiful LLP can be exploited. The OoO core may also not be available when needed, if multiple applications are sharing the CPU. Furthermore, when LLP or TLP is limited, there will often be more coarse-grained tasks needing further acceleration via ILP than there are OoO cores. Finally, prior research [3, 4, 5] suggests that cooperative work of multiple IO cores can generally outperform or at least compete with an OoO core, which may obviate the need for an asymmetric architecture in the first place.

Does any representation of program execution provide a large instruction window without introducing spurious dependencies? Figure 1.1 illustrates the design spectrum of the representation of program execution on which parallelization is performed. Theoretically, any point on the design spectrum between the two extremes (DIS and complete CFG) may be the one that achieves the optimal trade-off between code visibility and analysis accuracy. Unlike compile-time parallelization, DBP has the potential to construct *dynamic* CFGs from the instruction stream by only considering execution paths which are actually taken in each particular run. These *partial* CFGs typically represent the execution of smaller code structures (e.g., part of a function instead of the entire function) than *static* CFGs in order to maintain a practical number of unmerged control flows for aggressive parallelization. As the design point shifts to the right on the design spectrum, each dynamic CFG represents the execution of larger code structures and merges more execution paths until the complete whole-program CFG is constucted.

In practice, many programs tend to frequently repeat long sequences of instructions called *hot traces*, which have the potential to provide a generally good trade-off between code visibility and analysis accuracy for a wide variety of applications so as to achieve better parallel performance. First, traces only represent the execution path which is actually taken, eliminating spurious control and data dependencies to the highest possible extent. Second, traces can act as a unified representation of program execution to seamlessly incorporate the exploitation of both coarse- and fine-grained parallelism. For traces that comprise multiple loop iterations, LLP can be exploited with higher priority. By only considering a single execution possibility, many loop-carried dependencies are simply eliminated and more accurate alias analysis can be achieved. As a result, more code regions may contain exploitable LLP, greatly increasing the applicability of existing CFG-based techniques. For the remainder of the program that is less parallelizable, long traces may still expose distant ILP opportunities. The average length of traces is typically much larger than the size of the hardware instruction window used in existing DIS-based techniques.

## 1.2 Challenges of Trace-Based DBP

The major challenge of trace-based DBP is constructing high-quality traces that provide a large instruction window without introducing spurious dependencies. Due to Amdahl's Law, these traces should also cover a large portion of dynamic instructions in order to produce large overall speedups. Another challenge is customizing algorithms that are most suitable to optimize and parallelize binary code in trace format. The following sections will describe these challenges in detail.

#### **1.2.1** Trace Construction and Prediction

Prior research [13] has demonstrated that the return of dynamic binary optimization (DBO) diminishes when traces are longer than 200 basic blocks. For parallelization purposes, however, traces have to be *as long as possible* to expose more distant parallelism opportunities. Furthermore, traces have to be *logically atomic*. They should have a single entry point, a single exit point, and the control flow cannot exit prematurely through so-called *side exits*. Thus, analysis can ignore all unnecessary control and data dependencies, enabling more aggressive parallelization. This atomicity property necessitates speculative execution to recover program state when a trace deviates from the execution path which is actually taken. This is usually easier and less costly than more fine-grained recovery code required to support side exits. Finally, traces of different program phases should all meet the above two requirements so that the program can run in parallel most of the time.

The dilemma, however, is that the longer a trace is, the more difficult to achieve high speculation accuracy. To the best of our knowledge, most existing technologies do not support the atomicity property of traces [14, 15, 16, 17, 18, 19, 20]. rePlay [21] does perform DBO on short atomic traces (16 to 256 instructions long), but they are not suitable for parallelization purposes. Before the many-core era, some systems were proposed [22, 23, 24, 25] to use hardware-only technologies to speculate multiple consecutive atomic traces and execute them simultaneously on different functional units. In order to achieve reasonable speculation accuracy, however, these systems construct very short traces, which necessitates ultra-low communication latency to support program state transfer. Furthermore, these systems rely on fine-grained selective recovery from frequent mis-speculation. While suitable for simultaneous-multithreaded or clustered microarchitectures, neither requirement can be easily satisfied on many-core architectures.

### 1.2.2 Trace Optimization and Parallelization

Accurate alias analysis is usually the key factor to enable effective program optimization and parallelization. Lacking high-level information (e.g., types, variables, data structures), it is extremely difficult to disambiguate memory references when source code is not available. Thus, most existing software dynamic translation (SDT) systems, such as Dynamo [14], DynamoRio [15], Transmeta [26], and Daisy [27], only perform alias analysis in the form of *instruction inspection*, which disambiguates two memory references if they access either different memory regions or their addresses have the same base register and different offsets. As demonstrated in prior research [28], instruction inspection can only disambiguate one-third of all memory references in SPEC CUP2000 integer benchmarks, greatly restricting aggressive code transformations.

Compilers typically rely on various data-flow analyses [29] to optimize programs. They set up data-flow equations for each node of the CFG and solve them by repeatedly calculating the output from the input locally at each node until the entire system stabilizes, i.e., it reaches a fixpoint. In order to handle the large number of execution paths represented by the CFG, diverged program states

are consertively merged at certain joint points. Furthermore, the name space of data-flow functions is typically based on lexical names of variables, leaving many optimization opportunities behind. Some frameworks [30, 31] have been developed to achieve scalable path-based value-flow analysis, but all of them are targeted to bug detection instead of code transformations. On the contrary, an atomic trace not only represents a single execution path, but also has no side exits so that all control dependencies and derived data dependencies among its instructions can be ignored. Thus, it is both important and necessary to design heavyweight but powerful optimization algorithms to fully exploit the atomicity property of traces, which has never been studied by existing optimization systems that also leverage atomic traces [21, 32].

Due to limited trace length, existing trace-based parallelization systems [33, 34] only focus on exploiting local ILP. However, prior research [35] has demonstrated that there is no dominant type of parallelism. The contribution of each type of parallelism varies widely across the applications. Thus, one major prerequisite to achieve the greatest speedups is to accurately identify the most appropriate type of parallelism that should be exploited in each code region. Parallelization at the trace level further increases the difficulty of exploiting hybrid parallelism. For the same code region that has complicated control flows, different traces may have quite different characteristics, which need customized parallelization algorithms to meet the specific requirements.

### 1.3 Research Overview

This dissertation explores the novel idea of trace-based DBP, which provides a large instruction window without introducing spurious dependencies. We hypothesize that traces provide a generally good trade-off between code visibility and analysis accuracy for a wide variety of applications so as to achieve better parallel performance. Compared to DIS-based DBP, trace-based DBP can exploit more distant parallelism because the average length of traces is typically much larger than the size of the hardware instruction window. Compared to CFG-based DBP, trace-based DBP does not need to respect control and data dependencies that are not on the execution path which is actually taken. More importantly, while DIS-based DBP typically only exploits fine-grained parallelism and CFG-based DBP typically only exploits coarse-grained parallelism, traces can be used as a unified representation of program execution to seamlessly incorporate the exploitation of both coarse- and fine-grained parallelism.

Before developing any specific design of trace-based DBP, we first conduct a limit study to: 1) identify the performance limits of trace-based DBP, and 2) explain *why* trace-based DBP has that performance. The first goal is to set up the performance upper bound so that any following specific design can be judged to determine whether it has fully exploited the benefits of trace-based DBP. The second goal is to identify the unique and powerful characteristics of trace-based DBP that enable it to achieve substantial speedups. We highlight these characteristics by comparing trace-based DBP to static parallelization which is typically performed by the compiler.

We analyze the performance limits of trace-based DBP by making three idealizations about the hardware and algorithms: 1) the program runs on a many-core architecture with an unbounded number of cores and an unlimited, shared L1 cache, 2) the trace construction algorithm can always identify the most frequently repeating patterns of instructions that will occur in a particular run of the program, and 3) when the program reaches a repeating trace, the trace prediction algorithm can always correctly predict the trace that is about to run.

The limit study performs a five step process for each benchmark: 1) record the complete execution sequence of the program, 2) analyze the recording offline to identify the frequently repeating traces, 3) create a new execution sequence by replacing each trace in the original execution sequence with the parallelized version, 4) analyze the parallel execution time of the new execution sequence using a model of a shared-memory many-core architecture, and 5) replay a linearization of the new execution sequence on a real machine and check the correctness of the result.

We then develop Tracy, an innovative DBP framework which monitors a program at run time and dynamically identifies hot traces, parallelizes them, and caches them for later use so that the program can run in parallel every time a hot trace repeats. In order to achieve the greatest speedups over sequential execution, Tracy has to construct high quality traces as well as to customize the most suitable algorithms to optimize and parallelize these traces.

High quality traces have to simultaneously satisfy four requirements, which can be contrary to one another. First, traces have to be as long as possible to expose more distant parallelism opportunities. Second, traces have to be logically atomic. They should have a single entry point, a single exit point, and the control flow cannot exit prematurely through side exits. Thus, analysis can ignore all unnecessary control and data dependencies, enabling more aggressive parallelization. Third, traces have to be predicted accurately so that valuable CPU cycles and energy are not wasted on executing incorrect execution paths. Fourth, traces have to cover a large portion of dynamic instructions so as to produce large overall speedups.

Based on the above insights, we exploit the unique power of many-core architectures by launching multiple traces and executing them simultaneously on idle cores. The major insight is that in many cases, speculation accuracy can be *dramatically* increased by only trying a *very small* number of candidate traces. We also develop an innovatative trace construction algorithm that holistically balances among trace length, speculation accuracy, and coverage of dynamic instructions. Tracy constructs the longest traces that can be accurately speculated on the available number of cores. In certain code regions that have complicated control flows, Tracy stops constructing traces and executes these code regions sequentially. More specifically, we leverage the hierarchical code structures (e.g., functions, loops, basic blocks) to define the starting and ending points of each trace. In order to maximize their length, traces are initially restricted to start and end at the outermost functions or loops. During program execution, if a code structure shows unpredictable internal execution paths, it is abandoned and the next level of inner code structures is used instead. If the innermost code structure still has complicated control flows that are hard to predict, the corresponding code regions are executed sequentially.

We develop two major optimizations to optimize traces that have been constructed, namely *symbolic evaluation* and *memory disambiguation*. The functionality of these optimizations is not only to directly produce speedups, but more importantly, to prepare the code for future parallelization. Thus, the performed code transformations may be suboptimal for increasing the program performance by themselves, but they reformat the code to be more amenable to parallelism. Furthermore, these optimizations are designed to fully exploit the atomicity property of traces, within the confines of the underlying architectural support.

Symbolic evaluation assigns a symbolic value to each defined register or memory location. Code analysis and transformations are then performed through symbolically executing each program path and updating these values. The path sensitivity characteristic of symbolic evaluation is not scalable, and thus has not been used by the compiler that needs to optimize the entire CFG. However, because symbolic evaluation performs path-sensitive program analysis and data-flow information is based on symbolic values instead of lexical names, it performs more precise program analysis than traditional data-flow analysis [29]. For memory disambiguation, we divide all memory references into groups with different base registers. If the ranges of addresses covered by two groups are *disjoint*, memory references in one group are guaranteed not to alias with those in the other group. Disambiguating memory references at the group granularity is necessary because the sequential order of all memory references is lost after parallelization, which, however, may introduce false positives due to the approximation of memory addresses.

Our goal is not to develop totally innovative parallelization algorithms, but to customize off-theshelf algorithms to make them suitable for parallelizing atomic traces. For exploiting ILP, Tracy adopts the traditional list scheduling algorithm [36] to partition and schedule instructions among different cores. Unlike the original algorithm that only reorders instructions on the same core, we have to minimize inter-core synchronization overhead as well as cache coherence traffic on the many-core architecture. For exploiting LLP, Tracy performs two major code transformations, *accumulator expansion* and *dependent code motion*, to eliminate loop-carried dependencies or at least to increase the execution overlap of multiple threads so as to achieve better parallel performance.

We also leverage traces as the unified representation of program execution to exploit both coarseand fine-grained parallelism. This combination is quite vital. As Amdahl's Law shows, even a small fraction of non-parallelizable code can drastically inhibit overall speedups. When both types of parallelism are available, Tracy selects the optimal strategy at the trace level. It first parallelizes the trace by exploiting LLP, which has the potential to produce larger speedups. If limited LLP exists, however, Tracy extracts ILP from the trace instead.

### 1.4 Contributions of the Dissertation

The contributions of the dissertation are listed as follows:

- A limit study that not only identifies the performance limits of trace-based DBP, but also explains *why* trace-based DBP performs as it does. It sets up the performance upper bound so that any following specific design can be judged to determine whether it has fully exploited the benefits of trace-based DBP. It also identifies the unique and powerful characteristics of trace-based DBP that enable it to achieve substantial speedups.

- A capture-replay framework that efficiently records program execution and replays the recording by capturing non-deterministic events such as interrupts, preemption, and user input. The framework is unique in that the user can modify the execution sequence and replay the modified version to verify that it is equivalent to the original execution, which will be widely applicable to future studies on dynamic trace-based systems.

- An innovative trace-based DBP framework named Tracy which provides a large instruction window without introducing spurious dependencies. Compared to DIS-based DBP, it can exploit more distant parallelism and compared to CFG-based DBP, it only needs to respect control and data dependencies on the execution path which is actually taken.

- A general trace construction algorithm that holistically balances among trace length, speculation accuracy, and coverage of dynamic instructions. This algorithm constructs the longest

traces that can be accurately speculated on the available number of cores and can be readily adopted by other dynamic trace-based systems.

- Two code optimizations, symbolic evaluation and memory disambiguation, that are specifically designed for atomic traces. They not only directly produce speedups, but also transform the code to be more amenable to parallelism, which is usually more important.

- A unified parallelization system that uses customized algorithms to extract both coarse- and fine-grained parallelism from atomic tracs and selects the optimal strategy based on the estimated parallel performance.

### 1.5 Organization of the Dissertation

The remainder of the dissertation is organized as follows. Chapter 2 provides background on the evolution of traces and different parallelization technologies to facilitate understanding of the subsequent chapters. Chapter 3 discusses a limit study to prove the feasibility trace-based DBP and Chapter 4 then presents Tracy, an innovative trace-based DBP framework which leverages multi-trace execution to exploit the unique power of many-core architectures. After that, Chapters 5 to 7 describe trace construction and prediction, trace optimization, and trace parallelization, respectively, which are the three most important functionalities of Tracy. Finally, Chapter 8 concludes the dissertation and discusses future work.

## Chapter 2

# **Background and Related Work**

Two key concepts of this dissertation are *trace* and *parallelization*. Thus, we organize the background chapter based on these two concepts. Under the trace concept, we first describe its evolution during the last three decades and then discuss how traces are typically constructed during run time using SDT systems. Under the parallelization concept, we discuss both manual parallelization and automatic parallelization. Automatic parallelization is further divided into four categories, each of which is described in detail.

### 2.1 Evolution of Traces

Traces have long been used to improve program performance. While VLIW and superscalar processors need sufficient ILP to effectively utilize the parallel hardware, ILP within basic blocks is limited for control-intensive programs. Thus, optimizations across basic block boundaries are needed. Based on profiling information, the initial traces are constructed by the compiler, which removes constraints due to unimportant execution paths and links basic blocks together following the most frequently executing path. These traces contain both side entrances and side exits, where the control flow can enter and exit the trace arbitrarily. For several different architectures, trace scheduling [37, 38] has been proposed to exploit more ILP by performing code motion on these long sequences of instructions. However, the existing side entrances require very complex bookkeeping information to schedule instructions across basic block boundaries, if at all possible.

In order to remove the problems of side entrances, tail duplication has been proposed to ensure that the control flow can only enter from the top of the trace. More specifically, a copy is made of the tail portion of the trace from the first side entrance to the end, and all side entrances are moved to the corresponding duplicated basic blocks. Such reformatted traces with a single entry and multiple exits are called superblocks [16, 39]. Superblocks are not only constructed by the compiler based on profiling information, but are also leveraged by a variety of modern microarchitectures and SDT systems at run time. For example, the trace cache [40] increases instruction fetch width by caching dynamic instruction sequences; the trace processor [25] speeds up control prediction by speculating on traces instead of branches; DBO systems [14, 15, 18, 20, 21] exploit optimization opportunities on traces which are not available by statically analyzing the CFG.

Although superblocks do not have side entrances, the side exits still prevent instructions from being freely scheduled across basic block boundaries. For example, an instruction cannot be moved above a preceding side exit if it is used before it is redefined when the side exit is taken. Thus, prior research [21, 32] has introduced atomic traces, which have a single entry point and a single exit point. Furthermore, these reformatted traces encapsulate only a single flow of control. If any instruction within the trace executes, all instructions within the trace execute. This atomicity property provides more flexibility for performing beneficial code transformations than if the traces were not atomic. Instructions within the trace are not control dependent on one another and can be moved freely within the confines of data dependencies.

Another enhancement of superblocks is called hyperblocks [17, 19], which represent multiple execution paths simultaneously. Instructions from different execution paths are guarded by hardwaresupported predicates to maintain the correct control flow at run time. The motivation behind hyperblocks is to group many basic blocks from different execution paths into a single manageable code region for compiler optimization. Thus, for programs without heavily biased branches, hyperblocks provide a more flexible framework for compile-time code transformations. However, hyperblocks also contain side exits and thus do not have the atomicity property.

### 2.2 Software Dynamic Translation

As described above, traces are initially constructed by the compiler based on profiling information. Recently, however, SDT systems become increasingly popular to extract traces directly from the instruction stream while the program is running. Figure 2.1 illustrates how an SDT system is positioned under the application to intercept the native instruction stream at run time. Three algorithmic components form the foundation of a generic SDT implementation: 1) the *translator* translates instructions from the binary executable into traces that will run on the actual hardware, often interjecting or altering instructions en route, 2) the *code cache* holds these commonly executed

#### 2.2 | Software Dynamic Translation

Figure 2.1: Generic SDT systems contain three algorithmic components and transparently manipulate the binary executable while it is running.

traces so that they can be executed again without re-translation, and 3) the *dispatcher* redirects the control flow to either the next trace, if it is already in the trace cache, or to the translator which re-translates the target address. In the mean time, the original program either continues running without being translated or is suspended until the new trace is completed.

SDT systems have been implemented purely in software and executed on commodity microarchitectures for diverse purposes, such as optimization [14, 15], ISA translation [27], profiling [41, 42], or security monitoring [43, 44]. Due to the large overhead of software-based dynamic instrumentation [41, 42], however, most systems [27, 41, 42, 43, 44] do not profile the running program and terminate the trace at any conditional branch or jump that has multiple targets. Other systems [14, 15] use the next executed tail (NET) algorithm to construct superblocks, which only needs very lightweight instrumentation. The NET algorithm has two phases, the profiling phase and the collection phase. In the profiling phase, each conditional branch that is a backedge is instrumented. A counter is maintained for each of these backedges and incremented every time that backedge is taken. When this counter hits a predetermined threshold, the next superblock is collected. In the collection phase, the code is instrumented and monitored basic block by basic block until another backedge is encountered. The NET algorithm has two significant shortcommings: 1) it is possible to collect a cold path during the collection phase even if a hot path was primarily responsible for reaching the backedge during the profiling phase, and 2) the constructed hyperblocks cannot span any function invocations/returns and loops, and thus are typically only two to three basic blocks long. Prior research [45] has further demonstrated that for the SPEC CPU2006 benchmark suite, the superblocks constructed by the NET algorithm only account for less than 40% of dynamic instructions and for more than 80% of the times, the control flow leaves the running superblock prematurely via its side exits.

In order to improve trace quality with low runtime overhead, prior research [25, 40] has proposed to implement dynamic instrumentation in hardware by directly integrating trace construction with non-critical stages of instruction pipeline execution. This technology has been adopted by a variety of DBO systems [18, 20, 21], for which increasing program speed is the top priority. For example, both [18] and [20] profile the behavior (i.e., execution frequency and target bias) of every conditional branch, which would cause prohibitive runtime overhead if using software-based dynamic instrumentation. Highly biased hot branches are then identified and analyzed to generate those dominant execution paths. As reported by [18], 12% of the constructed hyperblocks are more than 50 instructions long and 89% of them cover at least 100 million dynamic instructions during program execution. rePlay [21, 46] takes a further step by associating each conditional branch with the global branch history [47]. This context sensitive information separates each conditional branch into instances based on the execution path leading up to itself. Once separated this way, a greater number of conditional branches tend to exhibit biased behavior. For integer applications in the SPEC CPU2000 benchmark suite, rePlay is capable of constructing atomic traces of 102 instructions on average, which results in optimization effectiveness [13].

### 2.3 Manual Parallelization

With the number of cores increasing rapidly but the performance per core increasing slowly at best, software must be parallelized in order to improve performance. A variety of parallel programming frameworks such as OpenMP [48], Chapel [49], and Axum [50] have been proposed to help software engineers fully exploit this increased processing power by executing threads on multiple cores simultaneously. Based on these frameworks, specific parallel libraries [51, 52] have also been proposed to facilitate efficient software development in different domains. Such manual parallelization typically yields the best speedups because the programmer can choose new algorithms and data structures that are more amenable to parallelism.

For a variety of reasons, however, many programs will not be completely parallelized and will continue to have both parallel and sequential modes of execution. Software engineers may not have the source code for some or all parts of the program because it was lost or because it uses third-party libraries. Furthermore, manual parallelization is often prohibitively time-consuming and error-prone,