# Mitigating Resource Contention in Warehouse Scale Computers

A Dissertation

Presented to

In Partial Fulfillment

of the requirements for the Degree

Doctor of Philosophy

Computer Science

by

Lingjia Tang

May 2012

### Approvals

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

| Lingjia Tar              | ng                     |

|--------------------------|------------------------|

| Approved                 | ;                      |

| Mary Lou Soffa (Advisor) | Westley Weimer (Chair) |

| Jack Davidson            | Kamin Whitehouse       |

| <u></u>                  |                        |

Joanne Bechta Dugan

Accepted by the School of Engineering and Applied Science:

Dean, School of Engineering and Applied Science

### **Abstract**

The class of modern datacenters hosting large-scale Internet services such as web-search, mail, and social networking has gained significant momentum in today's computing environments. However, these datacenters, recently coined as warehouse scale computers (WSCs), are extremely expensive to construct and operate. Improving software performance and server utilization is key to improving the efficiency and reducing the enormous cost in WSCs.

Modern WSCs are constructed using commodity multicore processors, on which part of the memory subsystem is shared. When multiple applications are co-located on a multicore machine, contention for the shared memory resources, such as caches and memory bandwidth, may occur. This contention can cause severe cross-core performance interference, and significantly degrade application performance. Mitigating resource contention is critical for improving application performance. However, despite the wealth of research effort on contention management, little is known about how emerging large-scale web-service applications interact with the shared memory resources on commodity processors, and how this contention can be mitigated to improve the performance of these applications.

In addition to performance, mitigating contention is also critical for improving the server utilization in WSCs. As multicore processors with expanding core counts continue to dominate the server market, the overall utilization of WSCs depends heavily on the consolidation of workloads to take advantage of the total computing potential provided by modern processors. However, many of the applications running in WSCs are user-facing, latency-sensitive applications with quality of service (QoS) requirements. These QoS requirements can be violated by the performance interference that can occur when multiple applications are consolidated on a single machine. As a result, the current common practice in WSCs is to disallow the co-location of latency-sensitive applications with other applications. This approach is undesirable as it results in low machine utilization in WSCs and millions of dollars wasted.

This dissertation presents novel compilation and runtime approaches to significantly mitigating contention and improving performance, QoS and machine utilization in datacenters. Specifically, the main contributions of this dissertation include: 1) comprehensive investigation and characterization of the impact of memory resource sharing on industry-strength large-scale datacenter workloads, which expose new characteristics and insights contrary to recent literature; 2) the design of a heuristic based system and a runtime system to intelligently map application threads to cores to promote positive resource sharing and mitigate resource contention to improve application performance; and 3) the design of novel compilation techniques and runtime systems that statically and dynamically manipulate applications' contentious nature to enable the co-location of applications with varying QoS requirements, and as a result, greatly improve server utilization in WSCs.

# ${\bf Acknowledgements}$

To Jason Mars.

To Dr. Soffa.

To Google folks.

To committee members.

To fellow graduate students.

To my parents.

| 1 | Int | troduction 1                           |                                                        |    |

|---|-----|----------------------------------------|--------------------------------------------------------|----|

|   | 1.1 | Memory Resource Sharing and Contention |                                                        | 2  |

|   | 1.2 | Implic                                 | ations of Memory Resource Contention                   | 3  |

|   |     | 1.2.1                                  | The Impact of Contention on Performance                | 4  |

|   |     | 1.2.2                                  | The Impact of Contention on Server Utilization         | 4  |

|   |     | 1.2.3                                  | Trade-offs Between Performance and Utilization         | 5  |

|   | 1.3 | Mitiga                                 | ating Contention                                       | 6  |

|   | 1.4 | Two S                                  | trategies for Mitigating Contention                    | 7  |

|   |     | 1.4.1                                  | Mitigating Contention to Improve Performance           | 8  |

|   |     | 1.4.2                                  | Mitigating Contention to Improve Utilization           | 10 |

|   | 1.5 | Summ                                   | ary of Contributions                                   | 12 |

| 2 | Ba  | ckgrou                                 | and and Related Work                                   | 16 |

|   | 2.1 | Wareh                                  | nouse Scale Computers                                  | 16 |

|   |     | 2.1.1                                  | Cost                                                   | 17 |

|   |     | 2.1.2                                  | Application QoS                                        | 17 |

|   |     | 2.1.3                                  | Job Scheduling, Application Colocation and Utilization | 18 |

|   |     | 2.1.4                                  | Machine Level                                          | 21 |

|   | 2.2 | Relate                                 | d Work                                                 | 22 |

|   |     | 2.2.1                                  | Impact of Memory Resource Sharing                      | 22 |

|   |     | 2.2.2                                  | Novel Hardware Solutions to Mitigate Contention        | 22 |

|   |                        | 2.2.3         | Software Runtime and OS Approaches to Mitigating |            |

|---|------------------------|---------------|--------------------------------------------------|------------|

|   |                        |               | Contention                                       | 23         |

|   |                        | 2.2.4         | Cache Contention Aware Compilation               | 25         |

| 3 | $\mathbf{Th}$          | e Imp         | act of Memory Resource Sharing                   | 27         |

|   | 3.1                    | Memo          | ory Resource Sharing                             | 28         |

|   | 3.2                    | Intra-        | Application Sharing                              | 29         |

|   |                        | 3.2.1         | Experiment Methodology                           | 30         |

|   |                        | 3.2.2         | Measurement and Findings                         | 32         |

|   |                        | 3.2.3         | Investigating Performance Variability            | 36         |

|   |                        | 3.2.4         | Summary                                          | 38         |

|   | 3.3                    | Inter-        | Application Sharing                              | 38         |

|   |                        | 3.3.1         | Experiment Design                                | 39         |

|   |                        | 3.3.2         | Measurement and Findings                         | 39         |

|   |                        | 3.3.3         | Varying Thread Count and Architecture            | 44         |

|   |                        | 3.3.4         | Summary                                          | 48         |

| 4 | $\mathbf{T}\mathbf{h}$ | $ m_{read-t}$ | o-core Mapping                                   | 49         |

|   | 4.1                    | A Het         | uristic Approach to TTC Mapping                  | 50         |

|   |                        | 4.1.1         | Evaluating the Heuristics                        | 55         |

|   | 4.2                    | An Ao         | daptive Approach to TTC Mapping                  | 56         |

|   |                        | 4.2.1         | Evaluating AToM                                  | 57         |

| 5 | Co                     | mpilin        | ng for Niceness                                  | <b>5</b> 9 |

|   | 5.1                    | QoS-C         | Compile Overview                                 | 61         |

|   | 5.2                    | Identi        | fy Contentious Code Regions                      | 63         |

|   |                        | 5.2.1         | Contentiousness and Sensitivity                  | 64         |

|   |                        | 5.2.2         | Identify Contentious Regions                     | 70         |

|   | 5.3                    | Comp          | iler Transformations for Rate Reduction          | 74         |

|   |     | 5.3.1  | Padding                                                    |

|---|-----|--------|------------------------------------------------------------|

|   |     | 5.3.2  | Nap Insertion                                              |

|   |     | 5.3.3  | Understanding Cooldown and Warmup 78                       |

|   | 5.4 | Evalua | ation                                                      |

|   |     | 5.4.1  | Setup and Methodology                                      |

|   |     | 5.4.2  | Model for Code Region Identification 80                    |

|   |     | 5.4.3  | Compiler Transformations                                   |

|   |     | 5.4.4  | QoS-Compile: Put it All Together                           |

|   |     | 5.4.5  | Google Applications                                        |

|   | 5.5 | Summ   | nary                                                       |

| 6 | Re  | active | Niceness 97                                                |

|   | 6.1 | React  | ive-Niceness Overview                                      |

|   | 6.2 | RN-C   | ompile: Compiling for Reactive Niceness 102                |

|   | 6.3 | RN-R   | untime: Dynamic Detection and Reaction to QoS              |

|   |     | Degra  | dation                                                     |

|   |     | 6.3.1  | Runtime                                                    |

|   |     | 6.3.2  | Detection and Reaction                                     |

|   | 6.4 | Evalua | ation                                                      |

|   |     | 6.4.1  | Setup and Methodology                                      |

|   |     | 6.4.2  | Effectiveness of Reactive-Niceness: Simple Heuristic . 112 |

|   |     | 6.4.3  | Effectiveness of Reactive-Niceness: Targeted Heuristic 115 |

|   |     | 6.4.4  | Effectiveness of Reactive-Niceness: Phase Level Be-        |

|   |     |        | havior                                                     |

|   |     | 6.4.5  | Overhead                                                   |

|   |     | 6.4.6  | Energy Efficiency of using Reactive-Niceness 122           |

|   |     | 6.4.7  | Varying Architecture                                       |

|   | 6.5 | Summ   | nary 125                                                   |

| 7 | Conclusions and Future Directions |        | 127                                                 |       |

|---|-----------------------------------|--------|-----------------------------------------------------|-------|

|   | 7.1                               | Summ   | ary of Themes and Results                           | . 128 |

|   | 7.2                               | Future | e Direction                                         | . 130 |

|   |                                   | 7.2.1  | Managed Runtime for QoS and utilization in WSCs .   | . 131 |

|   |                                   | 7.2.2  | Runtime systems and research infrastructure for WSC | s 131 |

| Topology of a Dual Socket Intel Clovertown                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current Two Options in WSCs. Option A, disallowing colo-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| cation of applications, achieves peak application performance |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| at the sacrifice of machine utilization. Option B improves    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| machine utilization and reduces the number of server ma-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| chines needed. However, applications may suffer significant   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| performance degradation, which can impair latency-sensitive   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| applications' capability to deliver acceptable QoS            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Dissertation Overview - Understanding the impact of con-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tention and 2 strategies to mitigate contention to improve    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| performance and utilization                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Enabled capabilities by our software systems. (A) illustrates |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| the strategy 1, the TTC mapper's effect - improved perfor-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mance comparing to baseline colocation situation, shown in    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 1.2. (B) illustrates the strategy 2, Static/Dynamic    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Compilation for Niceness's effect. Strategy 2 improves the    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| QoS of the high priority application to meet its QoS require- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ment. By doing so, strategy 2 turns previous forbidden colo-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| cations into "safe" colocations and thus improves the server  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| utilization, comparing to the baseline of disallowing coloca- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tion shown in Figure 1.2                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                               | Current Two Options in WSCs. Option A, disallowing colocation of applications, achieves peak application performance at the sacrifice of machine utilization. Option B improves machine utilization and reduces the number of server machines needed. However, applications may suffer significant performance degradation, which can impair latency-sensitive applications' capability to deliver acceptable QoS Dissertation Overview - Understanding the impact of contention and 2 strategies to mitigate contention to improve performance and utilization |

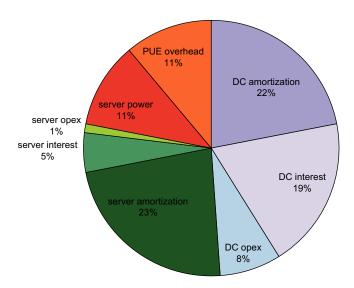

| 2.1  | 1CO (1otal Cost of Ownership) cost breakdown for a data-         |    |

|------|------------------------------------------------------------------|----|

|      | center using commodity servers                                   | 18 |

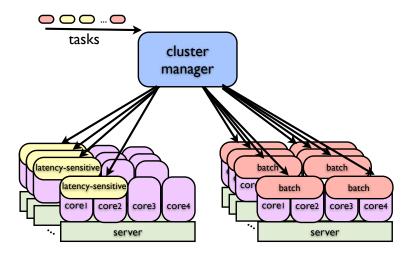

| 2.2  | Task placement in a cluster. The cluster manager does not        |    |

|      | co-locate latency-sensitive applications with others to protect  |    |

|      | their QoS from performance interference, causing low machine     |    |

|      | utilization                                                      | 19 |

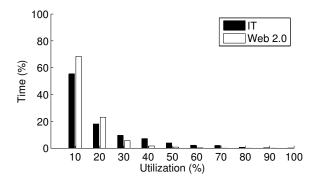

| 2.3  | Server Utilization Histogram from HP datacenters                 | 20 |

| 2.4  | Activity profile of a sample of 5,000 Google servers over a      |    |

|      | period of 6 months                                               | 21 |

| 3.1  | Sharing Cache, Separate FSBs (XXXX)                              | 30 |

| 3.2  | Sharing Cache, Sharing FSB (XXXX)                                | 30 |

| 3.3  | Separate Caches, Separate FSBs (X.X.X.)                          | 30 |

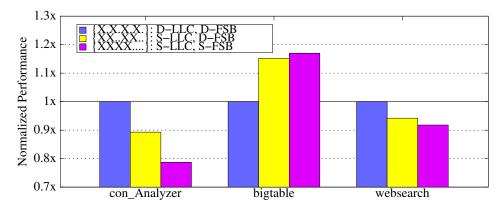

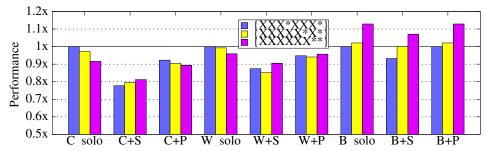

| 3.4  | Performance of different thread-to-core mappings when each       |    |

|      | application is running alone. The higher the bars, the better    |    |

|      | performance. The performance variability is up to $20\%$ for     |    |

|      | each application, indicating that the memory resource sharing    |    |

|      | has a significant performance impact on these applications.      |    |

|      | Also, notice that bigtable is benefiting from sharing last level |    |

|      | cache; while $contentAnalyzer$ and $webSearch$ suffer from the   |    |

|      | contention for memory resource among sibling threads             | 33 |

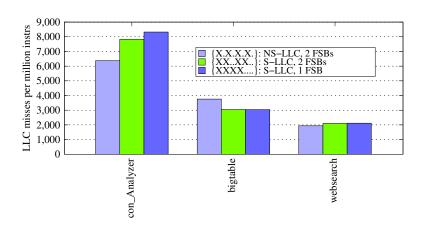

| 3.5  | LLC misses per million instrs                                    | 34 |

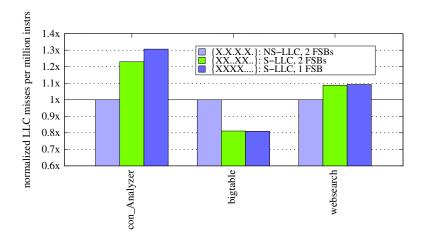

| 3.6  | Normalized average LLC misses per million instructions           | 34 |

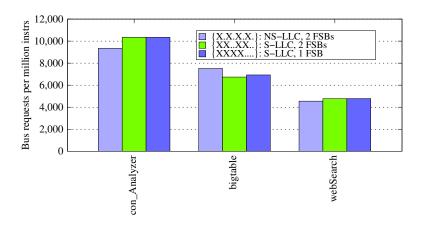

| 3.7  | Bus ratio                                                        | 35 |

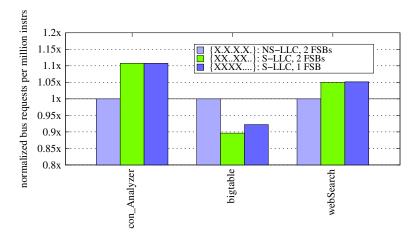

| 3.8  | Normalized bus ratio                                             | 35 |

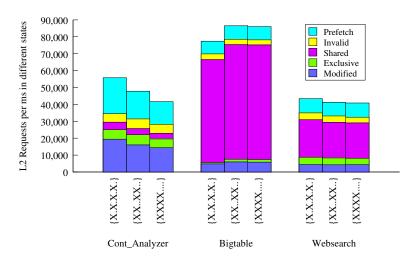

| 3.9  | L2 Requests in MESI States and in Prefetch State                 | 36 |

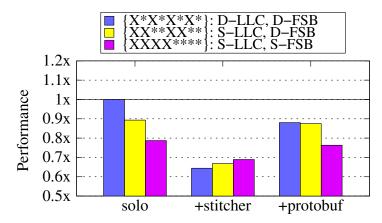

| 3.10 | ContentAnalyzer. Normalized to solo performance                  | 40 |

| 3.11 | Websearch. Normalized to solo performance                        | 40 |

| 3.12 | Bigtable. Normalized to solo performance                                                    | 40 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.13 | ContentAnalyzer. Normalized to solo performance with                                        |    |

|      | {X.X.X.}                                                                                    | 41 |

| 3.14 | Websearch. Normalized to solo performance with $\{X.X.X.X.\}$                               | 41 |

| 3.15 | Big<br>table. Normalized to solo performance with $\{{\tt X.X.X.X.}\}$ .                    | 41 |

| 3.16 | Topology of Dual Socket Intel Westmere                                                      | 44 |

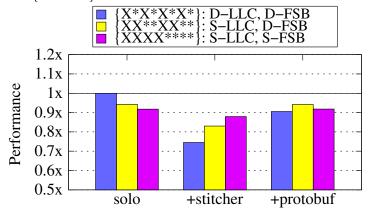

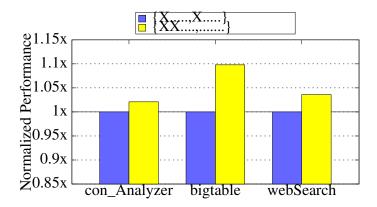

| 3.17 | 2 threads of a latency sensitive application colocated with                                 |    |

|      | 6 threads of a batch application, normalized to the latency                                 |    |

|      | sensitive application's solo performance in $\{\mathtt{X} \dots \mathtt{X} \dots\}$ mapping | 45 |

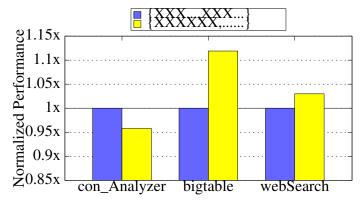

| 3.18 | 6 threads of a latency sensitive application colocated with 2                               |    |

|      | threads of a batch application, normalized to the latency sen-                              |    |

|      | sitive application's solo performance in $\{\texttt{XXX.,XXX.}\}$ mapping                   | 45 |

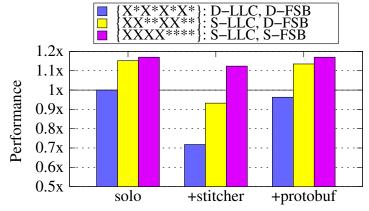

| 3.19 | 2 threads of latency sensitive applications running alone on                                |    |

|      | Westmere                                                                                    | 47 |

| 3.20 | 6 threads of latency sensitive applications running alone on                                |    |

|      | Westmere                                                                                    | 47 |

| 3.21 | 6 threads of latency sensitive applications co-running with 6                               |    |

|      | threads of batch applications on Westmere;                                                  | 47 |

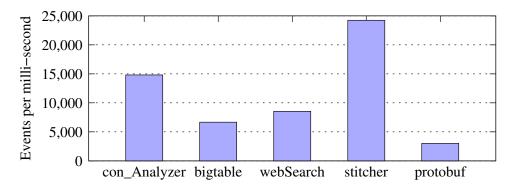

| 4.1  | Bus Burst Transactions (full cache line) per millisecond per                                |    |

|      | one thread                                                                                  | 52 |

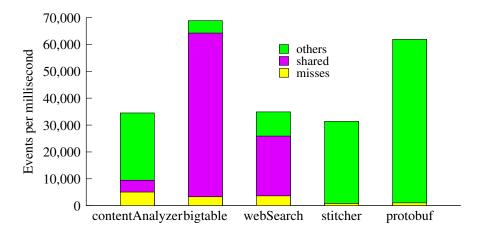

| 4.2  | LLC misses/ms, LLC_requests_Share/ms and LLC reference/ms                                   |    |

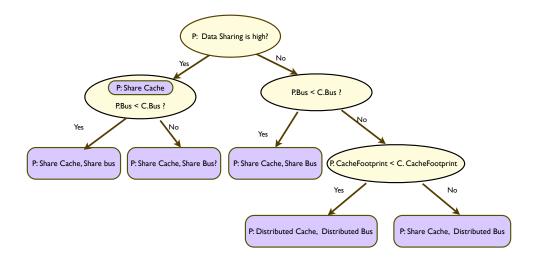

| 4.3  | Decision Tree                                                                               | 55 |

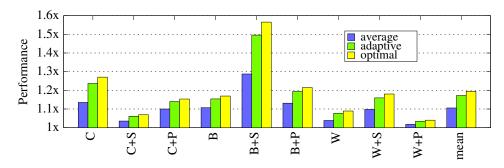

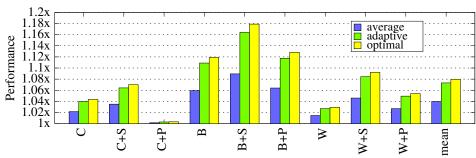

| 4.4  | Adaptive Thread-To-Core Mapping on Clovertown                                               | 58 |

| 4.5  | Adaptive Thread-To-Core Mapping on Westmere                                                 | 58 |

|      |                                                                                             |    |

| 5.1  | QoS-Compile Overview                                                                        | 61 |

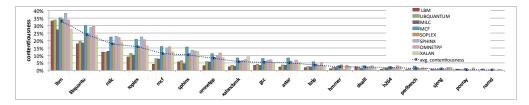

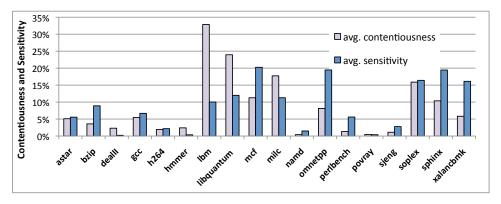

| 5.2  | Contentiousness. Each bar shows the performance degrada-                                    |    |

|      | tion of a corunner caused by the application across x-axis                                  | 66 |

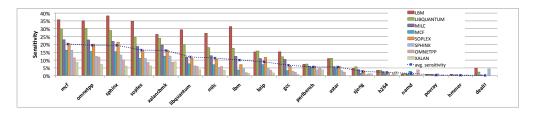

| 5.3  | Sensitivity. Each bar shows the performance degradation of      |    |

|------|-----------------------------------------------------------------|----|

|      | the application across x-axis caused by each of the 8 different |    |

|      | corunners                                                       | 66 |

| 5.4  | Average Contentiousness vs. Sensitivity                         | 68 |

| 5.5  | PMUs used for predicting contentiousness                        | 72 |

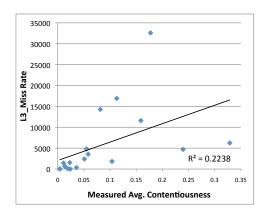

| 5.6  | L3 Miss Rate is not strongly correlated with the real measured  |    |

|      | contentiousness                                                 | 80 |

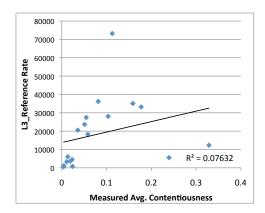

| 5.7  | L3 Reference rate is not strongly correlated with the real mea- |    |

|      | sured contentiousness                                           | 80 |

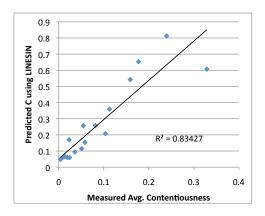

| 5.8  | Predicted contention score using our model is highly corre-     |    |

|      | lated with the real measured contentiousness for SPEC bench-    |    |

|      | marks                                                           | 81 |

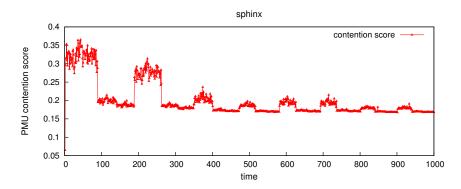

| 5.9  | Sphinx's PMU contention score calculated using our predic-      |    |

|      | tion model                                                      | 83 |

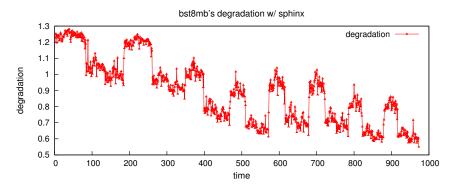

| 5.10 | Bst8mb's degradation when running with sphinx. The higher,      |    |

|      | the more degradation. Figure 7 trends similarly with this       |    |

|      | figure, indicating the profiler is identifying the correct con- |    |

|      | tentious code regions.                                          | 83 |

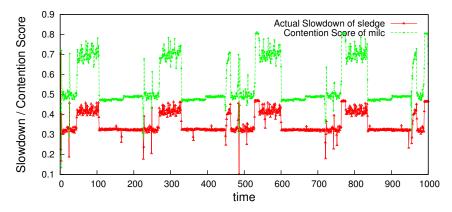

| 5.11 | This graph shows the accuracy of the contention score given     |    |

|      | by our prediction model in predicting the contentiousness of    |    |

|      | milc.                                                           | 83 |

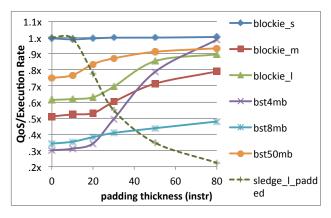

| 5.12 | Padding sledge_l's effect on its co-runner blockie and bst.     |    |

|      | As padding thickness increases, sledge_l's execution rate de-   |    |

|      | ceases, blockie and bst's QoS improves. The padding gran-       |    |

|      | ularity is every 5 instructions                                 | 85 |

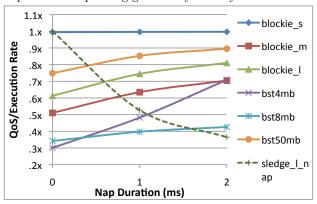

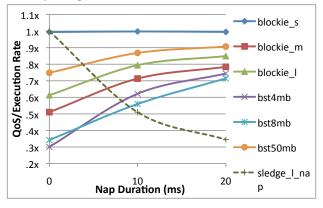

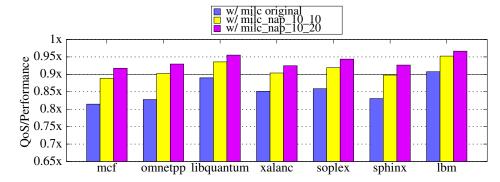

| 5.13 | Napping sledge is effect on co-runners, blockie and           |    |

|------|---------------------------------------------------------------|----|

|      | bst. Nap granularity is 1ms. As nap duration increases,       |    |

|      | sledge_l's execution rate deceases, blockie and bst's QoS     |    |

|      | improves                                                      | 85 |

| 5.14 | Napping sledge_l's effect on co-runners. Nap granularity is   |    |

|      | 10ms                                                          | 85 |

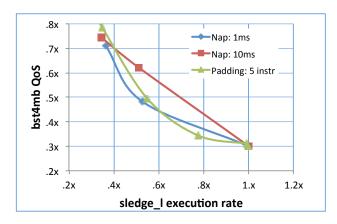

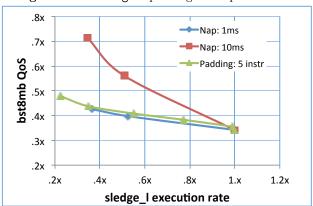

| 5.15 | sledge_l padding vs. nap for bst4mb                           | 86 |

| 5.16 | sledge_l padding vs. nap for bst8mb                           | 86 |

| 5.17 | sledge_l padding vs. nap for bst50mb                          | 86 |

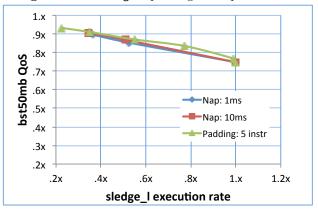

| 5.18 | SPEC benchmark's performance when it is co-located with       |    |

|      | the original lbm, lbm with nap insertion (10ms, 10ms) and     |    |

|      | nap insertion (10ms, 20ms), normalized by each benchmark's    |    |

|      | performance when it is running alone                          | 89 |

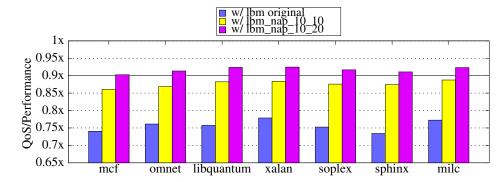

| 5.19 | SPEC benchmark's performance when it is co-located with       |    |

|      | the original milc, milc with nap insertion (10ms, 10ms) and   |    |

|      | nap insertion (10ms, 20ms), normalized by each benchmark's    |    |

|      | performance when it is running alone                          | 89 |

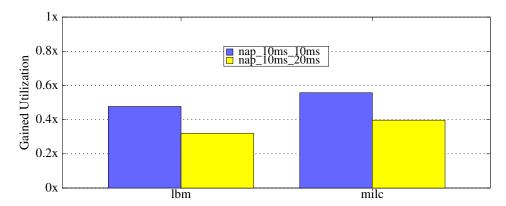

| 5.20 | Gained Utilization when allow co-location                     | 91 |

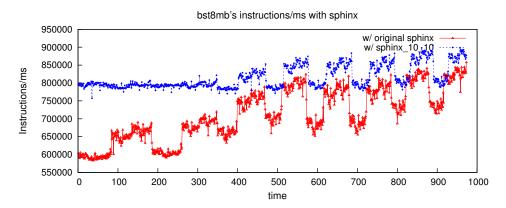

| 5.21 | bst8mb running with sphinx                                    | 92 |

| 5.22 | Google benchmark's performance when it is co-located with     |    |

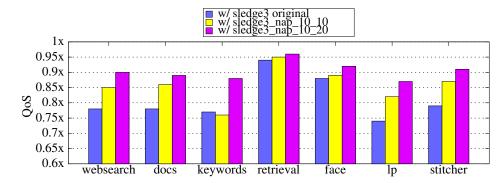

|      | the original sledge3, sledge3 with nap insertion (10ms, 10ms) |    |

|      | and nap insertion (10ms, 20ms), normalized by each bench-     |    |

|      | mark's performance when it is running alone                   | 93 |

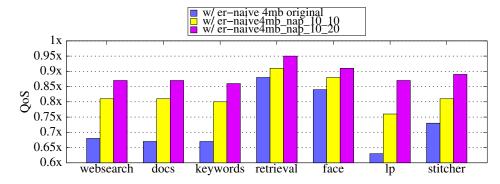

| 5.23 | Google benchmark's performance when it is co-located with     |    |

|      | the original er-naive4mb, er-naive4mb with nap insertion      |    |

|      | (10ms, 10ms) and nap insertion (10ms, 20ms), normalized       |    |

|      | by each benchmark's performance when it is running alone .    | 94 |

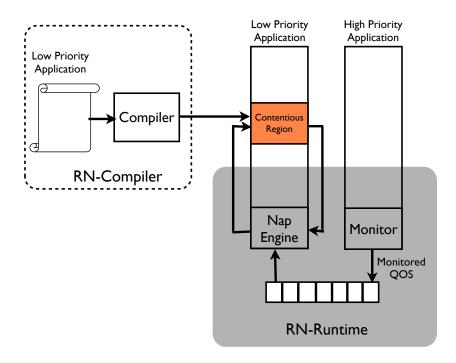

| 6.1  | Reactive-Niceness Overview                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

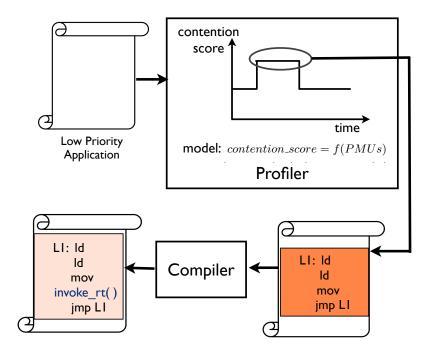

| 6.2  | Reactive-Niceness Compilation                                                                                                                                                  |

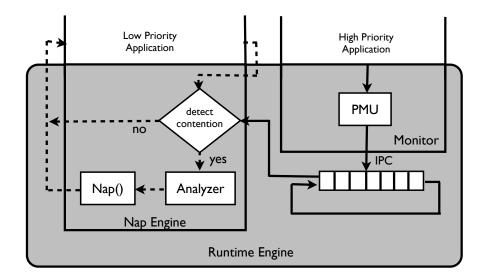

| 6.3  | Reactive-Niceness Runtime Architecture                                                                                                                                         |

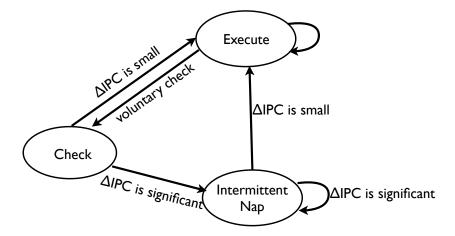

| 6.4  | DFA for targeted Heuristic                                                                                                                                                     |

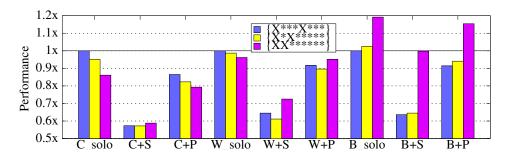

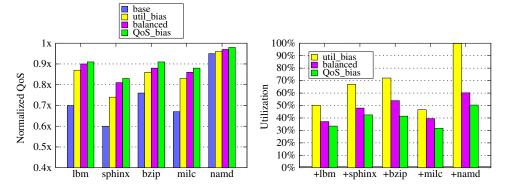

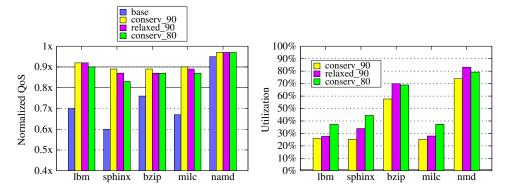

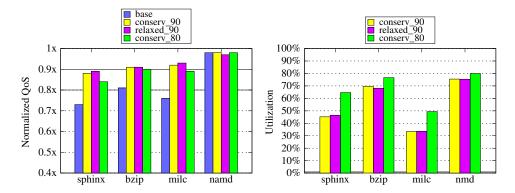

| 6.5  | QoS of each benchmark co-running with sledge, normalized                                                                                                                       |

|      | to solo QoS. (simple)                                                                                                                                                          |

| 6.6  | Utilization of sledge with each configuration. (simple) 112                                                                                                                    |

| 6.7  | QoS of each benchmark co-running with 1bm. (simple) 112                                                                                                                        |

| 6.8  | Utilization of 1bm with each configuration. (simple) 112                                                                                                                       |

| 6.9  | QoS of each benchmark co-running with ${\tt milc.}~({\tt simple})$ 113                                                                                                         |

| 6.10 | Utilization of milc with each configuration. (simple) 113                                                                                                                      |

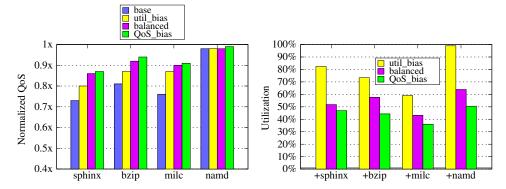

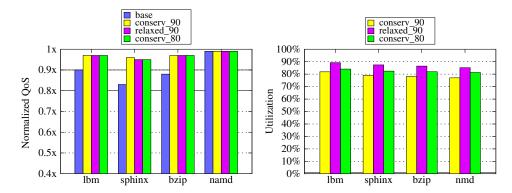

| 6.11 | QoS of each benchmark co-running with sledge, normalized                                                                                                                       |

|      | to solo QoS. (targeted)                                                                                                                                                        |

| 6.12 | Utilization of sledge with each configuration. (targeted) $115$                                                                                                                |

| 6.13 | $\operatorname{QoS}$ of each benchmark co-running with 1bm. (targeted) $% \operatorname{Policy}\left( \operatorname{Spec}\left( \operatorname{Appendix}\right) \right) =0$ 115 |

| 6.14 | Utilization of 1bm with each configuration. (targeted) $115$                                                                                                                   |

| 6.15 | $\mathrm{QoS}$ of each benchmark co-running with $\mathtt{milc.}$ (targeted) $$ . $116$                                                                                        |

| 6.16 | Utilization of milc with each configuration. (targeted) 116                                                                                                                    |

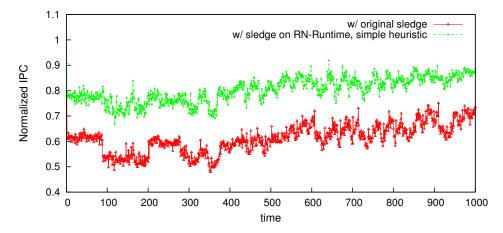

| 6.17 | Sphinx normalized IPC with original sledge and with                                                                                                                            |

|      | <b>sledge</b> with RN_H1                                                                                                                                                       |

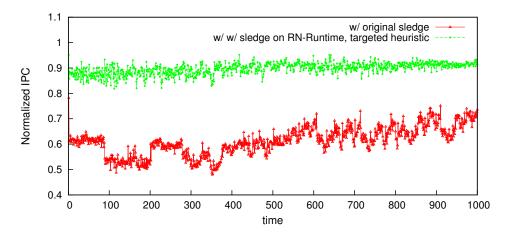

| 6.18 | Sphinx normalized IPC with original sledge and with                                                                                                                            |

|      | <b>sledge</b> with RN_H2                                                                                                                                                       |

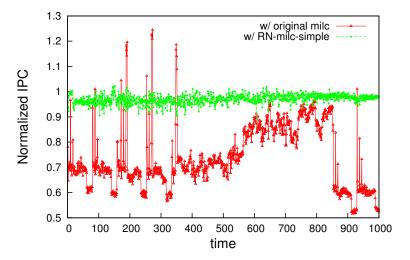

| 6.19 | Sphinx normalized IPC with original milc and with simple                                                                                                                       |

|      | milc                                                                                                                                                                           |

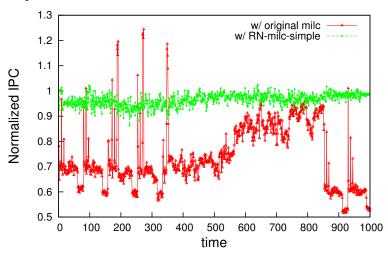

| 6.20 | Sphinx normalized IPC with original milc and with                                                                                                                              |

|      | targeted milc                                                                                                                                                                  |

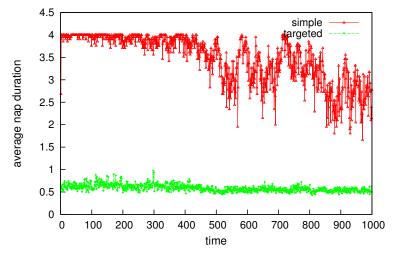

| 6.21 | Average nap duration for milc with simple vs. milc with                                                                                                                        |

|      | targeted                                                                                                                                                                       |

| $List\ o$ | f Figures | 16 | 3 |

|-----------|-----------|----|---|

| List o    | f Figures | 1( | ) |

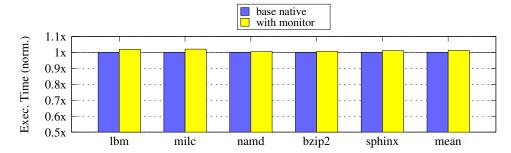

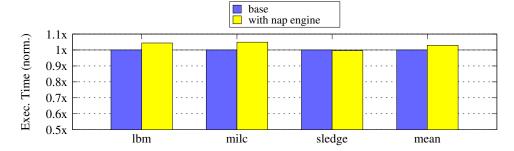

| 6.22 | Overhead of monitoring for high-priority application 1       | .21 |

|------|--------------------------------------------------------------|-----|

| 6.23 | Overhead of nap engine for low-priority application 1        | .21 |

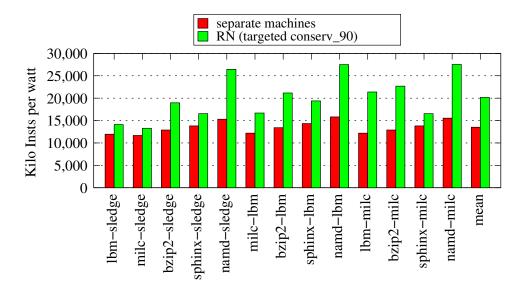

| 6.24 | Efficiency of allowing co-location with Reactive-Niceness vs |     |

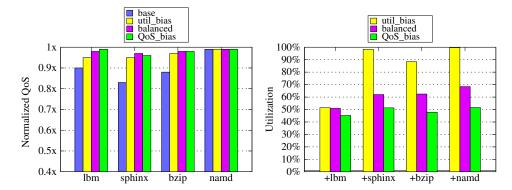

|      | over-provisioning. (targeted)                                | .23 |

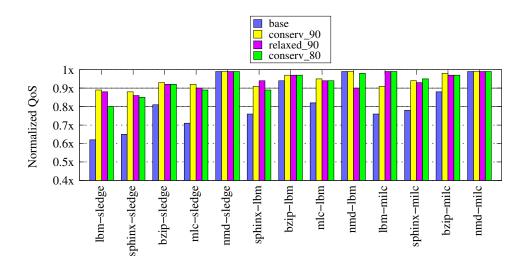

| 6.25 | QoS of each benchmark co-running with sledge, 1bm, and       |     |

|      | milc. (targeted)                                             | .24 |

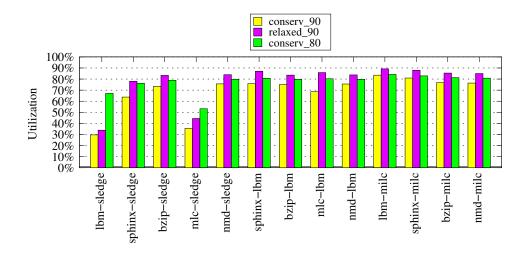

| 6.26 | Utilization of sledge, 1bm and milc with each configuration. |     |

|      | (targeted) 1                                                 | 24  |

# List of Tables

| 3.1 | Sharing configurations for sets of $2$ cores and sets of $4$ cores . | 30  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | Experiment Platform                                                  | 30  |

| 3.3 | Production Datacenter Applications                                   | 31  |

| 3.4 | Optimal Thread-To-Core Mapping in Solo and Co-location               |     |

|     | Situations                                                           | 44  |

| 4.1 | Predicted Thread-To-Core Mapping Using the Heuristic Ap-             |     |

|     | proach                                                               | 56  |

| 5.1 | Contention Benchmarks Suite: SmashBench                              | 73  |

| 5.2 | Comparing our contentiousness predictor to predictors used           |     |

|     | in prior works. Our predictor was trained with the Smash-            |     |

|     | Bench suite of contentious kernels and tested against all            |     |

|     | SPEC 2006 benchmarks                                                 | 81  |

| 5.3 | Production Warehouse Scale Computer Applications                     | 92  |

| 6.1 | Three configurations for simple heuristic                            | 113 |

| 6.2 | Three configurations of targeted heuristic                           | 116 |

# Chapter 1

### Introduction

#### Contents

| 1.1 | Memory Resource Sharing and Contention                 |   |  |  |  |

|-----|--------------------------------------------------------|---|--|--|--|

| 1.2 | Implications of Memory Resource Contention             | 3 |  |  |  |

|     | 1.2.1 The Impact of Contention on Performance          | 4 |  |  |  |

|     | 1.2.2 The Impact of Contention on Server Utilization   | 4 |  |  |  |

|     | 1.2.3 Trade-offs Between Performance and Utilization . | 5 |  |  |  |

| 1.3 | Mitigating Contention                                  |   |  |  |  |

| 1.4 | Two Strategies for Mitigating Contention               |   |  |  |  |

|     | 1.4.1 Mitigating Contention to Improve Performance     | 8 |  |  |  |

|     | 1.4.2 Mitigating Contention to Improve Utilization 10  | 0 |  |  |  |

| 1.5 | Summary of Contributions                               | 2 |  |  |  |

Webservice datacenters and cloud computing economies of scale have gained significant momentum in today's computing environments. Companies such as Google, Microsoft, Yahoo, Facebook, Apple and Amazon host large-scale data intensive applications including search, email, maps, docs, video, social networking and other cloud services that require execution on a Warehouse Scale Computer (WSC) [5]. A warehouse scale computer often houses tens of thousands of machines to provide the computing resources needed to serve millions of users and typically costs hundreds of

millions of dollars to construct and operate. This large cost stems from purchasing servers, power, cooling and other infrastructural and operational cost [13, 17].

To reduce the cost and to improve the efficiency of WSCs, it is important to improve both **software performance** and **server utilization** [5]. For example, improving performance and server utilization can reduce the cost for infrastructure construction, server purchase and power consumption. At the massive scale of modern WSCs of web-services companies such as Google, 1% improvement in either performance or utilization translates to millions of dollars saved. However, memory resource sharing and contention inhibits the efficiency of WSCs.

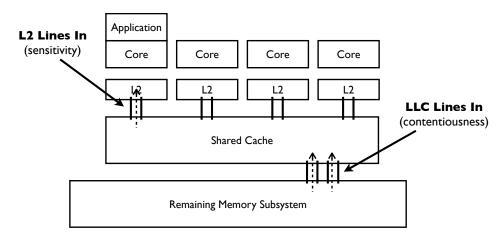

#### 1.1 Memory Resource Sharing and Contention

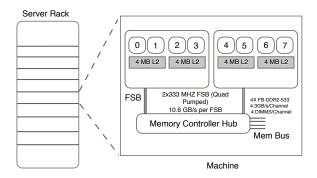

One of the major challenges that limit the efficiency in WSCs is the contention for memory subsystem resources on the servers that populate WSCs. Modern WSCs are constructed using commodity multicore machines as they are inexpensive and easily replaceable. Typically, these server machines have multiple sockets hosting processors with multiple cores. The processing cores may share a number of caches, buses and controllers. As an example, Figure 1.1 shows a typical dual-socket machine configuration found in production WSCs. Each socket on this system has two separate L2 caches shared by a pair of cores and all four cores on a socket share a Front Side Bus (FSB). This type of machine organization is commonplace in state-of-the-art server processors. The sharing of these memory resources across multiple cores often has a significant impact on application performance. This impact may be constructive or destructive.

• When multiple cores share a resource, the threads running on those

Figure 1.1: Topology of a Dual Socket Intel Clovertown

cores can *constructively* use this resource in a number of ways. For example, when threads share a cache, data sharing requires only one copy of the data in the shared cache rather than multiple copies spread out across private caches. Furthermore, memory bus and coherence traffic is reduced since data is fetched from memory only once and does not ping-pong back and forth between separate private caches.

• However, multiple threads, either from an individual application or multiple applications, can also contend for shared resources. Memory resource contention has a destructive impact on performance. For example, a thread can bring its own data into a shared cache, evicting the data of a neighboring thread and resulting in performance interference and degradation. Threads can also contend for prefetchers, memory controllers and bus bandwidth, detrimentally affecting performance.

### 1.2 Implications of Memory Resource Contention

Memory resource contention has a negative impact on both application performance and server utilization, significantly limiting the efficiency of modern warehouse scale computers.

#### 1.2.1 The Impact of Contention on Performance

The destructive performance impact caused by contention can often be significant. Prior work reports up to 60% performance degradation due to contention using SPEC CPU2006 benchmarks and state-of-the-art server machines [65, 15, 40]. Therefore, it is greatly beneficial to mitigate contention and to exploit the potential positive resource sharing to improve application performance.

However, currently, there is little understanding about the interaction between the shared memory subsystem and the emerging large-scale datacenter workloads. Prior work largely relies on popular small-scale benchmark suites such as SPEC and PARSEC, and has reached conflicting conclusions about whether cache sharing has a significant performance impact, especially for contemporary multi-threaded applications [62]. To the best of our knowledge, no prior work has investigated the memory resource sharing for industry-strength emerging datacenter workloads. Although modern WSCs have generally adopted the policy of disallowing colocation of certain applications to avoid potential performance interference, the severity of the interference due to contention is unclear. Due to the lack of understanding, current software systems in WSCs do not acknowledge or manage the resources sharing among application threads, resulting in potential performance inefficiencies.

#### 1.2.2 The Impact of Contention on Server Utilization

In addition to performance, the interference caused by memory resource contention also proves particularly problematic to large-scale web service applications as it may prevent these applications from providing satisfactory quality of service (QoS). On one hand, in order to reduce the machine and operational cost, it is essential for datecenters to consolidate various

workloads on multicore servers to improve machine utilization [46]. On the other hand, warehouse scale computer workloads are composed of diverse applications with varying QoS requirements and priorities. Key applications, usually those that are user-facing and provide interactive service such as search, mail and maps, are latency sensitive and have fairly strict QoS requirements. Other applications such as backup service and file compression are batch applications that are not latency sensitive or have a lower QoS priority. When co-locating applications on a multicore platform, the performance and QoS of high priority applications may suffer unacceptable amounts of degradation due to resource contention and interference [58, 38]. Moreover, high priority applications may even suffer more QoS degradation than low priority applications, resulting in unacceptable priority inversion. As a result, modern warehouse scale computers often resort to disallowing co-location of latency-sensitive applications with any other applications, which leads to costly low machine utilization [6]. This over-provisioning of compute resources is one of the major reasons the utilization in modern WSCs remains low, recently reported to be below 30% on average [42].

#### 1.2.3 Trade-offs Between Performance and Utilization

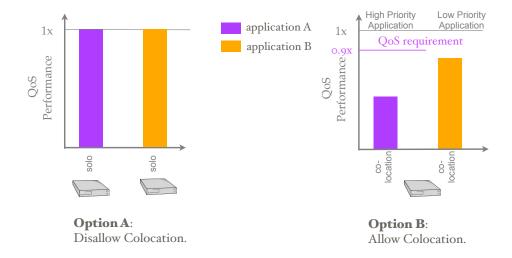

Figure 1.2 further illustrates the performance interference caused by contention and its implications for the tradeoffs between performance, QoS and utilization in WSCs. Disallowing colocation of applications, shown as Option A, achieves peak application performance at the sacrifice of machine utilization. The alternative, allowing colocation, shown as Option B, improves machine utilization at the risk of impairing latency sensitive applications' capability to deliver acceptable QoS. The current approach in modern warehouse scale computers is fairly ad-hoc with a mix of these two options. WSCs may allow colocation of applications that do not necessarily

**Figure 1.2:** Current Two Options in WSCs. Option A, disallowing colocation of applications, achieves peak application performance at the sacrifice of machine utilization. Option B improves machine utilization and reduces the number of server machines needed. However, applications may suffer significant performance degradation, which can impair latency-sensitive applications' capability to deliver acceptable QoS.

have strict QoS requirements, and simply submit to suffering performance degradation for the sake of better machine utilization. However, for latency-sensitive applications, WSCs often resort to disallowing co-location of these types of applications with any other applications which translates to low machine utilization at the cost of millions of dollars.

In conclusion, memory resource contention has significantly limited the application performance and server utilization in WSCs; and consequently, mitigating memory resource contention is critical for improving efficiency in WSCs.

### 1.3 Mitigating Contention

This dissertation argues for the design of novel software systems that are aware of the impact of resource sharing on applications, intelligently mitigate potential memory contention and promote positive resource sharing to improve software performance. In addition, this dissertation argues for novel software systems to mitigate contention to provide QoS management on multicore machines for applications with various QoS requirements to improve server utilization.

In addition to the current lack of understanding, there are multiple challenges for designing systems that can mitigate contention to improve performance or QoS on multicore platforms. Applications may contend for a plethora of memory components including a hierarchy of caches, prefetchers, memory controllers and buses. The interaction between the applications and these various components can be fairly complicated. In addition, due to the current limited transparency and monitoring capabilities for hardware behaviors, it is challenging for system software to dynamically detect and diagnose the occurrences of memory resource contention. System software also does not have control over hardware resources such as caches and memory bandwidth, which renders responding to contention and managing applications' QoS quite challenging. As a result, despite the amount of research attention given to contention problems on multicore platforms [29, 45, 10, 19, 44, 51, 52, 28, 34, 15, 30, 24, 65, 23, 24, 7, 3, 61], mitigating the impact of contention on an application's performance and QoS, enforcing the relative QoS priorities of co-running applications, while maximizing machine utilization, remains key challenges in modern warehouse scale computers.

### 1.4 Two Strategies for Mitigating Contention

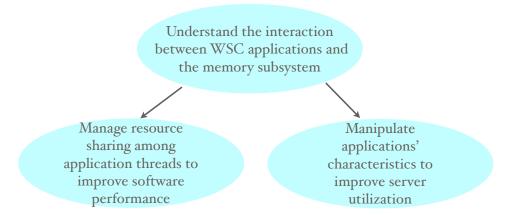

This dissertation first comprehensively investigates the impact of memory resource sharing on industry-strength large-scale datacenter workloads and provides new information and insights. The result of our investigations demonstrate that, contrary to conclusions from recent work [62], across sev-

**Figure 1.3:** Dissertation Overview - Understanding the impact of contention and 2 strategies to mitigate contention to improve performance and utilization

eral key datacenter applications including web-search, there is both a sizable benefit and a potential degradation from improperly sharing microarchitectural resources on a single machine, such as on-chip caches and bandwidth to memory. This dissertation then presents two complementary software strategies, shown in Figure 1.3, to mitigate memory resource contention for improving performance and server utilization of WSCs.

#### 1.4.1 Mitigating Contention to Improve Performance

Strategy 1: Manage resource sharing among threads to improve performance using Intelligent Thread-to-Core Mapping.

The basic idea of an intelligent thread-to-core mapper is to take advantage of the memory resource topologies (an example is shown in Figure 1.1) to promote more positive sharing and reduce negative sharing among threads. The processing cores on this machine do not share the same resources. For example, as shown in the figure, core 0 and 1 share a L2 cache, front side bus (FSB) and a memory controller. However, core 0 and 2 do not share L2 cache, and core 0 and 4 do not share FSB. Therefore, when mapping threads to cores, the mapper essentially manages what resources

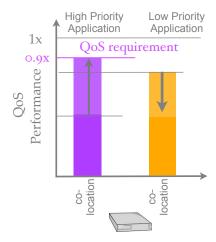

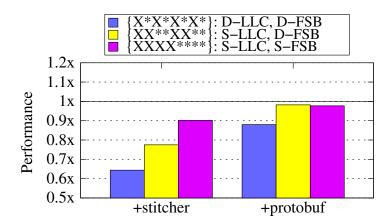

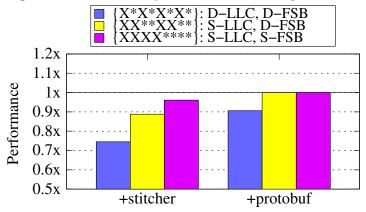

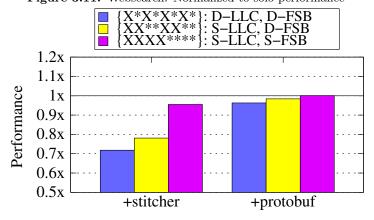

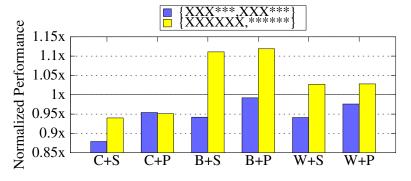

(A) Mitigate contention: improve performance

(B) Mitigate contention: improve QoS and server utilization

Figure 1.4: Enabled capabilities by our software systems. (A) illustrates the strategy 1, the TTC mapper's effect - improved performance comparing to baseline colocation situation, shown in Figure 1.2. (B) illustrates the strategy 2, Static/Dynamic Compilation for Niceness's effect. Strategy 2 improves the QoS of the high priority application to meet its QoS requirement. By doing so, strategy 2 turns previous forbidden colocations into "safe" colocations and thus improves the server utilization, comparing to the baseline of disallowing colocation shown in Figure 1.2.

are shared among threads. For example, some threads share data and may benefit from cache sharing. Thus these threads should be mapped to cores that share a cache. Others threads are contentious with each other and thus should be mapped to cores that do not share a cache or even FSB to mitigate interference. An intelligent thread-to-core mapper can take advantage of these application characteristics and the memory topologies to mitigate contention and improve performance.

This research finds that the performance variability between the worst and the optimal thread-to-core mappings can be significant for datacenter workloads. More interestingly, the best thread-to-core mapping for a given application does not only depend on the application's sharing and memory characteristics; it is also impacted dynamically by the characteristics of other applications that are co-running on the same machine simultaneously. Based on this insight, we design two approaches for intelligent thread-to-core

(TTC) mapping.

The desired outcome of our strategy for mitigating contention to improve performance is illustrated in Figure 1.4 (A).

#### • Heuristic-based approach

The application characteristics that impact performance in various thread-to-core mapping scenarios are identified. These characteristics include the amount of data sharing among threads, the amount of memory bandwidth an application requires, and the cache footprint of the application. We present an algorithm that takes advantage of these applications characteristics to identify efficient thread-to-core mappings.

#### • Dynamic approach

We also present an adaptive approach, AtoM, that uses a competition heuristic to search for the best performing mapping online. The approach includes two phases: a learning phase, when AToM empirically has various TTC mappings compete to learn which mapping performs best, and an execution phase, when the winning TTC mapping is run for a fixed or adaptive period of time.

#### 1.4.2 Mitigating Contention to Improve Utilization

Strategy 2: Manipulate applications' characteristics to improve server utilization using Static/Dynamic Compilation for Niceness

The second strategy comprises novel compilation and runtime systems to directly manipulate an application's contentious nature and reduce the interference it can cause to its corunning applications. By doing so, we facilitate more "safe" colocations where contention is mitigated so that latency-sensitive applications can provide acceptable QoS. The desired outcome of

Chapter 1. Introduction

11

our strategy for mitigating contention to improve *utilization* is illustrated in Figure 1.4 (B).

#### • Static Approach: Compiling for Niceness

Two key insights underlie this approach. Firstly, a compilation-based approach is both well-suited and desirable for WSCs. Large-scale webservice applications such as web-search, maps, email, video, etc, are both developed and hosted by the companies that operate the WSCs and their source code are available and recompiled regularly. Secondly, in the era of multicore and the emerging computing domain of WSCs, the objectives of compiler optimization ought to be multifaceted. In addition to optimizing each application for its own individual performance, we argue for the additional objective of optimizing for an application's "niceness"; to reduce its potential interference to its corunning applications.

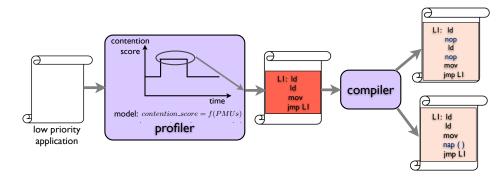

Our approach, QoS-Compile, uses novel compilation techniques to directly manipulate the contentiousness of low priority applications to ensure the QoS of a higher priority co-runner. With this, high machine utilization can be achieved through allowing colocation while providing satisfactory QoS. QoS-Compile uses a prediction model to pinpoint code regions that aggressively demand memory resources. It then targets these regions, transforms their code layouts to reduce their contentiousness by throttling down their memory request rate, thus reducing its interference to the QoS of its co-runners. To the best of our knowledge, QoS-Compile is the first compilation approach to address the QoS challenges caused by contention for multi-programmed workloads.

#### • Dynamic: Reactive Niceness

Enabled by the above static approach, we designed a light-weight dynamic approach, Reactive-Niceness, to further improve QoS and utilization. Reactive-Niceness instruments the contentious regions to enable the flexible manipulation of their contentiousness at runtime. Dynamically, Reactive-Niceness detects contention-caused QoS degradation and adaptively throttles down the memory request rate of those contentious regions in the low-priority application. The degree of execution rate reduction on low-priority applications is based on the severity of observed QoS degradation of the high-priority application and a feed-back control, enabling the flexibility needed to further improve machine utilization and achieve more precise QoS management.

In summary, this dissertation advances the state-of-the-art for understanding and managing the impact of memory resource contention on largescale emerging WSC workloads, and provides effective software systems to mitigate contention to significantly improve both **application performance** and **server utilization** in WSCs.

### 1.5 Summary of Contributions

We first conduct a thorough investigation of the impact of sharing memory resources (e.g., shared caches and memory bandwidth) on key commercial datacenter applications including Google's web-search engine and bigtable (a peta-scale data storage software). This work is the first to characterize the impact of memory resource sharing on real-world large-scale datacenter applications, exposing new insights about these emerging workloads and demonstrating the significant impact of memory contention. Chapter 3 examines

• Intra-application sharing: We investigate the impact of memory re-

source sharing on threads that belong to a single multithreaded application [59] (Section 3.2). While prior work has found neither positive nor negative effects from cache sharing across benchmark suites, we find that across these datacenter applications, there is both a sizable benefit and a potential degradation from improperly sharing resources.

• Inter-application sharing: We investigate the impact of memory resource sharing on threads that belong to multiple multithreaded applications [59] (Section 3.3). Our investigation demonstrates that memory resource contention among multiple applications often cause significant performance degradation. Our investigation also shows that, contrary to common intuition, the optimal thread-to-core mapping for a given application changes depending on its execution environment, including the underlying machine, whether it is running alone, and if not, which application it is co-running with.

We then apply the discoveries and insights from the investigation and design intelligent thread-to-core mappers to mitigate contention and improve software performance in WSCs. Chapter 4 presents

- Heuristics based thread-to-core mapper: We identify the application characteristics that impact performance in the various thread-to-core mapping scenarios and provide a technique for deriving algorithms from these characteristics for heuristics based thread-to-core mapping to improve performance efficiency in WSCs [59] (Section 4.1).

- Automatic thread-to-core mapper (AToM): We also present the design of an adaptive approach that uses a competition heuristic to learn the best performing mapping online to improve performance that is agnostic to the underlying microarchitecture [59] (Section 4.2).

To address the server utilization and QoS challenges, we design a static compilation approach, QoS-Compile, for effective QoS management on multicores to facilitate workload consolidation and improve server utilization in WSCs. QoS-Compile is the first compilation approach to effectively addressing the QoS challenges caused by contention for multiple co-running applications. Chapter 5 presents

- Profiling techniques to identify contentious code regions: We design a prediction model that is based on the performance counters to pinpoint code regions that aggressively demand memory resources [57, 56] (Section 5.2).

- Novel code transformations to dampen code regions' contentious nature: We design two compilation techniques that reduce a code region's contentiousness and the potential performance interference it can cause to co-runners [57] (Section 5.3).

In addition to static compilation techniques, we design a staticallyenabled runtime system, **Reactive-Niceness**, to further improve server utilization and achieve more accurate QoS management of latency-sensitive applications. Chapter 6 presents

- RN-Compiler: We present a profiling guided compilation approach that enables the adaptive manipulation of contentiousness of the low-priority application. The RN-Compiler identifies the contentious code regions of an application and inserts hooks in these regions that are used to invoke runtime manipulation [55] (Section 6.2).

- RN-Runtime: We present a runtime system that continuously monitors the QoS of high-priority applications, detects when contention is occurring dynamically, and directs the manipulation of the contentiousness of low-priority applications based on an adaptation policy. We

also present two adaptation policies for flexible adjustments of the tradeoffs between QoS and utilization [55] (Section 6.3).

Collectively, this dissertation takes a major leap forward in understanding and mitigating memory resource contention to improve efficiency in the emerging domains of large scale web-services and modern warehouse scale computers. We demonstrate the need for new types of software systems in modern WSCs and design effective mechanisms to fundamentally address the detrimental impact of memory resource contention on efficiency of WSCs to greatly improve both performance and server utilization.

# Chapter 2

# Background and Related Work

| Contents |                  |                                                   |    |

|----------|------------------|---------------------------------------------------|----|

| 2.1      | Ware             | chouse Scale Computers                            | 16 |

|          | 2.1.1            | Cost                                              | 17 |

|          | 2.1.2            | Application QoS                                   | 17 |

|          | 2.1.3            | Job Scheduling, Application Colocation and Uti-   |    |

|          |                  | lization                                          | 18 |

|          | 2.1.4            | Machine Level                                     | 21 |

| 2.2      | 2.2 Related Work |                                                   | 22 |

|          | 2.2.1            | Impact of Memory Resource Sharing                 | 22 |

|          | 2.2.2            | Novel Hardware Solutions to Mitigate Contention . | 22 |

|          | 2.2.3            | Software Runtime and OS Approaches to Mitigat-    |    |

|          |                  | ing Contention                                    | 23 |

|          | 2 2 4            | Cache Contention Aware Compilation                | 25 |

### 2.1 Warehouse Scale Computers

This chapter reviews the background and related work of this dissertation. We first present the background of modern warehouse scale computers including its cost breakdown (Section 2.1.1), the QoS metrics of applications

that are running in these datacenters (Section 2.1.2), the job scheduling on a cluster level (Section 2.1.3) and on a machine level (Section 2.1.4). We then present related work, especially on the topic of memory resource contention from both software and hardware communities (Section 2.2).

#### 2.1.1 Cost

To better understand the importance of improving performance and server utilization, let us first examine the cost of a modern warehouse computer. Figure 2.1 is from "The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines" by Barroso et al. [5]. It presents a 3-year total cost of ownership (TCO) breakdown of a datacenter housing commodity servers, including both capital cost and operational cost. As shown in the figure, serve purchase, power and datacenter construction are several major components of the TCO. Improving performance and utilization can reduce the cost for all these components. Better performance and higher server utilization indicate less servers needed for the given amount of work, less power consumed by these servers and a smaller datacenter to host these servers.

#### 2.1.2 Application QoS

Applications that are running in a warehouse scale computer often have various quality-of-service (QoS) priorities. User-facing applications such as web-search, maps, email and other internet services are *latency-sensitive*, and have high QoS priorities. Applications such as file backup, offline image processing, and video compression are *batch* applications that often have no QoS constraints. For these, latency is not as important.

In this dissertation, we define the QoS of a latency-sensitive application in terms of the relevant performance metric specified in its internal service

$\textbf{Figure 2.1:} \ \, \textbf{TCO (Total Cost of Ownership) cost breakdown for a datacenter using commodity servers} \\$

level requirements (SLAs). For example, the QoS of Google's web-search is measured using query latency and queries-per-second. This is in contrast to Bing's [22, 32], which uses the quality of search results provided. And a job's QoS level of 95% corresponds to the normalized 95% of its performance when an entire machine is dedicated to that job. More details and examples of applications and their QoS or performance metrics are presented in Section 3.1 Table 3.3.

# 2.1.3 Job Scheduling, Application Colocation and Utilization

In this section, we examine the current job scheduling in a modern WSC, the application colocation policy and the current server utilization. In the modern datacenter, job scheduling is done in a hierarchical fashion. A global job scheduler manages a number of machines and selects a particular machine for each job. Once a job is mapped to a machine, the machine-level scheduler then decides the mapping and scheduling of the job and its threads.

Figure 2.2: Task placement in a cluster. The cluster manager does not co-locate latency-sensitive applications with others to protect their QoS from performance interference, causing low machine utilization.

In this section, we focus on the cluster level scheduler. We discussion the machine level scheduler in the next section.

In modern warehouse scale computers, each web-service is composed of one to hundreds of application tasks, and each task runs on a single machine. An application task is composed of the application binary, associated data, and a configuration file that specifies the machine level resources required. These resources include the number of cores, amount of memory, and disk space that are to be allocated to the task. The configuration file for a task may also include special rules for the cluster manager such as whether to disallow co-locations with other tasks. Application task is conducted by the cluster-level manager that is responsible for a number of servers. Based on the resource requirement, the cluster manager uses an algorithm similar to bin-packing to place each task in a cluster of machines [43].

#### **Application Colocation**

As multicores become widely adopted in datacenters, the cluster manager often consolidates multiple disparate tasks on a single server to improve

Figure 2.3: Server Utilization Histogram from HP datacenters.

the machine utilization. However, to avoid the performance interference, latency-sensitive applications that have strict QoS are not co-located with any other applications. A simplified illustration of the application task placement process is shown in Figure 2.2. Latency-sensitive tasks that disallow co-location inadvertently occupy more resources on a server leading to unnecessary server overprovisioning and low machine utilization.

#### Sever Utilization

The current server utilization in warehouse-scale computers is typically quite low, often below 30%. Figure 2.3 presents a histogram of utilization for two production workloads, "web 2.0" applications and enterprise IT applications, from enterprise-scale commercial deployments [42]. The data presented is from utilization traces collected over many days, aggregated over more than 120 severs (production utilization traces were provided courtesy of HP Labs). As shown here, the servers spend the vast majority of time under 10% utilization.

Figure 2.4 presents a histogram of average CPU utilization of more than 5,000 servers during a six-month period in Google production datacenters [5]. As shown in the figure, servers rarely operate near their maximum utiliza-

Figure 2.4: Activity profile of a sample of 5,000 Google servers over a period of 6 months.

tion. The average utilization shown here is around 30%. The policy of disallowing colocation of latency-sensitive applications is one of the main reasons for the low utilization.

#### 2.1.4 Machine Level

Once application tasks are mapped on a machine, on the individual machine level, general purpose system software such as the Linux kernel is adapted for, and used in the datacenter for finer grain scheduling. The state-of-the-art kernel scheduler focuses on load balancing and prioritizes cache affinity to reduce cache warm-up overhead. It does not take memory resource sharing into account. The scheduler's thread-to-core mapping is determined without regard to, or knowledge of, the application characteristics or the underlying resource sharing topology. Although developers can specify which cores to use manually, this must be done on an application by application, architecture by architecture basis. As a result, this option is seldom used as it places a significant burden on the developer.

#### 2.2 Related Work

#### 2.2.1 Impact of Memory Resource Sharing

Currently, little is known about the impact of memory resource sharing on large-scale web-service datacenter applications. A great amount of prior work has concluded that contention has a significant impact on the performance of traditional workloads using common benchmark suites such as SPEC [65, 15, 40]. However, recent work by Zhang et al. concludes that contemporary multithreaded applications are not affected by cache sharing using a multithreaded benchmark suite PARSEC [62]. To the best of our knowledge, no prior work has investigated the impact of memory resource sharing for industry-strength emerging datacenter workloads. The commonly-used benchmark suites (SPEC, PARSEC, etc) do not necessarily represent these workloads, and thus may be misleading.

#### 2.2.2 Novel Hardware Solutions to Mitigate Contention

Hardware techniques such as cache partitioning and bandwidth partitioning to reduce resource contention and improve performance and fairness on multicores have received much research attention [29, 45, 10, 19, 44, 51, 52, 28, 34]. In addition, there also have been a number of works aimed at better modeling cache contention [8] and monitoring cache contention [64].

Most of the above studies focus on either overall performance or performance fairness. Recently, platform support that enforces different QoS priorities has been proposed [16, 21, 12, 18]. Among these studies, a promising direction for QoS management is hardware execution throttling. Herdirch et al. [18] use what is likely to be future hardware capabilities, core specific dynamic voltage scaling and clock modulation to throttle down low priority applications to reduce their performance interference on the high