# ReSense: A Unified Framework for Improving Performance and Reliability in Multicore Architectures

A Dissertation

Presented to

the Faculty of the School of Engineering and Applied Science

University of Virginia

In Partial Fulfillment

of the requirements for the Degree

Doctor of Philosophy (Computer Science)

by

Tanima Dey

August 2014

## **Approval Sheet**

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science)

## Tanima Dey

Tanima Dey

This dissertation has been read and approved by the Examining Committee:

## Mary Lou Soffa

Mary Lou Soffa, Advisor

## Jack W. Davidson

Jack W. Davidson, Advisor

## Sudhanva Gurumurthi

Sudhanva Gurumurthi, Committee Chair

## Mary Jane Irwin

Mary Jane Irwin, Pennsylvania State University

### John Lach

John Lach, Minor Representative

James H. Ay

Accepted for the School of Engineering and Applied Science:

James H. Aylor, Dean, School of Engineering and Applied Science

August 2014

## Abstract

Chip-multiprocessors (CMPs) have become ubiquitous in modern computing and the mainstream architecture for various platforms, including laptops, desktops, and large server machines. As technology scaling continues and more transistors are accommodated on the chip, the number of cores on CMPs is growing, and multi-core machines are scaling up to many-core machines. With this multi-core scaling, two major problems arise: shared-resource contention and soft errors or transient faults. Shared-resource contention can degrade an application's performance significantly, and soft errors increase the probability of incorrect application execution and the production of visible errors. To realize the full potential of multi- and many-core platforms, it is critical to ensure that applications in a workload not only execute efficiently and fast, but also correctly.

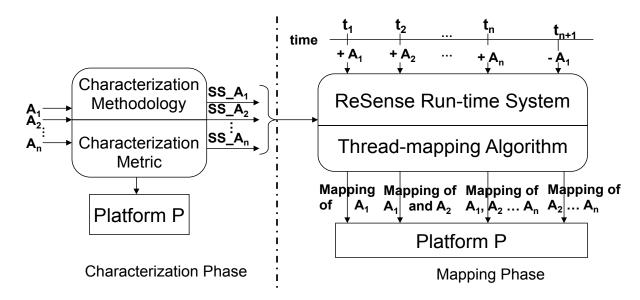

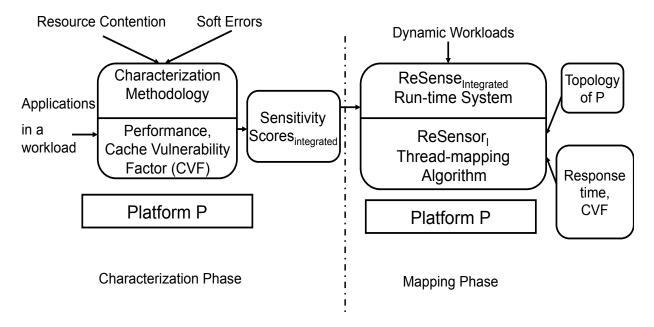

In this dissertation, we develop a novel, general, and unified framework, ReSense, to address several challenges on multicore architectures including performance optimization, reliability improvement, power and thermal management. The framework includes five components: a general characterization methodology, a characterization metric, a sensitivity score, a thread mapping algorithm, and a run-time system. An instance of the framework is applied in two phases: characterization and mapping. The characterization phase utilizes the general characterization methodology and characterization metric to identify application characteristics without considering any co-runner(s). It generates a resource-sensitivity score for each application in a workload. In the mapping phase, the run-time system uses a thread-mapping algorithm and the sensitivity scores of the applications in a workload to

Abstract

determine the thread-mappings that optimize the objective function of the targeted problem.

To demonstrate the utility and effectiveness of ReSense, we use it to address the problems of shared-resource contention and soft errors for multi-threaded applications. For the resource contention problem, the characterization methodology determines how a multi-threaded application's performance is affected as it shares a resource in the memory hierarchy. A sensitivity score based on resource contention is produced for each application in a workload. The run-time system uses the resource-contention sensitivity scores and a thread-mapping algorithm to allocate threads from a workload to core to mitigate shared-resource contention, thus improving response time and throughput.

For the soft error problem, the characterization methodology determines how a multithreaded application's vulnerability to soft errors in shared caches is affected by its resource occupancy duration. A sensitivity score based on cache occupancy is produced for each application in a workload. The run-time system uses the cache-occupancy sensitivity scores and a thread-mapping algorithm to allocate workload threads to cores to reduce the occupancy in the shared caches, thus reducing cache vulnerability.

Both minimizing an application's vulnerability to soft errors and maintaining application performance are critical. The thread-mapping algorithm that ensures better reliability may not ensure better performance. To address this problem, we develop an integrated instance of the framework that combines application characterizations for both contention and vulnerability to determine a trade-off between the performance and reliability improvements.

The dissertation includes a comprehensive evaluation of all three instances, which indicates that the mapping of each application in a dynamic workload according to its solo-characterization is highly effective. For the resource contention instance, response time and throughput was improved up to 30% and 47%, respectively over the native operating system. For the soft error instance, cache vulnerability was reduced up to 70% over the native operating system. The integrated instance was able to achieve various trade-offs between response time and vulnerability reductions.

# Acknowledgments

This dissertation would not have been possible without the help and support from many people in my life.

First and foremost, I acknowledge my PhD advisors, Mary Lou Soffa and Jack Davidson. Over the past six years, they have taught me how to think critically, write clearly, express ideas, give good talks, and most importantly how to do good research. They have mentored me, supported me both professionally and personally, whenever I went through any tough time in my life. They have always been patient with me whenever I struggled to find my research direction and with the countless draft of the papers I wrote with them. I cannot thank them enough and am very grateful for what they did for me. They truly have been my academic parents.

I would like to acknowledge the members of my dissertation committee, Sudhanva Gurumurthi, Mary Jane Irwin, and John Lach. They have given me feedback on my dissertation proposal to make the work better. Especially, I would like to thank Sudhanva. Whenever I wanted any advice from him about the reliability work, he always made time from his busy schedule to discuss with me.

I thank my lab and research mate, Wei Wang, for his support, feedback and honest opinion about my work. I acknowledge Jason Mars, who has been a good mentor to me. In the initial years of my PhD, both Jason and Lingjia had long discussions with me about my research and shared their thoughts about how to write a good paper. I also thank Kristen Walcott and Jing Yang for their feedback on my early ideas of the dissertation proposal.

Acknowledgments

I thank the systems staff, especially Scott Ruffner and Essex Scales, for their help and assistance whenever there was any problem with the machines and servers. They have always tried to accommodate any request I had. I also thank the CS department staff for keeping me on track in terms of official paper work.

I am grateful to all my teachers in Bangladesh, from the elementary to undergraduate school. They all have contributed to my intellectual ability, starting from how to get my hand writing (which I hardly get to do anymore) better to in-depth and broad knowledge in computer science.

I acknowledge all my friends and acquaintances at UVA and in Charlottesville. I am grateful to Taniya Siddiqua for being such a great mentor and sister to me. She has inspired me in numerous ways and gave me the courage and strength to survive through the hard graduate life. My life in Charlottesville would not have been the same without so many friends here, including my "bachcha-party": Yamina, Anindya, Emi, Asif, Samee. Special thanks to Juhi for keeping me active and full of spirit during the last six months and the most stressful time of my graduate life.

I acknowledge Charlottesville for the wonderful six years. I have loved every moment I have lived here, including the beauty of the Blue Ridge Mountains, the beautiful fall, every snowstorm in the winter, and the soothing rain in the summer. This is the place where two of my dreams came true. Charlottesville will always be my second home and remain special to me.

I am very blessed to have many dear friends in my life. Some have been friends with me for almost 20 years: Shemul (Mollick), Setu, Tithi. I acknowledge Laboni and Shantonu, for listening to my endless complaints about everything that goes wrong in my life, including paper rejections. I acknowledge Chayan, Sagar, Shafi, and Nabila for keeping my spirit high whenever I felt low. I am grateful for their continuous support and unconditional friendship, which gave me enough strength in my graduate life.

I acknowledge my family. Didi and Dida have been a constant source of encouragement.

Acknowledgments

Pishi taught me how to think positively in life, which helped me during my graduate life. I acknowledge all Kaka-Kakimas, Mama-Mamis, my cousins for supporting me during the hard times in my life. I acknowledge my family here in USA, MonDidi and family, SamarDada and family, Kumar, Ann, and Kent for making a foreign country feel like home. I acknowledge my Baba for inspiring me to overcome the difficulties and frustration in life.

I acknowledge my husband, Enamul: my best friend, harshest critic, biggest admirer, partner in crime, and co-pilot in life. Ever since I met him, he has been with me through every up and down of my life. He has made me a better version of what I am today. He has encouraged me, supported me, made me believe in my abilities and myself. I am more confident when I have him by my side. I can't wait to start the next phase of our lives together.

Last but not the least, I acknowledge my mother, Purabi Dey and Dadu, Anil Kumar Dey. I can't express in words their significance in my life. When I was in Bangladesh, Dadu used to stop by my study room every time I had any exam. I really wish he were alive to see me past the PhD finish line, where he always wanted me to be. Whenever I got frustrated and felt like giving up my PhD work, the biggest force that kept me moving was the thought of Maa and all the sacrifices she made for me in her life. I dedicate my dissertation to her.

$To\ Maa$

# Contents

| C | onter | nts      | j                                                               |

|---|-------|----------|-----------------------------------------------------------------|

|   | List  | of Table | es                                                              |

|   | List  | of Figur | res m                                                           |

| 1 | Intr  | roducti  | on 1                                                            |

|   | 1.1   | Challer  | nges in Multicore Systems                                       |

|   |       | 1.1.1    | Complex and Dynamic Workloads                                   |

|   |       | 1.1.2    | Resource Contention                                             |

|   |       | 1.1.3    | Soft Errors                                                     |

|   | 1.2   | Applica  | ation-driven Thread-mapping                                     |

|   |       | 1.2.1    | Contention/Performance Example                                  |

|   |       | 1.2.2    | Soft Error Example                                              |

|   | 1.3   | The Re   | eSense Framework                                                |

|   |       | 1.3.1    | Application Characterization                                    |

|   |       | 1.3.2    | Application Mapping                                             |

|   |       | 1.3.3    | Components of the Framework                                     |

|   |       | 1.3.4    | Generality of the Framework                                     |

|   |       | 1.3.5    | Addressing Resource Contention and Soft Errors Using ReSense 14 |

|   | 1.4   | Thesis   | Statement                                                       |

|   | 1.5   |          | Contributions                                                   |

|   | 1.6   |          | Outline                                                         |

| 2 | Rela  | ated W   | vork 19                                                         |

|   | 2.1   |          | ation Characterization                                          |

|   |       | 2.1.1    | Resource Contention Characterization                            |

|   |       | 2.1.2    | Vulnerability Characterization                                  |

|   | 2.2   |          | -resource Contention Mitigation                                 |

|   |       | 2.2.1    | Contention Mitigation for Single-threaded Applications          |

|   |       | 2.2.2    | Contention Mitigation for Multi-threaded Applications           |

|   |       | 2.2.3    | Mapping Applications using Prior Characterization               |

|   |       | 2.2.4    | Mapping Applications using Performance Prediction               |

|   |       | 2.2.5    | Cache Partitioning Techniques                                   |

|   | 2.3   |          | ques for Addressing Soft Errors                                 |

|   |       | 2.3.1    | Error Detection and Correction                                  |

|   |       | 222      | Error Drayantian                                                |

Contents j

| 3 | Res | Sense: A | A Unified Framework                                                          | 33  |

|---|-----|----------|------------------------------------------------------------------------------|-----|

|   | 3.1 | Overvi   | ew and Example of the Framework                                              | 35  |

|   | 3.2 | Charac   | terization Phase                                                             | 37  |

|   |     | 3.2.1    | Characterization Metric                                                      | 38  |

|   |     | 3.2.2    | Characterization Methodology                                                 | 39  |

|   |     | 3.2.3    | Sensitivity Score                                                            | 40  |

|   | 3.3 |          | ing Phase                                                                    | 42  |

|   |     | 3.3.1    | ReSensor <sub>Generic</sub> Thread-mapping Algorithm                         | 42  |

|   |     | 3.3.2    | Run-time System                                                              | 47  |

| 4 | Usi | ng ReS   | ense for Performance                                                         | 50  |

|   | 4.1 | •        | iction                                                                       | 50  |

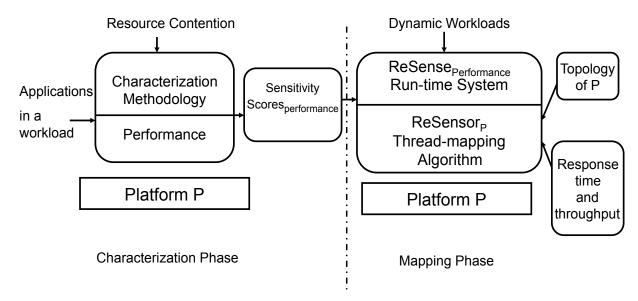

|   | 4.2 |          | eterization for Shared-Resource Contention                                   | 54  |

|   | 1.2 |          | Characterization Metric                                                      | 55  |

|   |     |          | Characterization Methodology                                                 | 56  |

|   |     | 4.2.3    | SensitivityScore <sub>performance</sub> : Sensitivity Scores for Performance | 58  |

|   | 4.3 |          | ng Co-located Multi-threaded Applications for Performance                    | 60  |

|   | 4.0 | 4.3.1    | The ReSensor <sub>P</sub> Thread-mapping Algorithm                           | 60  |

|   |     | 4.3.2    | The ReSense <sub>Performance</sub> Run-time System                           | 66  |

|   | 4.4 |          | tion of the ReSense_Performance Instance                                     | 67  |

|   | 4.4 | 4.4.1    | Characterization: Experimental Details and Results                           | 67  |

|   |     |          | Characterization: Discussion and Summary                                     | 96  |

|   |     |          | Mapping: Experimental Details and Results                                    | 98  |

|   |     | 4.4.4    | Mapping: Discussion and Statistical Analyses                                 | 109 |

|   |     | 4.4.4    | Mapping: Performance Comparison with Experimentally Determined               | 109 |

|   |     | 4.4.0    |                                                                              | 110 |

|   | 1 5 | Cumme    | 1 0                                                                          | 115 |

|   | 4.5 | Summa    | ary                                                                          | 110 |

| 5 | Usi | ng ReS   | ense for Reliability                                                         | 117 |

|   | 5.1 | Introdu  | action                                                                       | 117 |

|   | 5.2 | Charac   | terization for Vulnerability to Soft Errors                                  | 123 |

|   |     | 5.2.1    | Background                                                                   | 123 |

|   |     | 5.2.2    | Characterization Metric                                                      | 126 |

|   |     | 5.2.3    | Characterization Methodology                                                 | 127 |

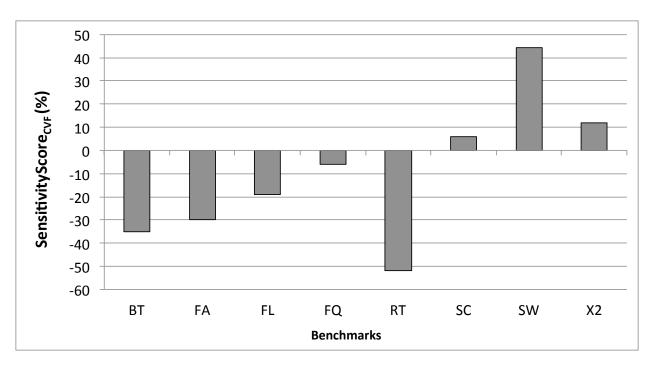

|   |     | 5.2.4    | SensitivityScore <sub>CVF</sub> : Sensitivity Scores for Reliability         | 129 |

|   | 5.3 | Mappir   | ng Co-located Multi-threaded Applications for Reliability                    | 130 |

|   |     | 5.3.1    | The ReSensor <sub>R</sub> Thread-mapping Algorithm                           | 130 |

|   |     | 5.3.2    | TheReSense <sub>Reliability</sub> Run-time System                            | 139 |

|   | 5.4 |          | tion of the ReSense_Reliability Instance                                     | 139 |

|   |     | 5.4.1    | Characterization: Experimental Details and Results                           | 141 |

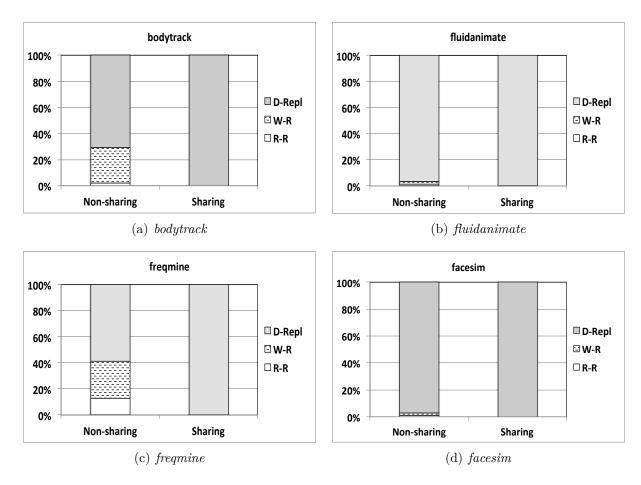

|   |     | 5.4.2    | Characterization: Discussion and Summary                                     | 146 |

|   |     |          | Mapping: Experimental Details and Results                                    | 149 |

|   |     |          | Mapping: Discussion and Statistical Analyses                                 | 154 |

|   | 5.5 |          | · · · · · · · · · · · · · · · · · · ·                                        | 155 |

Contents k

| 6  |       | _        | Sense for Performance and Reliability Integration                                           | 158 |

|----|-------|----------|---------------------------------------------------------------------------------------------|-----|

|    | 6.1   |          |                                                                                             | 158 |

|    | 6.2   |          | cterization for Resource Contention and Vulnerability                                       | 161 |

|    |       | 6.2.1    | Characterization Metric                                                                     | 161 |

|    |       | 6.2.2    | Characterization Methodology                                                                | 162 |

|    |       | 6.2.3    | SensitivityScore <sub>integrated</sub> : Sensitivity Scores for Performance and Reliability | 162 |

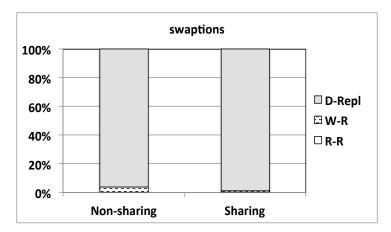

|    | 6.3   | Mappi    | ng Co-located Multi-threaded Applications for Performance and Relia-                        |     |

|    |       |          | Trade-off                                                                                   | 165 |

|    |       | 6.3.1    | The ReSensor <sub>I</sub> Thread-mapping Algorithm                                          | 165 |

|    |       | 6.3.2    | The ReSense <sub>Integrated</sub> Run-time System                                           | 171 |

|    | 6.4   |          | ation of the Integrated Instance                                                            | 172 |

|    | 0.1   | 6.4.1    | Characterization: Integrated Characteristics of the PARSEC benchmark                        |     |

|    |       | 6.4.2    | Mapping: Experimental Results and Analyses                                                  | 174 |

|    | 6.5   |          | ary                                                                                         | 179 |

| 7  | Con   | nclusion | and Future Work                                                                             | 182 |

|    | 7.1   |          | ary of the Contributions                                                                    | 182 |

|    |       | 7.1.1    | The ReSense Framework                                                                       | 182 |

|    |       | 7.1.2    | ReSense Performance: The Performance Instance of ReSense                                    | 183 |

|    |       | 7.1.3    | ReSense_Reliability: The Reliability Instance of ReSense                                    | 185 |

|    |       | 7.1.4    | ReSense_Integration: The Integrated Performance and Reliability                             |     |

|    |       | ,,_,_    | Instance of ReSense                                                                         | 187 |

|    | 7.2   | Future   | e Work                                                                                      | 188 |

|    |       | 7.2.1    | Applying the framework to other instances                                                   | 189 |

|    |       | 7.2.2    | Phase-level characterization                                                                | 189 |

|    |       | 7.2.3    | Instance for minimizing vulnerability of micro-architectural resources                      | 100 |

|    |       | 1.2.0    | and write-though caches                                                                     | 190 |

|    |       | 7.2.4    | Combine techniques for vulnerability minimization                                           | 191 |

|    |       | 7.2.5    | Model CVF on real hardware                                                                  | 192 |

|    |       | 7.2.6    | Different variations of the integrated instance                                             | 192 |

| Bi | bliog | graphy   |                                                                                             | 193 |

# List of Tables

| 1.1  | Targeted problems on modern CMPs to be addressed using the ReSense framework                         | 14  |

|------|------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Comparison between ReSense_Performance and some state-of-the-art systems                             | 25  |

| 4.1  | Configuration of the experimental platforms                                                          | 73  |

| 4.2  | Characterization configurations on the experimental platforms                                        | 78  |

| 4.3  | Summary of the intra-application contention results for the PARSEC benchmarks                        | 96  |

| 4.4  | Summary of the intra-application contention results for the NPB benchmarks                           | 97  |

| 4.5  | Summary of the inter-application contention results for the PARSEC benchmarks                        | 98  |

| 4.6  | SensitivityScore <sub>performance</sub> of the PARSEC benchmarks                                     | 99  |

| 4.7  | SensitivityScore <sub>performance</sub> of the NPB benchmarks                                        | 99  |

| 4.8  | Small and Medium Dynamic Workload Set                                                                | 103 |

| 4.9  | Large Dynamic Workload Set                                                                           | 107 |

| 4.10 | Confidence interval of performance improvements for three workloads                                  | 109 |

| 4.11 | Average performance improvements (positive values) or degradation (negative                          |     |

|      | values) over the native OS, for thread-mappings using fixed positive, fixed                          |     |

|      | negative and characterization-based SensitivityScores <sub>performance</sub>                         | 114 |

| 5.1  | Simics configuration for the targeted experimental platform                                          | 140 |

| 5.2  | Characterization summary of the PARSEC benchmarks                                                    | 147 |

| 5.3  | SensitivityScore <sub>CVF</sub> of the PARSEC benchmarks                                             | 148 |

| 6.1  | SensitivityScore <sub>performance</sub> and SensitivityScore <sub>CVF</sub> of the PARSEC benchmarks |     |

|      | •                                                                                                    | 172 |

| 6.2  | SensitivityScore <sub>integrated</sub> of the PARSEC benchmarks for L2-cache using differ-           |     |

|      |                                                                                                      | 173 |

| 6.3  | Experimental results showing $CVF_{mc-avq}$ and total response time for a four-                      |     |

|      | application PARSEC workload in different mapping configurations for $w_P =$                          |     |

|      |                                                                                                      | 179 |

|      |                                                                                                      |     |

# List of Figures

| 1.1   | Shared cache contention for a workload with single- and multi-threaded applications ( $CX$ stands for the processor core, $L1$ and $L2$ stand for L1- and L2-caches, respectively.) | 4   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2   | Mapping to mitigate shared-cache contention for a workload with two multi-<br>threaded applications                                                                                 | 9   |

| 1.3   | Mapping to reduce application vulnerability to soft errors                                                                                                                          | 10  |

| 3.1   | Components of the ReSense framework                                                                                                                                                 | 36  |

| 3.2   | Configurations to characterize a multi-threaded application L2-cache contention                                                                                                     | 41  |

| 3.3   | Mapping decision for two problems                                                                                                                                                   | 46  |

| 3.4   | An operational overview of ReSense                                                                                                                                                  | 49  |

| 4.1   | Components of the ReSense_Performance Instance                                                                                                                                      | 53  |

| 4.2   | Mapping decision for the two scenarios                                                                                                                                              | 63  |

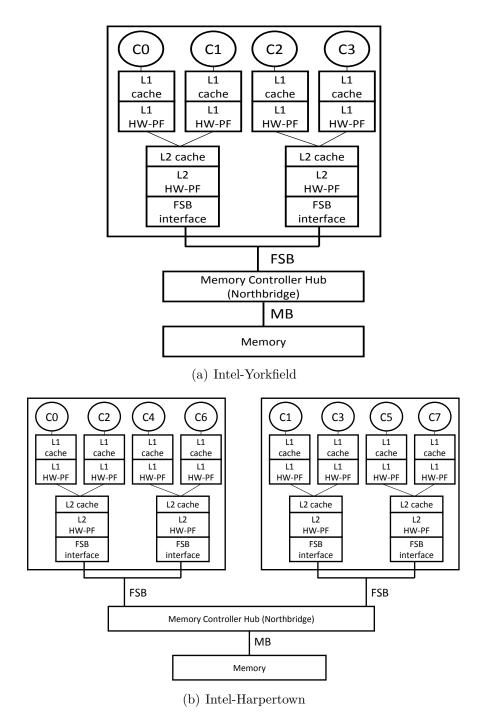

| 4.3   | Experimental Platforms ( $CX$ stands for the processor core, $L1$ $HW$ - $PF$ and $L2$ $HW$ - $PF$ stand for hardware prefetcher for L1- and L2-caches, respectively                |     |

|       | and $FSB$ and $MB$ stand for Front Side Bus and Memory Bus, respectively.) .                                                                                                        | 68  |

| 4.4   | Topology of Experimental Platforms                                                                                                                                                  | 72  |

| 4.5   | Configurations to characterize a multi-threaded application for intra-application                                                                                                   |     |

|       | L1-cache contention                                                                                                                                                                 | 73  |

| 4.6   | Configurations to characterize a multi-threaded application for intra-application L2-cache contention                                                                               | 74  |

| 4.7   | Configurations to characterize a multi-threaded application for intra-application                                                                                                   |     |

|       | FSB contention                                                                                                                                                                      | 75  |

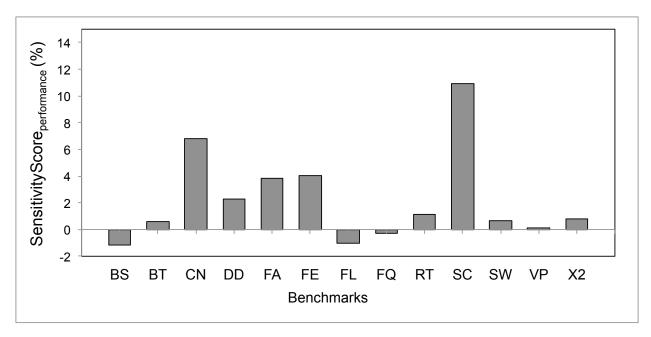

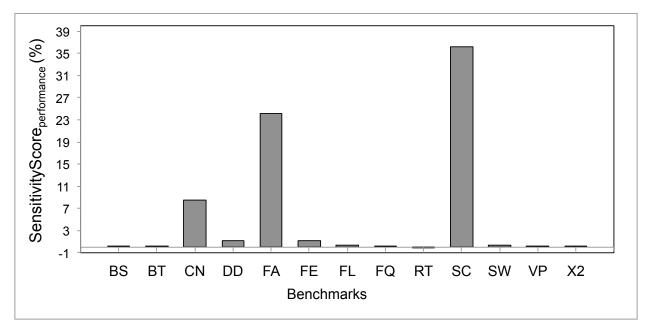

| 4.8   | Characterization results of the PARSEC benchmarks for intra-application                                                                                                             |     |

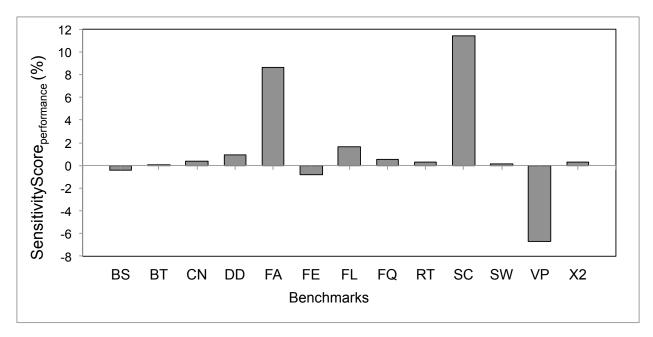

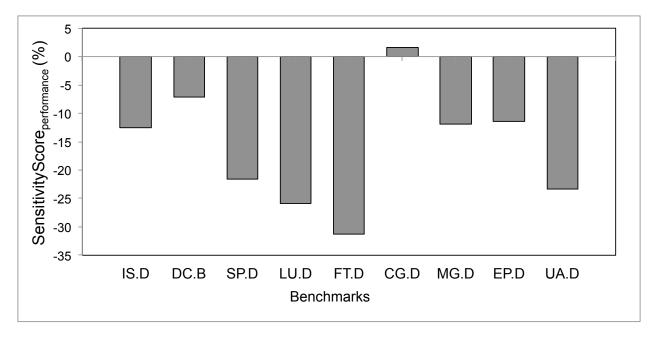

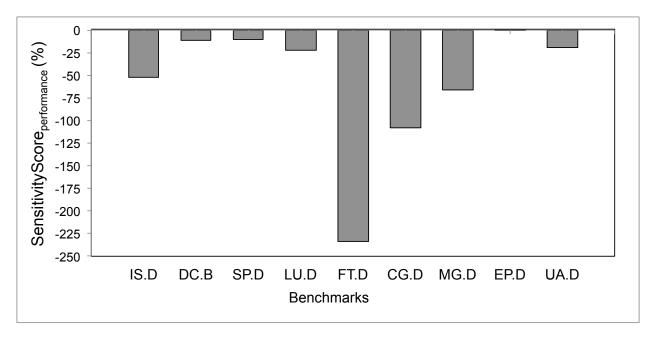

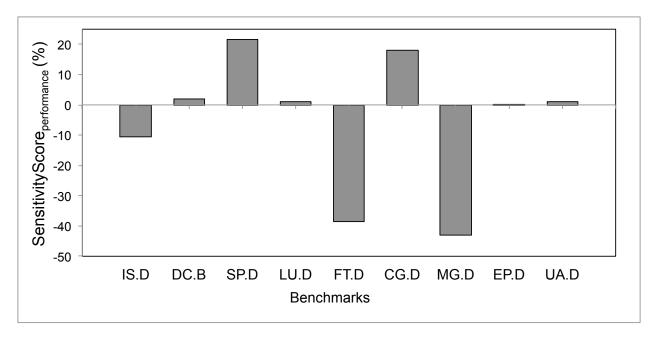

|       | L1-cache contention, represented as SensitivityScore <sub>performance</sub>                                                                                                         | 79  |

| 4.9   | Characterization results of the PARSEC benchmarks for intra-application                                                                                                             |     |

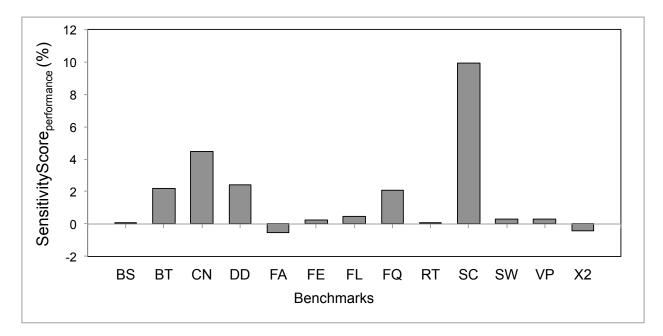

|       | L2-cache contention, represented as SensitivityScore <sub>performance</sub>                                                                                                         | 80  |

| 4.10  | 1 1                                                                                                                                                                                 | 0.1 |

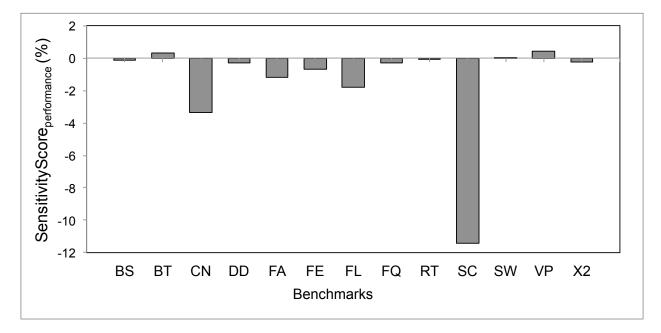

| 1 1 1 | contention, represented as SensitivityScore <sub>performance</sub>                                                                                                                  | 81  |

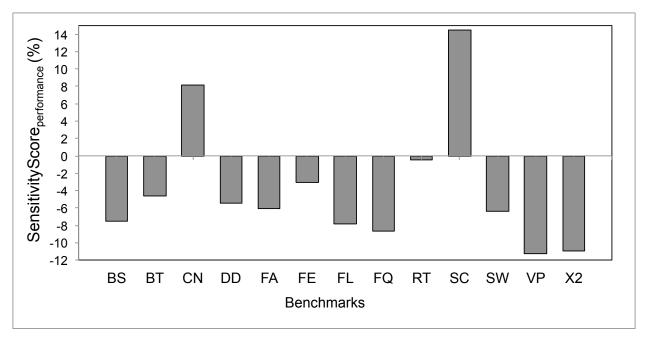

| 4.11  | Characterization results of the PARSEC benchmarks for intra-application                                                                                                             | ดก  |

| 1 10  | on-chip memory controller contention, represented as SensitivityScore <sub>performance</sub> Characterization results of the NPB benchmarks for intra-application on-chip           | 82  |

| 4.12  | memory controller contention represented as SensitivityScore accounts                                                                                                               | 83  |

|       |                                                                                                                                                                                     |     |

List of Figures n

| 4.13 | Characterization results of the PARSEC benchmarks for intra-application L3-cache contention, represented as SensitivityScore <sub>performance</sub>                                                    | 84  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.14 | Characterization results of the NPB benchmarks for intra-application L3-cache contention, represented as SensitivityScore <sub>performance</sub>                                                       | 85  |

| 4.15 | Characterization results of the PARSEC benchmarks for intra-application memory socket contention, represented as SensitivityScore <sub>performance</sub>                                               | 85  |

| 4.16 | Characterization results of the NPB benchmarks for intra-application memory socket contention, represented as SensitivityScore <sub>performance</sub>                                                  | 86  |

| 4.17 | Configurations to characterize a multi-threaded application for inter-application L1-cache contention                                                                                                  | 87  |

| 4.18 | Configurations to characterize a multi-threaded application for inter-application L2-cache contention                                                                                                  | 88  |

| 4.19 | Configurations to characterize a multi-threaded application for inter-application FSB contention                                                                                                       | 90  |

| 4.20 | Characterization results of the PARSEC benchmarks for inter-application contention for L1-cache                                                                                                        | 92  |

| 4.21 | Characterization results of the PARSEC benchmarks for inter-application contention for L2-cache                                                                                                        | 94  |

| 4.22 | Characterization results of the PARSEC benchmarks for inter-application contention for FSB                                                                                                             | 95  |

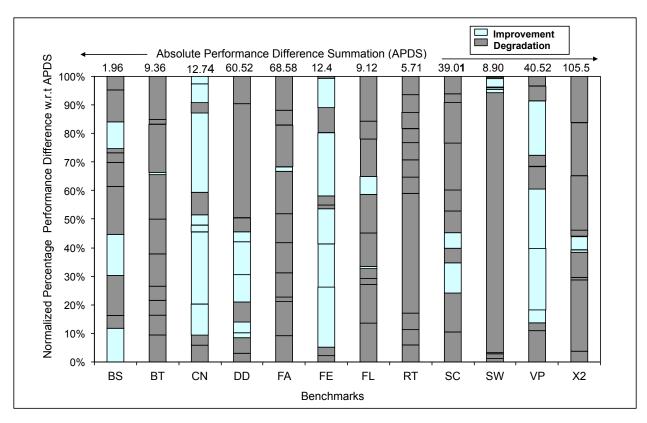

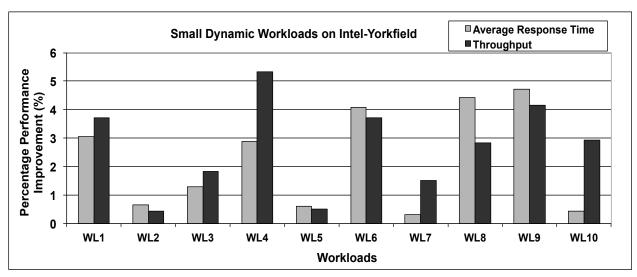

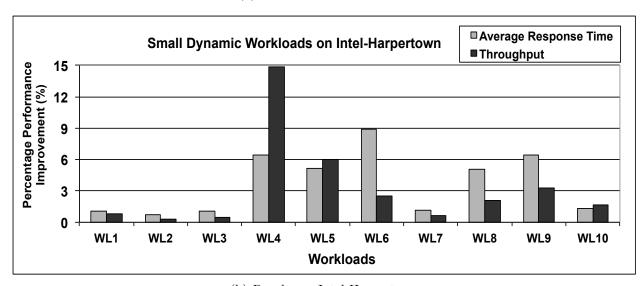

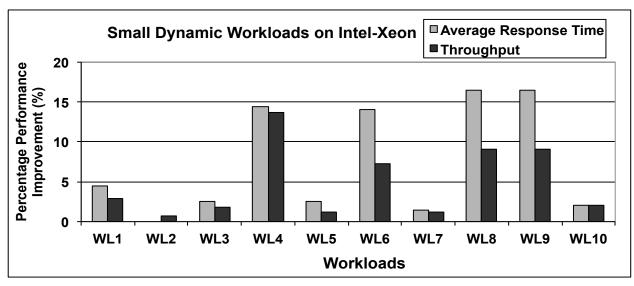

| 4.23 | Performance results of <i>Small</i> Dynamic Workloads, normalized to the native OS (ReSense <sub>Performance</sub> performs better than the OS)                                                        | 102 |

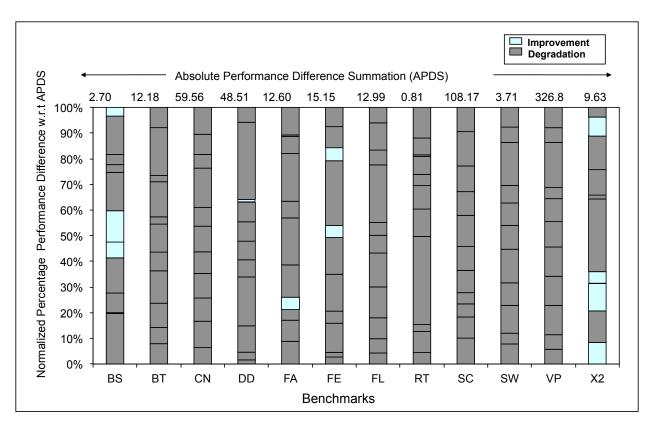

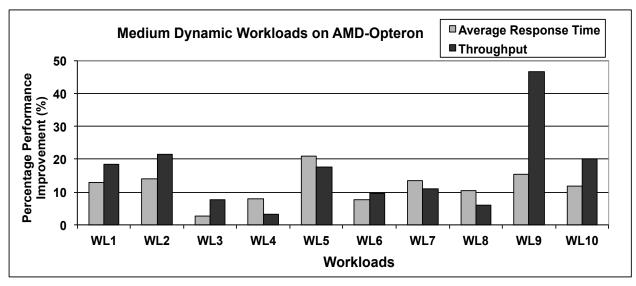

| 4.24 | Performance results of <i>Small</i> Dynamic Workloads, normalized to the native OS (ReSense <sub>Performance</sub> performs better than the OS)                                                        | 104 |

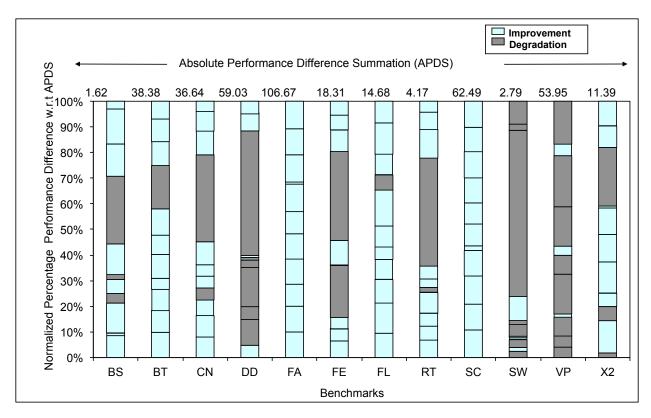

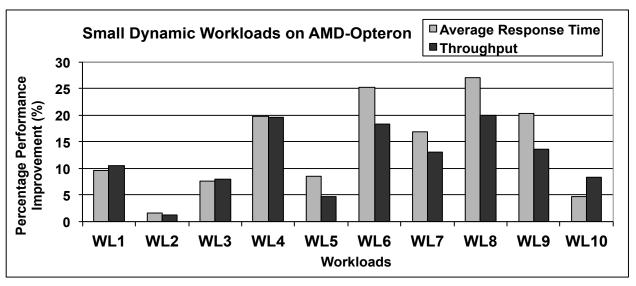

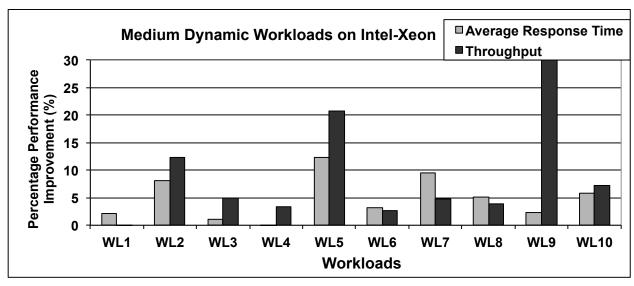

| 4.25 | Performance results for <i>Medium</i> Dynamic Workloads, normalized to the native OS (ReSense <sub>Performance</sub> performs better than the OS)                                                      | 106 |

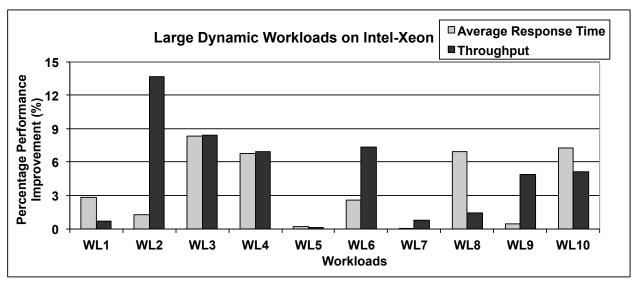

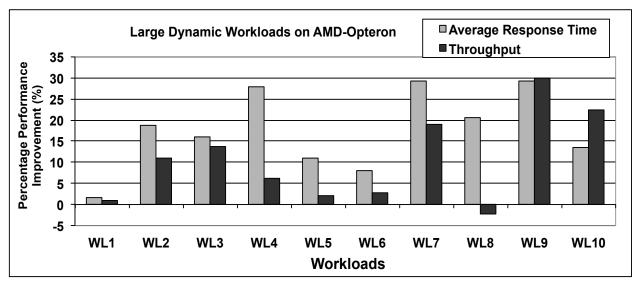

| 4.26 | Performance results for <i>Large</i> Dynamic Workloads, normalized to the native OS (ReSense <sub>Performance</sub> performs better than the OS)                                                       | 108 |

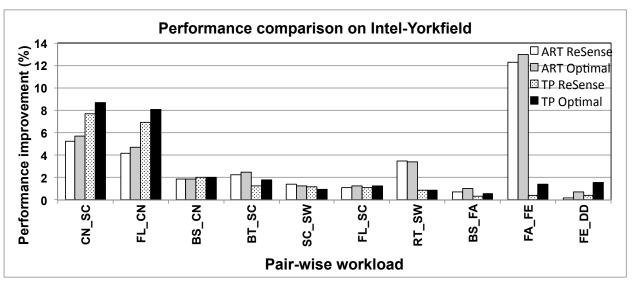

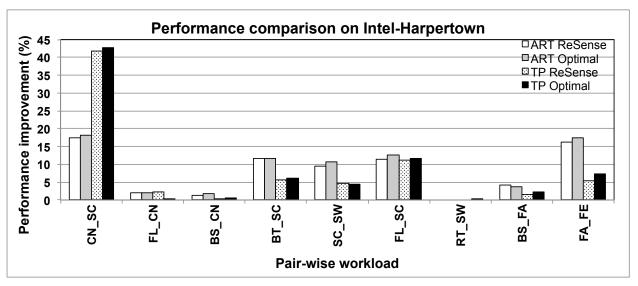

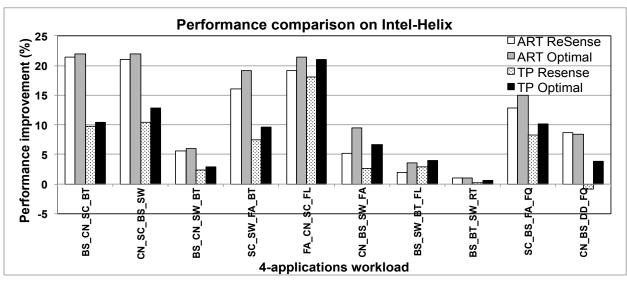

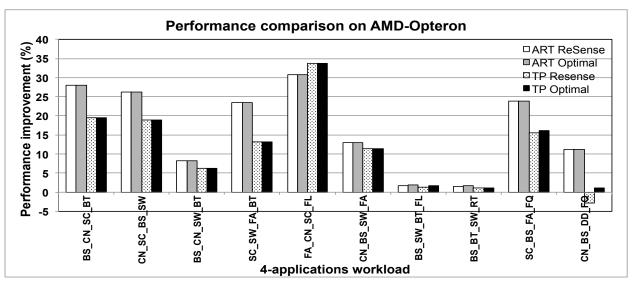

| 4.27 | Performance comparison between ReSense <sub>Performance</sub> and experimentally determined Optimal thread-mapping for pair-wise workloads, normalized to the native OS                                | 111 |

| 4.28 | Performance comparison between ReSense <sub>Performance</sub> and experimentally determined Optimal thread-mapping for 4-applications Workloads, normalized to the native OS                           | 113 |

| 5.1  | Components of the ReSense_Reliability Instance                                                                                                                                                         | 121 |

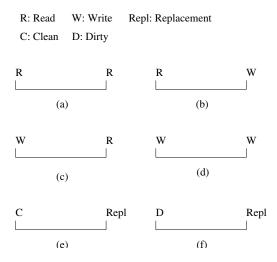

| 5.2  | Access patterns (intervals) of cache lines (a) Read-Read pattern (b) Read-Write pattern (c) Write-Read pattern (d) Write-Write Pattern (e) Clean-Replacement pattern (f) Dirty-Replacement pattern [1] | 124 |

| 5.3  | Configurations to characterize a multi-threaded application for vulnerability to soft errors in shared L2-cache                                                                                        | 129 |

| 5.4  | Mapping decision for the two cases in Scenario 1                                                                                                                                                       | 134 |

| 5.5  | Mapping decision for the two cases in Scenario 2                                                                                                                                                       | 137 |

List of Figures o

| 5.6  | Experimental results of vulnerability characterizations of the PARSEC benchmarks for a write-back shared L2-cache, represented as SensitivityScore <sub>CVF</sub> . Negative values mean increased $CVF_{mc}$ , positive values mean decreased $CVF_{mc}$ |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | in the sharing configuration                                                                                                                                                                                                                              | 142  |

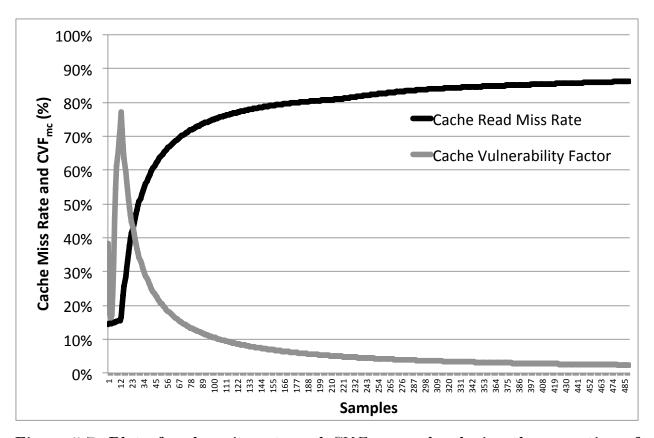

| 5.7  | Plot of cache miss rate and $CVF_{mc}$ samples during the execution of streamcluster                                                                                                                                                                      | -143 |

| 5.8  | Percentage ACE lifetime intervals during the execution of $swaptions$                                                                                                                                                                                     | 144  |

| 5.9  | Percentage ACE lifetime intervals during the execution of the applications .                                                                                                                                                                              | 146  |

| 5.10 | Configurations for mapping two multi-threaded applications, each with two                                                                                                                                                                                 |      |

|      | threads                                                                                                                                                                                                                                                   | 151  |

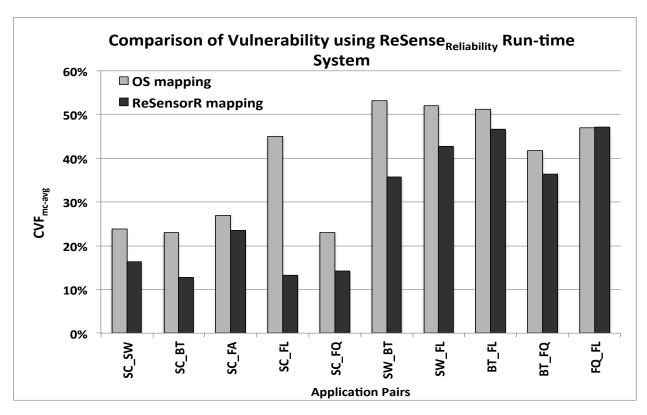

| 5.11 | Experimental results showing average $CVF_{mc}$ of the shared caches for pairs of PARSEC application for ReSensor <sub>R</sub> and OS mapping (Lower bar is better).                                                                                      | 152  |

| 6.1  | Components of the ReSense_Integration Instance                                                                                                                                                                                                            | 160  |

| 6.2  | Mapping decisions for the two examples in Scenario 1                                                                                                                                                                                                      | 168  |

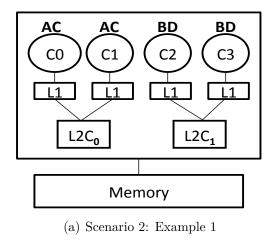

| 6.3  | Mapping decision for an example in Scenario 2                                                                                                                                                                                                             | 170  |

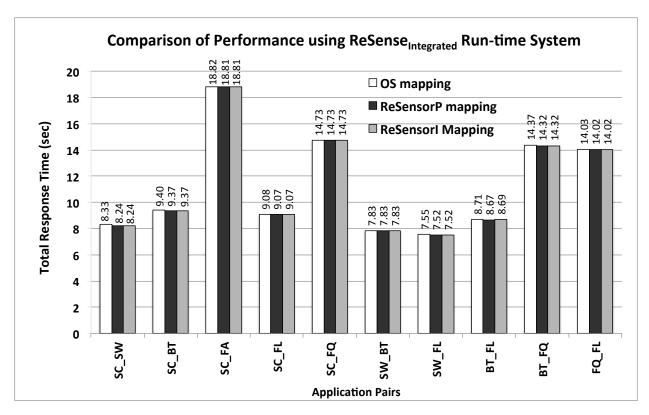

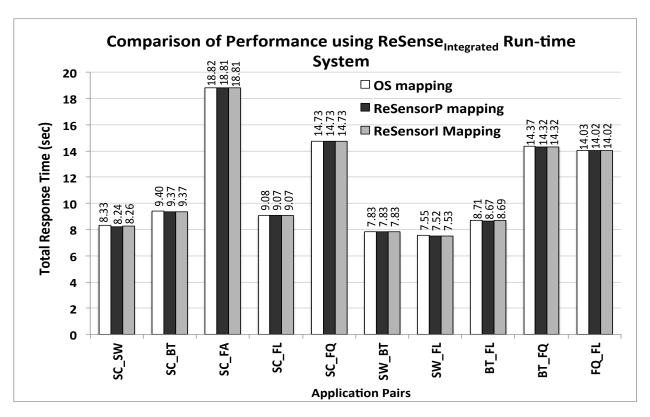

| 6.4  | Experimental results showing total response time for the pairs of PARSEC application using OS, ReSensor <sub>P</sub> and ReSensor <sub>I</sub> mapping for $w_P = 0.99$ and $w_R = 0.01$ (Lower bar is better)                                            | 175  |

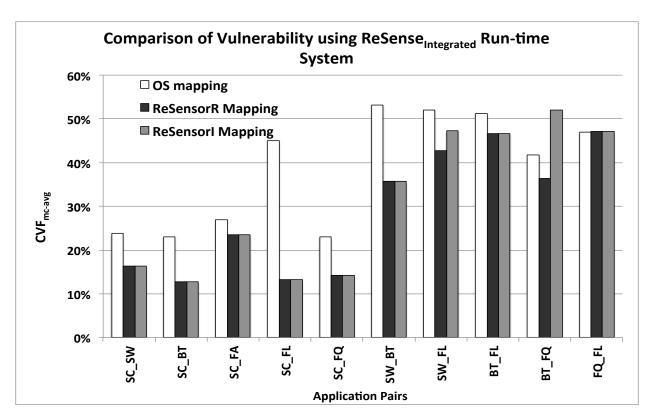

| 6.5  | Experimental results showing average $CVF_{mc}$ of the shared caches for pairs of PARSEC application using OS, ReSensor <sub>R</sub> and ReSensor <sub>I</sub> mapping for $w_P =$                                                                        |      |

|      | 0.99 and $w_R = 0.01$ (Lower bar is better)                                                                                                                                                                                                               | 176  |

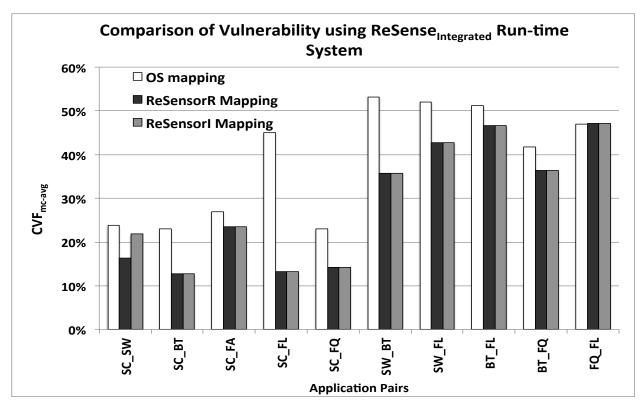

| 6.6  | Experimental results showing average $CVF_{mc}$ of the shared caches for pairs of PARSEC application in OS, ReSensor <sub>R</sub> and ReSensor <sub>I</sub> mapping for $w_P = 0.30$                                                                      |      |

|      | and $w_R = 0.70$ (Lower bar is better)                                                                                                                                                                                                                    | 177  |

| 6.7  | Experimental results showing total response time for the pairs of PARSEC application in OS, ReSensor <sub>P</sub> and ReSensor <sub>I</sub> mapping for $w_P = 0.30$ and $w_R = 0.70$ (Lower bar is better)                                               | 178  |

|      |                                                                                                                                                                                                                                                           |      |

List of Figures p

# Chapter 1

## Introduction

Chip-multiprocessors (CMPs) have become ubiquitous in modern computing and the mainstream architecture for various platforms, including laptops, desktops, and large server machines. These CMP machines are very powerful and useful for solving computationintensive problems and provide high throughput through their instruction- and thread-level parallelism capabilities.

## 1.1 Challenges in Multicore Systems

### 1.1.1 Complex and Dynamic Workloads

As technology scaling continues and more transistors are accommodated on the chip, the number of cores on CMPs is growing, and multicore machines are scaling up to many-core machines. Because of CMP scaling, the trend of application design has shifted towards multi-threaded and parallel programming. To fully exploit the available computational resources, workloads, which consist of multiple multi-threaded applications, are executed. Each application uses the underlying resources differently depending on how the application threads are mapped to the available cores. Furthermore, the way the applications use different resources has an impact on the workload's execution and overall resource management, which can lead to performance optimization, reliability improvement, power consumption, and

thermal problems on CMPs. The continuous change in the execution environment caused by dynamic workloads, where any number of multi-threaded applications arrive, execute, and terminate in unpredictable ways, makes these problems especially challenging and difficult to address.

As multicore machines continue to scale up, the performance and reliability challenges on these architectures are becoming more severe because of the increased criticality of shared-resource contention and soft errors [2, 3]. To realize the full potential of CMP platforms, we need to ensure that multi-threaded workloads not only execute efficiently and fast, but also correctly. The following two sections describe the resource contention and soft error problems in more detail.

#### 1.1.2 Resource Contention

There are various resources in CMPs that are shared by several and/or all processing cores, including on-chip shared and last-level caches (LLC), front side bus (FSB), memory bus, disk, and I/O-devices. When there are multiple multi-threaded applications executing on CMPs, there is increased contention among the applications for these shared resources. Shared-resource contention is a phenomenon that occurs when an application shares any resource (e.g., last-level cache) with its co-runner<sup>1</sup>. Because of contention, especially for the resources in the memory hierarchy, an application's performance can degrade by more than 50% [4], and scalable performance improvement is often not achieved on multicore and many-core machines [5]. Contention for the shared resources in the memory hierarchy can also lead to inefficient resource usage [3, 6].

Because of the resource usage behaviors, contention for the shared-memory resources created by multi-threaded applications in a workload can be severe for two reasons. First, a multi-threaded application can use more than one shared resource in the memory hierarchy, which increases the degree of contentiousness. Consider the contention problem for a shared

<sup>&</sup>lt;sup>1</sup>A co-runner is a thread from a different application, which executes on the same or neighboring core and shares any resource.

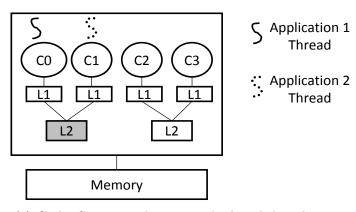

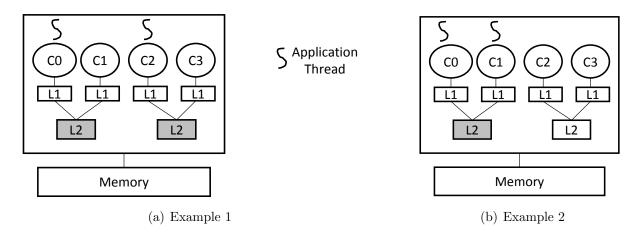

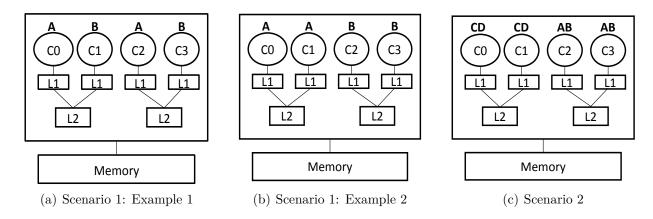

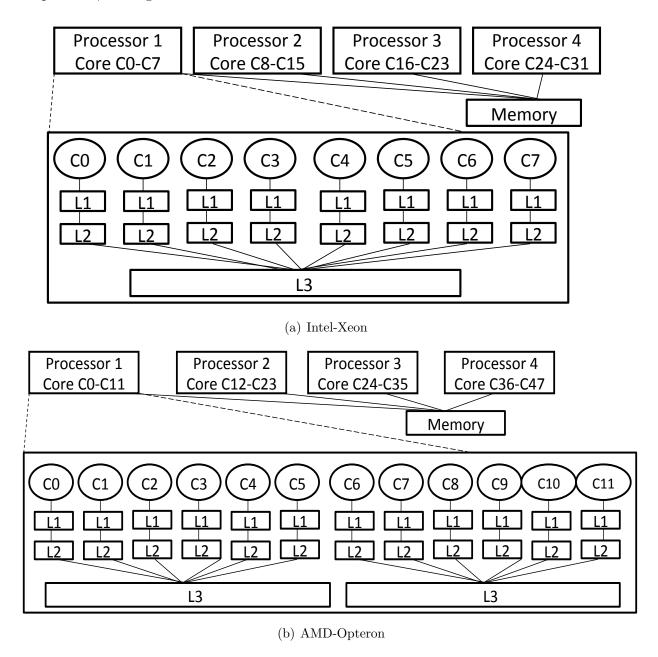

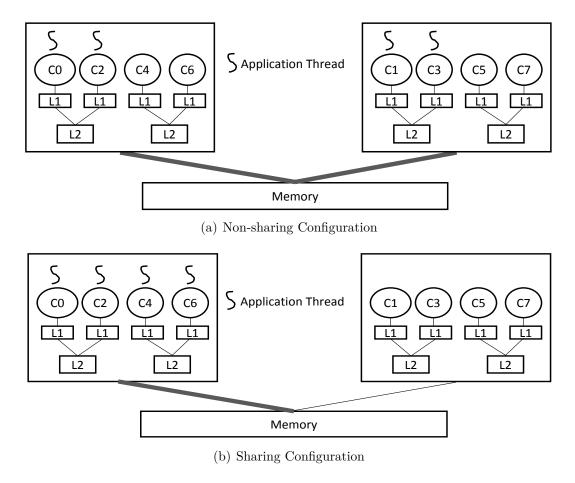

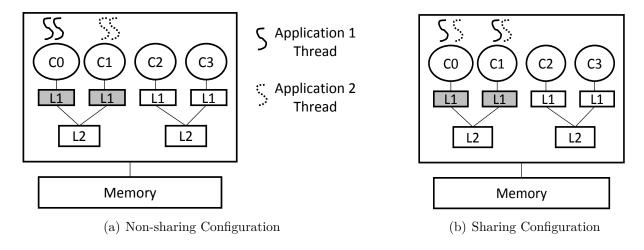

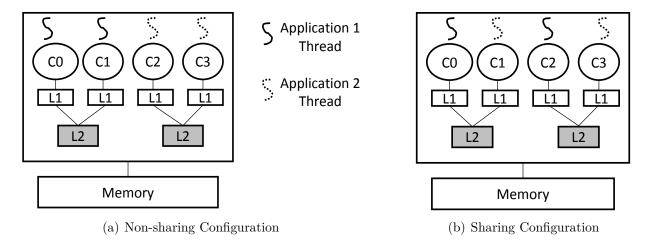

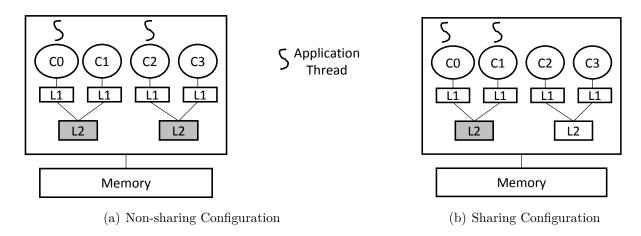

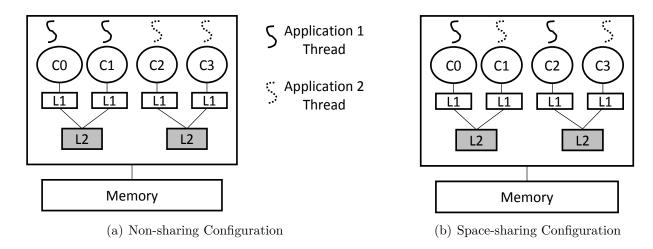

L2-cache, which is one of the resources in the memory hierarchy. When two single-threaded applications in a workload share the same L2-cache (Figure 1.1(a)), the application that accesses L2-cache frequently can increase the cache contention and severely degrade the other application's performance. If the workload has two multi-threaded applications and the threads from one application share the same L2-cache with the other application's threads (Figure 1.1(b)), the cache contention created in two L2-caches by the cache-intensive application can also degrade the workload's overall performance. Second, the application threads can contend for the shared-memory resources among themselves even when the application runs solely. If the workload has only one multi-threaded application, the sibling threads<sup>2</sup> can contend for the shared L2-cache (Figure 1.1(c)) and degrade the application's performance. On the other hand, if the sibling threads share data, then sharing the same cache improves the application performance [7]. Thus a multi-threaded application's resource usage and inherent characteristics can impact the severity of resource contention and affect the workload's performance.

There has been significant research efforts to address shared-resource contention via both hardware and software techniques. Hardware techniques can provide performance improvement [8, 9]; however, they are hard to implement in practice, and existing hardware solutions might become obsolete or ineffective for emerging and new application behaviors. Several research efforts have addressed shared-resource contention via software techniques, including execution throttling, thread-mapping, and scheduling [6, 4, 10]. However, to the best of our knowledge, these efforts have not considered multi-threaded applications.

There are several differences between the characteristics of single- and multi-threaded applications as they contend for the shared resources. A single-threaded application can have one co-running thread on a neighboring core when it shares, for example, a L2-cache, as shown in Figure 1.1(a). Consequently, it contends for cache resources with that co-runner. On the other hand, a multi-threaded application can share multiple caches with multiple

<sup>&</sup>lt;sup>2</sup>Sibling threads are defined as the threads that are created from the same multi-threaded application.

- (a) Cache Contention by two single-threaded applications

- (b) Contention by two multi-threaded applications

(c) Contention by one multi-threaded application

Figure 1.1: Shared cache contention for a workload with single- and multi-threaded applications (CX stands for the processor core, L1 and L2 stand for L1- and L2-caches, respectively.)

co-running threads, as shown in Figure 1.1(b), and contend for more than one cache with a multi-threaded co-runner. Moreover, multi-threaded applications can have contentious behavior among its own threads even when they do not have any co-runner [5], as shown in Figure 1.1(c). In addition, single-threaded applications do not have data sharing, whereas, multi-threaded applications can have data sharing [11]. In short, multi-threaded applications suffer from shared-resource contention differently than single-threaded applications, for both solo-execution and execution with co-runner(s). Existing techniques to address resource contention do not consider these differences and are thus not applicable for mitigating contention created by multi-threaded applications.

There are several challenges to mitigating contention created by simultaneously executing multi-threaded applications on CMPs. A multi-threaded application can suffer from contention created by its own sibling threads and by threads from co-running application(s). For workloads with multiple multi-threaded applications, mitigating contention depends on an application's characteristics, underlying resource topology of the platform, and importantly on the characteristics of the co-running application(s). Contention mitigation becomes more challenging for dynamic workloads. The continuous change in the execution environment created by the dynamic workloads with increasing and decreasing numbers of applications, arriving and terminating in unpredictable ways, makes contention mitigation even more challenging and difficult. Because of the dynamic nature of this problem and emerging workloads, contention mitigation is ideally done dynamically using software techniques based on the characteristics of the currently executing applications in the workload and the run-time environment.

#### 1.1.3 Soft Errors

As the technology scaling continues, the size of the transistors shrinks each process generation, and the reliability of CMP platforms is becoming another critical issue [2, 12]. In particular, systems are increasingly susceptible to transient faults or soft errors. Soft errors are faults that occur randomly caused by various sources, including cosmic rays, power supply noise, and packaging defects. Soft errors do not cause permanent damage to any hardware component, but potentially cause applications to execute incorrectly and output wrong results. Soft errors affect a system's reliability with respect to micro-architectural resources, such as load-store unit (LSU), re-order buffer (ROB), instruction queue (IQ), as well as memory resources, such as caches [13]. The occurrence rate of these soft errors increases as multicore machines continue to scale up to many-core machines and the total bit count on these platforms increases, posing a significant risk for these computing platforms.

An application's resource usage can lead to vulnerable execution and have an impact on

reliability [13, 14]. If an application occupies a particular resource for a long time during its execution, then the long resource occupancy makes the application more vulnerable to soft errors caused by high energetic beam particles [15]. Such errors can change an application's execution and result in visible errors and incorrect output, reducing application reliability on the system. For example, if an application uses data from any resource very frequently and executes for a longer time than an application with a shorter execution time, then the data used by the long running application has a higher probability of being corrupted because of its susceptibility to soft errors.

Additionally, because a multi-threaded application uses multiple resources, it is more susceptible to soft errors. For example, each single-threaded application in a workload uses only one L1-cache (Figure 1.1(a)). On the other hand, the siblings threads from a multi-threaded application use two L1-caches in Figure 1.1(c). Thus, the multi-threaded application has twice the probability of being affected by soft errors in L1-caches than the single-threaded applications. Fundamentally, the resource usage characteristics of the multi-threaded applications, in terms of both duration and number of resources, can make the soft error problem on a multicore machine even more critical for a workload.

There has been much research effort addressing soft errors using both hardware and software techniques. Hardware techniques typically include redundant bits and device hardening to protect against soft errors. However, these techniques have significant power, area, cost, and latency overhead, which are not suitable for systems with large numbers of cores [16, 17]. Software techniques utilize redundant executions to ensure reliable execution. However, this mechanism has a very high performance overhead [18]. Other software techniques include compilation to reduce an application's susceptibility to soft errors [19]. Soft errors can affect an application's output during its execution, and the sensitivity to soft errors in modern systems is application dependent [13]. Therefore, dynamic and lightweight software measures that leverage application characteristics are more effective than the static compilation techniques in reducing application vulnerability to soft errors.

In general, addressing soft errors via a dynamic software technique is challenging for several reasons. First, soft errors corrupt the contents in the hardware units, which are used by the applications during their executions and can potentially result into visible errors. The software technique must be able to monitor the applications' executions continuously to detect such corrupted data usage by the applications, which can incur high overhead. Second, the software technique should reduce an application's susceptibility to soft errors so that the number of potential visible errors is minimized. Therefore, the technique should use a metric that represents and quantifies the probability of an application being affected by soft errors while it is still in execution. Determining this metric should be done accurately so that the software technique can effectively take measures to reduce the probability of soft errors affecting the application execution. Third, the effect of soft errors varies across applications and is dynamic, depending on the occupancy duration of a particular hardware resource by the applications in a workload [19]. Therefore, an effective software technique must be able to control the occupancy duration of the resources as the applications execute.

## 1.2 Application-driven Thread-mapping

An application's inherent characteristics of resource usage can impact both performance and reliability on multicore platforms. If an application in a workload uses a particular resource excessively, then this contentious behavior degrades the workload's performance when it shares the resources with its co-runners. If an application occupies a resource for a longer period of time, then the execution becomes highly vulnerable to soft errors, and the probability of visible errors becomes very high.

The performance and reliability challenges on a multicore platform can be addressed effectively by taking into consideration how the characteristics of the applications in a workload affect these problems of resource contention and soft errors, respectively. A characterization technique would be useful to identify the application behaviors for resource usage that are critical to address a targeted problem. The insights from such characterization and analyses

can be used to control the resource usage of the applications by intelligently mapping them on the appropriate cores such that the objective for the targeted problem is obtained.

For the resource contention problem, a contentious application in a workload can be identified by analyzing its resource usage behavior. Once the contentious application(s) is(are) identified, all the threads from a workload can be mapped such that the resource contention is mitigated and the contentious threads have minimal impact on the workload's performance, i.e., response time and throughput.

For the soft errors problem, a highly vulnerable application to soft errors can be identified by performing its resource occupancy behavior analyses. Once the highly vulnerable application(s) is(are) identified in a workload, the resource occupancy in the targeted resources can be reduced by mapping the application threads such that the overall vulnerability to soft errors is minimized.

Furthermore, this approach of mapping applications using prior characterization generalizes and can be used to improve performance and reliability for complex, dynamic workloads. Once the application characteristics are understood and identified, then as the applications start and finish their executions in a dynamic workload, thread-mapping can be used to adjust the resource usage of the currently executing applications to achieve the performance and/or reliability objective.

#### 1.2.1 Contention/Performance Example

We describe two examples of how application characteristics can be used to address a resource contention problem - specifically cache contention. To achieve the goal of contention mitigation, application threads can be mapped appropriately by understanding their cache contentious behaviors.

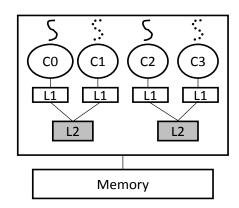

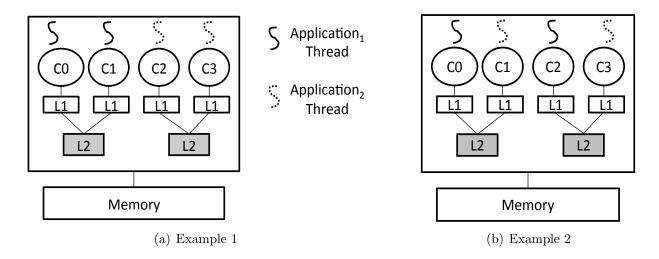

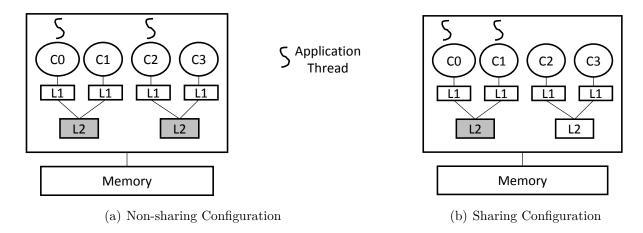

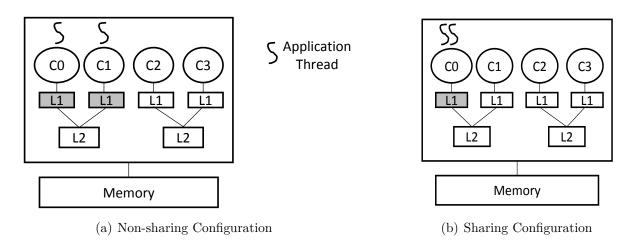

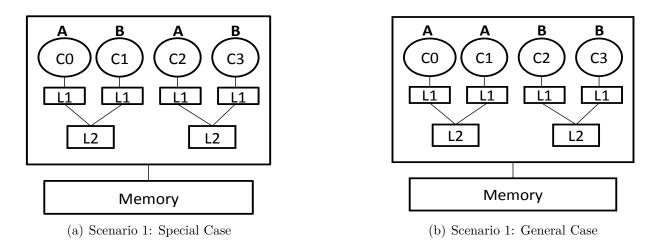

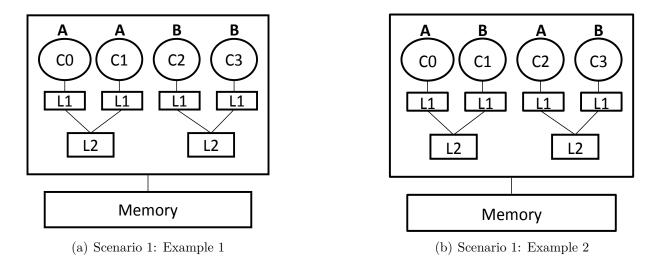

Consider a workload that has two multi-threaded applications, and one of the applications,  $Application_1$ , has severe cache contention among its siblings threads. For the first example, if the second application,  $Application_2$ , of the workload has shared data among its sibling

Figure 1.2: Mapping to mitigate shared-cache contention for a workload with two multi-threaded applications

threads, then the threads from  $Application_1$  and  $Application_2$  should be mapped such that each application uses its own L2-cache (shown in Figure 1.2(a)). This mapping ensures resource isolation so that the contentiousness from one application does not affect the cache sharing of the other application.

When such resource isolation is not possible, an application's sensitivity to the targeted resource, based on its characterization, can be used to determine the effective mapping, e.g., the most cache-intensive application can be mapped with the least cache-intensive application to share the same last-level cache [4]. For the second example, if  $Application_2$  is computation-intensive (does not contend for cache), then the threads should be mapped such that the cache-intensive  $Application_1$  threads share the same cache with the computation-intensive  $Application_2$  threads (shown in Figure 1.2(b)). As  $Application_2$  does not have much cache usage, this mapping would not degrade its performance significantly; however, it would mitigate contention for the cache-intensive application and improve its performance.

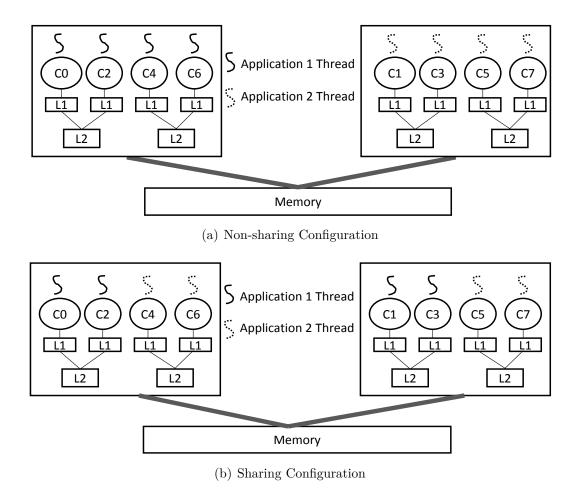

### 1.2.2 Soft Error Example

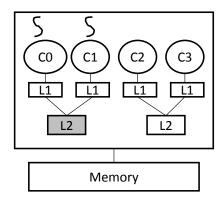

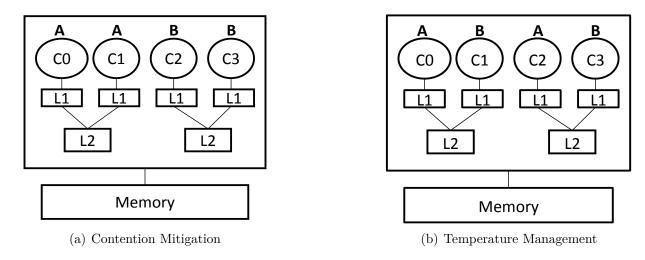

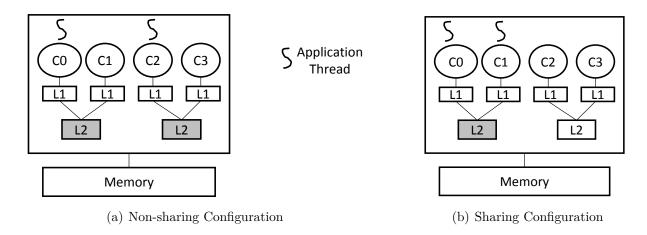

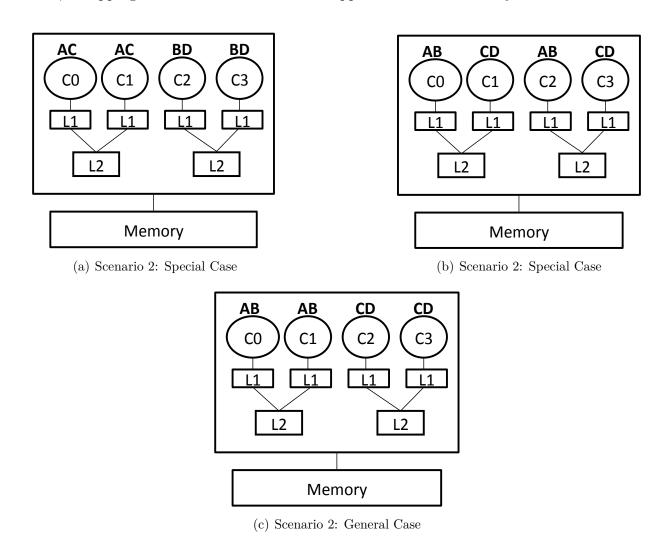

We now describe how an application's resource usage can be used to reduce its vulnerability to soft errors. Consider a workload with one multi-threaded application that executes for

Figure 1.3: Mapping to reduce application vulnerability to soft errors

a long time, and the application does not use the cache resources very frequently. If the application threads are mapped to use two separate caches (shown in Figure 1.3(a)), then the data in the two caches remain resident for a long period of time, and the application becomes more vulnerable to soft errors. This vulnerability can be decreased if the threads are mapped to use the same cache (shown in Figure 1.3(b)). This mapping can increase the cache miss rate, which lowers the residency time of the data and reduces the probability of being affected by soft errors. As a result, higher probability of correct application execution and output is obtained by this mapping.

To summarize, on a multicore platform, a multi-threaded application's characteristics and behaviors can be used to guide how to map application threads from a workload to improve performance and reliability.

#### 1.3 The ReSense Framework

For the thread-mapping algorithm to be effective, it is critical to determine the applications' behaviors that affect the goal, i.e., mitigating contention and reducing occupancy duration in targeted resources (see Table 1.1). Determining such application behavior can be done *online* when the workload executes, by varying the resource usage for an application and analyzing how it affects the objective in the presence of co-runner(s). These online characterizations can

be used in an on-the-fly manner by the thread-mapping algorithm to achieve the objective of mitigating contention and reducing vulnerability.

For example, mapping different co-running applications from the given workload to use the same shared caches can vary the cache resource usage. An application's cache usage intensity creates contention in the shared cache, which eventually leads to application performance degradation. An application's cache usage characteristics can be determined online during its execution with the co-runner(s). The determined cache usage can be used to map the application threads with complementary cache behavior on the targeted machine during application execution to mitigate contention and ensure optimized performance [20, 4].

However, as the number of multi-threaded applications increases in a workload, the number of mapping configurations that must be evaluated to identify the application characteristics in the presence of co-runners and determine the optimal thread-mappings for performance and reliability improvement, can increase exponentially [21]. When the number of threads in a workload is very high, this exponential complexity makes the online resource usage detection and application thread-mappings very challenging and causes the characterization technique to have significant overhead. The online characterization becomes even more complex when dynamic workloads are considered because of the continuously changing and unpredictable set of co-running applications.

### 1.3.1 Application Characterization

To avoid the overhead and exponential complexity of an online characterization technique, an offline technique is used to determine a multi-threaded application's characteristics that are critical for addressing the targeted problem. This offline technique utilizes a general methodology to characterize a multi-threaded application when it runs solely without any co-runner. The characterization methodology isolates the effect of a targeted resource usage on a multi-threaded application's execution depending on the objective of performance optimization and reliability improvement. This isolation helps the application's behavior

analyses based on its usage of the targeted resource. Such analyses of isolated resource usage identify the application's key characteristics that precisely represent its sensitivity to that resource. Even though such characterization is performed without considering the presence of a co-running application, the sensitivity analyses help prioritize applications in a workload to determine the effective mappings for optimized performance and improved reliability.

#### 1.3.2 Application Mapping

An application's inherent characteristics of resource usage influence how the performance and reliability on a targeted platform are evolved. Thread-mapping is an application-level software technique that can control an application's resource usage by changing the cores on which the threads from a workload would run. It does not require special hardware, is relatively easy to integrate into any system, and has very low run-time overhead. Therefore, thread-mapping is an attractive approach and is used in the framework to effectively address resource contention and soft errors for performance and reliability improvements on multicore machines.

#### 1.3.3 Components of the Framework

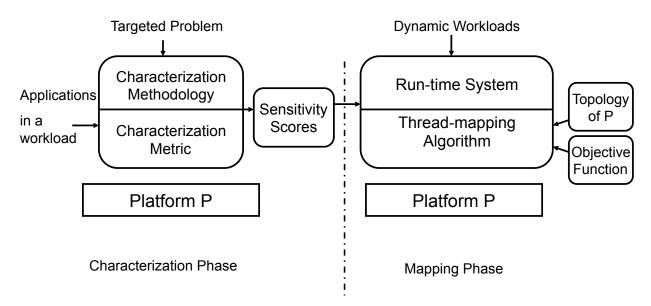

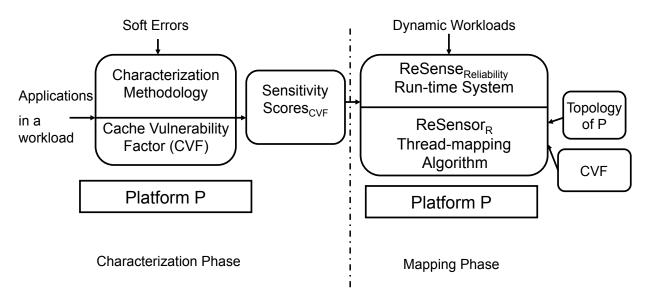

Based on the insights and discussion in the previous sections, we develop a novel, unified, and general framework called **ReSense** that addresses several key problems on multicore architectures (see Table 1.1). The framework includes five components: a general characterization methodology, a characterization metric, a sensitivity score, a thread mapping algorithm, and a run-time system. An instance of the framework is applied in two phases: characterization and mapping. The offline *characterization* phase utilizes the general characterization methodology and characterization metric to identify a multi-threaded application's key behavior with respect to resource usage for a targeted problem. It generates a resource-sensitivity score for each application in a workload. In the online *mapping* phase, the run-time system uses a thread-mapping algorithm and the sensitivity scores of the applications in a workload to determine the thread-mappings that optimize a problem-specific objective function. The

run-time system is capable of handling complex dynamic workloads. Whenever the number of threads changes in the workload, the run-time system invokes the mapping algorithm to dynamically adjust the thread-mappings for the new or modified workload in the system.

#### 1.3.4 Generality of the Framework

The ReSense framework can be used to address other problems on CMPs that are influenced by application characteristics, e.g., thermal and power consumption.

For example, an application's intensity of resource usage can have an impact on the processor temperature. Consider a computation-intensive application that uses integer and floating-point units can increase the processor temperature significantly. On the other hand, a memory-bound application can maintain lower processor temperature as it uses the core computational resources less intensely [22]. When these applications with different thermal profiles are considered in a workload, the intensity of their resource usage creates thermal variation inside the processor core and can cause thermal hot-spots, leading to a thermal emergency [22, 23]. An application's resource usage characteristics can also affect energy and power consumption of the targeted platform [24, 25].

The characterization phase of the ReSense framework can be used to identify how multithreaded applications' resource usage affects the thermal and power issues on CMPs. Then, ReSense's dynamic thread-mapping algorithms can be used to reduce power consumption and minimize hot-spots for avoiding thermal emergencies.

Column 1 of Table 1.1 lists the general challenges on a multicore architecture and Column 2 lists the corresponding targeted problems that can be addressed using the ReSense framework. The table also includes the application behaviors to be determined in the characterization phase (Column 3), the overall goal of the mapping phase (Column 4), and the objective function used by the thread-mapping algorithm (Column 5). In this dissertation, we address the resource contention and soft errors problems (first two rows of Table 1.1) using the framework.

| Challenges   | Targeted    | Application Behavior | Goal/            | Objective     |

|--------------|-------------|----------------------|------------------|---------------|

|              | Problem     |                      | Objective        | Function      |

| Performance  | Resource    | Contentiousness      | Mitigate         | Response time |

| Optimization | contention  | in shared-memory     | contention       | and           |

|              |             | resources            |                  | throughput    |

| Reliability  | Soft errors | Resource occupancy   | Reduce occupancy | Vulnerability |

| Improvement  |             | duration             | duration         | factor        |

|              |             |                      | in a resource    | of a resource |

| Thermal      | Thermal     | Computational        | Distribute       | Response time |

| Management   | emergency   | resource usage       | computation      | and           |

|              |             |                      | to minimize      | throughput    |

|              |             |                      | hot spots        |               |

| Power        | High power  | Power usage          | Reduce power     | Energy        |

| Management   | and energy  | in the resources     | and energy       | delay product |

|              | consumption |                      | consumption      |               |

Table 1.1: Targeted problems on modern CMPs to be addressed using the Re-Sense framework

## 1.3.5 Addressing Resource Contention and Soft Errors Using Re-Sense

An application's resource usage impacts its execution in a workload with respect to both resource contention and soft errors. Shared-resource contention makes the application execute slowly if the application uses the resources excessively. If an application occupies a resource for a long period of time, soft errors make it error prone. Both resource contention and soft errors can be addressed using the ReSense framework.

For the resource contention problem, the characterization methodology determines how a multi-threaded application's performance is affected as it shares a resource in the memory hierarchy. A sensitivity score based on resource contention is produced for each application in a workload. The run-time system uses the resource-contention sensitivity scores and a thread-mapping algorithm to allocate threads from a workload to core to mitigate shared-resource contention, thus improving response time and throughput (Table 1.1).

For the soft error problem, the characterization methodology determines how a multithreaded application's vulnerability to soft errors in shared caches is affected by its resource occupancy duration. A sensitivity score based on cache occupancy is produced for each application in a workload. The run-time system uses the cache-occupancy sensitivity scores and a thread-mapping algorithm to allocate threads from a workload to core to reduce the overall occupancy in the shared caches, thus reducing cache vulnerability (Table 1.1).

For both contention mitigation and vulnerable occupancy reduction, the thread-mapping algorithms are designed to use the multi-threaded applications' prior characterizations that are determined offline. In particular, each multi-threaded application in any workload is characterized *only once* without considering the presence of any co-runner, and the algorithms map any combination of these multi-threaded applications using the pre-determined offline characterizations for optimizing the objective functions (Table 1.1). The offline characteristics for individual applications are represented as *sensitivity scores*, which quantitatively describe an application's solo-sensitivity to the targeted resources. When these applications are considered in a workload, these sensitivity scores are used to prioritize the applications when their thread-mappings are determined with respect to the targeted resources in the presence of co-runners(s). The most-sensitive applications affect the objective function more than the less-sensitive applications.

For example, when a workload consists of a cache-intensive and a computation-intensive application, the mapping that gives priority to the cache-intensive application results in a reduced response time and increased throughput because the cache-intensive application is more sensitive to the shared cache usage than the computation-intensive application [4]. Therefore, even though the application characteristics are not determined in the presence of co-runners, the sensitivity score captures an application's key behavior for the targeted resource, and applications in a workload can be prioritized and compared with each other based on how their sensitivity scores for the targeted resource usage. The thread-mapping algorithms thus work by prioritizing the most-sensitive applications in the workload based on

their sensitivity scores and dynamically determine the thread-mappings of the applications.

The performance and reliability improvements are often conflicting goals [26, 18]. The thread-mapping algorithm that ensures better performance may not ensure better reliability. By designing an algorithm that considers two objectives of the resource contention and soft errors problems (Table 1.1), in this thesis, we demonstrate the use of ReSense to determine a trade-off between reducing response time and vulnerability factors of shared caches for a workload.

#### 1.4 Thesis Statement

On a multicore machine running multiple multi-threaded applications simultaneously, a workload's response time and throughput can be improved and vulnerability to soft errors in shared caches can be reduced via thread-mapping driven by the resource usage characteristics of the applications that are determined using an offline technique.

#### 1.5 List of Contributions

This dissertation makes the following contributions.

- A novel and efficient offline technique for characterizing a multi-threaded application's resource usage by running it solely.

- The use of offline sensitivity characterization in determining the thread-mappings of multi-threaded applications in a workload to mitigate contention and reduce vulnerability to soft errors.

- ReSense, a unified framework that can be used to address the performance optimization, reliability improvement, thermal and power management challenges on a multicore platform.

- Development of the performance instance of ReSense, ReSense\_Performance. This instance addresses the challenges of mitigating shared-resource contention in the memory

1.6 | Thesis Outline

hierarchy and optimizes response time and throughput of the applications in a workload. Using dynamic workloads of different sizes, ReSense\_Performance is able to improve the response time by up to 29.34% and throughput by up to 46.56% over the native operating system (OS) using real hardware.

- Development of the reliability instance of ReSense, ReSense\_Reliability. This instance addresses the challenges of improving application reliability on multicore machines by using an application-level technique and minimizes the overall cache vulnerability to soft errors on a targeted multicore platform. ReSense\_Reliability effectively reduces the overall cache vulnerability by up to 70% over the native OS.

- Development of the integrated instance of ReSense, ReSense\_Integration. This instance combines application characteristics for both contention and vulnerability to soft errors and determines a trade-off between the performance and reliability improvement on a multicore machine. When applications' contentious behaviors are more preferred, ReSense\_Integration reduces applications' response time, and when applications' vulnerability characterizations are more preferred, it reduces the overall shared cache vulnerability.

#### 1.6 Thesis Outline

The thesis is organized as follows: Chapter 2 describes the state-of-the-art related work for resource contention and soft errors. Chapter 3 describes the design of the ReSense framework in more detail. Chapter 4 presents the performance instance of the ReSense framework, including the characterization process for resource contention and the mapping algorithm for performance optimization. Chapter 5 presents the reliability instance of ReSense framework, including the characterization methodology for application vulnerability and the mapping algorithm for reliability improvement. Chapter 6 describes the integration of the performance and reliability instances to determine a trade off between performance and

reliability improvements. Chapter 7 summarizes the findings, describes the future work, and concludes the thesis.

# Chapter 2

## Related Work

In this chapter, we discuss prior research related to resource contention and soft errors. First, we describe the research on application characterization for resource contention and vulnerability to soft errors. Then we describe prior research on the techniques for contention mitigation to improve performance and the techniques for reducing the effects of soft errors to improve reliability.

## 2.1 Application Characterization

#### 2.1.1 Resource Contention Characterization

#### 2.1.1.1 Characterization for Single-threaded Applications

There has been prior work on application characterization for shared-resource contention. Zhuravlev et al. analyzes the effect of cache contention created by co-runners and provides a comprehensive analysis of different cache-contention classification schemes [4]. Mars et al. synthesizes and analyzes cross-core performance interference for last-level caches (LLC) on two architectures [27, 28]. They characterize the applications in the presence of co-runners using synthetic workloads and determine the effects of contention for the memory resources [29]. Xie and Loh characterize and classify applications by measuring cache miss-rates for a dynamic cache partitioning scheme [30]. Zhao et al. investigates low overhead

mechanisms for fine-grained monitoring of shared cache usage, interference, and sharing to determine application characteristics [31]. These works mainly analyze cache contention for single-threaded applications. In contrast, we design a general methodology in ReSense to characterize any multi-threaded application for not only LLC contention, but also contention for private caches, front-side bus, memory controllers, and memory socket connections.

#### 2.1.1.2 Characterization for Multi-threaded Applications