#### last time (1)

```

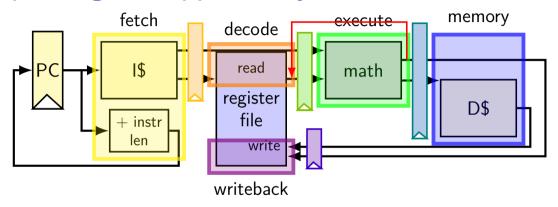

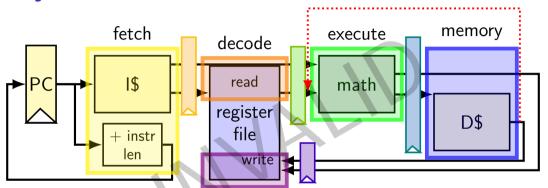

single-cycle CPU review

```

one possible CPU design that runs one instruction per cycle PC changes at beginning of cycle, cascades for other components to operation

#### pipelining idea

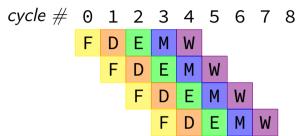

laundry analogy opportunity: in single-cycle design, most components mostly idle assembly-line: step 1 of instr 1 then  $\{\text{step 2 of instr 1} + \text{step 1 of instr 2}\}$

then  $\{\text{step 3 of instr } 1 + \text{step 2 of instr } 2 + \text{step 1 of instr 3} \}$  then ... adding registers to store values for each stage

## last time (2)

#### pipelining limits

cycle time determined by slowest stage time taken by new registers uneven split of stages doubling pipeline stages != half cycle time

#### data hazards

solving by changing ISA? solving by *stalling* (insert nops)

#### anonymous feedback

"Why are we using kytos for the autograders when we can use gradescope? Having to wait over an hour for an "autograder" is unacceptable. I have never had gradescope take more than 2 minutes with any autograded submission and I've never had kytos take less than 5 minutes, often it taking an hour/running overnight. I understand there are conveniences with kytos (the cumulative performance), but if we are truly doing assignments that are autograded and provide instant feedback, we shouldn't need to spend several hours waiting. I'll propose some potential solutions that could remedy the problem: 1. If people are missing just 1-2 tests on the autograder, just bump their score up to 100 so they don't clog up the queue, 2. Extend the assignment for each person individually based on how long they've waited for their submission to be graded (maybe up to a certain number of submissions), 3. Use Gradescope!"

life 'test your code' section which was pretty complete

given basically this assignment with no autograder feedback before

from talking to other faculty, gradescope is not always as fast as you think

(though, yes, when the queue is empty, it starts things sooner...)

probably would have been better if autograder gave up on submissions that

timeout a lot faster (which would've also been a problem under gradescope)

#### some notes on the lab (1)

map/reduce division

I expected one loop

map strategy determines which items you do log(...) operation for reduce strategy determines how you do += to answer

okay to two loops, but much harder to make efficient

#### some notes on the lab (2)

```

why was atomic update reduce strategy slow?

processors need to take turns having accumulator (answer)

lots of synchronization time + mostly one thread works at a time

why was task queue strategy slow?

processors need to take turns grabbing index to use next

lots of synchronization time

what about few-to-many reduction with array?

```

```

results[thread_id] +=

problem: multiple thread values are in same cache block

cores need to take turns having the block in their cache to write

workaround: make results array be more spread out

called "false sharing"

```

## upcoming lab/HW logistics

### addq processor: data hazard

```

// initially %r8 = 800,

// %r9 = 900, etc.

addq %r8, %r9

addq %r9, %r8

addq ...

addg ...

```

|       | fetch | fetch | /decode |      |             | execute/memory |      | memory/v | vriteback |    |

|-------|-------|-------|---------|------|-------------|----------------|------|----------|-----------|----|

| cycle | PC    | rA    | rB      | R[rB | R[rB] rB si |                | sum  | rB       | sum       | rB |

| Θ     | 0×0   |       |         |      | •           |                |      | •        |           |    |

| 1     | 0x2   | 8     | 9       |      |             |                |      |          |           |    |

| 2     |       | 9     | 8       | 800  | 900         | 9              |      |          |           |    |

| 3     |       |       |         | 900  | 800         | 8              | 1700 | 9        | ]         |    |

| 4     |       |       |         |      | •           |                | 1700 | 8        | 1700      | 9  |

| 5     |       |       |         |      |             |                |      |          | 1700      | 8  |

#### addq processor: data hazard

```

// initially %r8 = 800,

// %r9 = 900, etc.

addq %r8, %r9

addq %r9, %r8

addq ...

addq ...

```

|       | fetch | fetch/         | decode | dec  | decode/execute      |   |      | memory | memory/writeb |    |  |

|-------|-------|----------------|--------|------|---------------------|---|------|--------|---------------|----|--|

| cycle | PC    | rA             | rB     | R[rB | R[rB  R[rB]  rB  si |   | sum  | rB     | sum           | rB |  |

| Θ     | 0×0   |                |        |      |                     |   |      |        |               |    |  |

| 1     | 0x2   | 8              | 9      |      |                     |   |      |        |               |    |  |

| 2     |       | 9              | 8 [    | 800  | 900                 | 9 |      |        |               |    |  |

| 3     |       |                |        | 900  | 800                 | 8 | 1700 | 9      |               |    |  |

| 4     |       |                |        |      |                     |   | 1700 | 8      | 1700          | 9  |  |

| 5     |       | should be 1700 |        |      |                     |   |      | •      | 1700          | 8  |  |

#### data hazard

```

addq %r8, %r9 // (1)

addq %r9, %r8 // (2)

```

| step# | pipeline implementation | ISA specification   |

|-------|-------------------------|---------------------|

| 1     | read r8, r9 for (1)     | read r8, r9 for (1) |

| 2     | read r9, r8 for (2)     | write r9 for (1)    |

| 3     | write r9 for (1)        | read r9, r8 for (2) |

| 4     | write r8 for (2)        | write r8 ror (2)    |

pipeline reads older value...

instead of value ISA says was just written

#### data hazard compiler solution

```

addq %r8, %r9

nop

nop

addq %r9, %r8

one solution: change the ISA

all addgs take effect three instructions later

(assuming can read register value while it is being written back)

make it compiler's job

problem: recompile everytime processor changes?

```

#### data hazard hardware solution

```

addq %r8, %r9

// hardware inserts: nop

// hardware inserts: nop

adda %r9, %r8

how about hardware add nops?

called stalling

extra logic:

sometimes don't change PC

sometimes put do-nothing values in pipeline registers

```

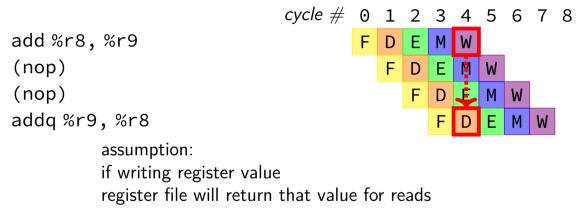

## stalling/nop pipeline diagram (1)

```

add %r8, %r9

(nop)

(nop)

addq %r9, %r8

```

# stalling/nop pipeline diagram (1)

not actually way register file worked in single-cycle CPU (e.g. can read old %r9 while writing new %r9)

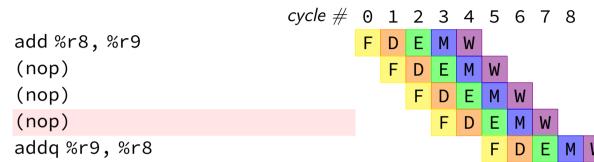

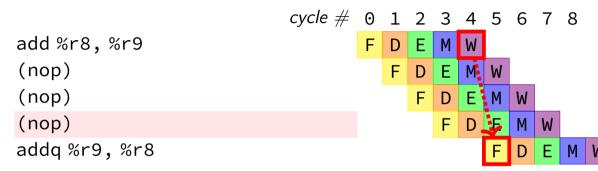

## stalling/nop pipeline diagram (2)

## stalling/nop pipeline diagram (2)

if we didn't modify the register file, we'd need an extra cycle

#### opportunity

```

// initially %r8 = 800,

// %r9 = 900, etc.

0x0: addq %r8, %r9

0x2: addq %r9, %r8

```

. . .

|       | fetch | fetch | /decode | dec        | decode/execute         |   | execute/ | memory | memory/v | vriteback |

|-------|-------|-------|---------|------------|------------------------|---|----------|--------|----------|-----------|

| cycle | PC    | rA    | rB      | R[rB       | R[rB   R[rB]   rB   sı |   | sum      | rB     | sum      | rB        |

| 0     | 0×0   |       |         |            |                        |   |          |        |          |           |

| 1     | 0x2   | 8     | 9       |            |                        |   |          |        |          |           |

| 2     |       | 9     | 8       | 800        | 900                    | 9 |          | 7      |          |           |

| 3     |       |       |         | 900        | 800                    | 8 | 1700     | 9      |          |           |

| 4     |       |       | ' '     | 1.1.1      | 1700                   |   | 1700     | 8      | 1700     | 9         |

| 5     |       |       | shou    | ld be 1700 |                        |   |          |        | 1700     | 8         |

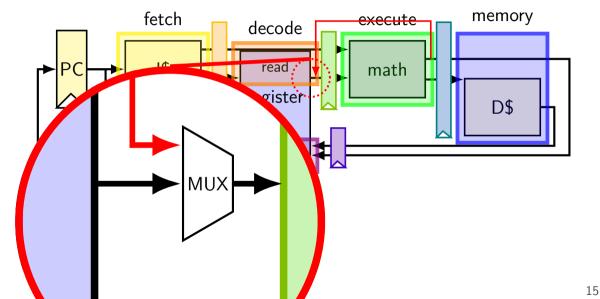

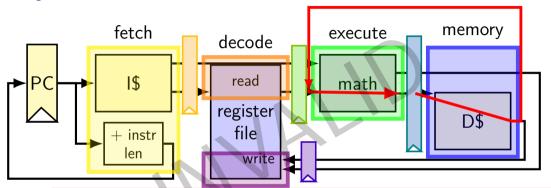

#### exploiting the opportunity

## exploiting the opportunity

#### opportunity 2

```

// initially %r8 = 800,

// %r9 = 900, etc.

0x0: addq %r8, %r9

0x2: nop

0x3: addq %r9, %r8

```

|       | fetch | fetch/ | decode | ,           |           | execute/memory |      | memory/v | vriteback |    |

|-------|-------|--------|--------|-------------|-----------|----------------|------|----------|-----------|----|

| cycle | PC    | rA     | rB     | R[rB        | R[rB]     | rB             | sum  | rB       | sum       | rB |

| Θ     | 0×0   |        |        |             |           |                |      |          |           |    |

| 1     | 0×2   | 8      | 9      |             |           |                |      |          |           |    |

| 2     | 0x3   |        |        | 800         | 300 900 9 |                |      |          |           |    |

| 3     |       | 9      | 8      |             |           |                | 1700 | 9        |           | ,  |

| 4     |       |        |        | 900         | 800       | 8              |      |          | 1700      | 9  |

| 5     |       |        | , '    |             | 1700      |                | 1700 | 9        |           |    |

| 6     |       |        | shou   | ıld be 1700 |           |                |      |          | 1700      | 9  |

## exploiting the opportunity

exercise: forwarding paths cycle # 0 1 2 3 4 5 6 7 8 addg %r8, %r9 FDEMW FDEMW subg %r8, %r10 xorq %r8, %r9 FDEMW andg %r9, %r8 FDEMW in subg, %r8 is \_\_\_\_\_ addg. in xorq, %r9 is \_\_\_\_\_ addq. in andg, %r9 is \_\_\_\_\_ addg.

in and q, %r9 is \_\_\_\_\_ xorq. A: not forwarded from

B-D: forwarded to decode from {execute, memory, writeback} stage of

| cycle #            | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |  |

|--------------------|---|---|---|---|---|---|---|---|---|--|

| addq %r8, %r9      | F | D | Ε | М | W |   |   |   |   |  |

| subq %r9, %r11     |   | F | D | Ε | М | W |   |   |   |  |

| movq 4(%r11), %r10 |   |   | F | D | Ε | М | W |   |   |  |

| movq %r9, 8(%r11)  |   |   |   | F | D | Ε | M | W |   |  |

| xorq %r10, %r9     |   |   |   |   | F | D | Ε | М | W |  |

| cycle #                      | 0 | 1 | 2              | 3 | 4 | 5 | 6 | 7 | 8 |  |

|------------------------------|---|---|----------------|---|---|---|---|---|---|--|

| addq %r8, <mark>%r9</mark>   | F | D | Ε <sub>\</sub> | M | W |   |   |   |   |  |

| subq <mark>%r9</mark> , %r11 |   | F | D              | Ε | М | W |   |   |   |  |

| movq 4(%r11), %r10           |   |   | F              | D | Ε | М | W |   |   |  |

| movq %r9, 8(%r11)            |   |   |                | F | D | Ε | М | W |   |  |

| xorq %r10, %r9               |   |   |                |   | F | D | Ε | М | W |  |

| cycle #                      | 0 | 1 | 2              | 3 | 4 | 5 | 6 | 7 | 8 |  |

|------------------------------|---|---|----------------|---|---|---|---|---|---|--|

| addq %r8, <mark>%r9</mark>   | F | D | Ε <sub>\</sub> | M | W |   |   |   |   |  |

| subq <mark>%r9</mark> , %r11 |   | F | D              | Ε | М | W |   |   |   |  |

| movq 4(%r11), %r10           |   |   | F              | D | Ε | М | W |   |   |  |

| movq %r9, 8(%r11)            |   |   |                | F | D | Ε | М | W |   |  |

| xorq %r10, %r9               |   |   |                |   | F | D | Ε | М | W |  |

| cycle #                         | 0 | 1 | 2  | 3 | 4 | 5 | 6 | 7 | 8 |  |

|---------------------------------|---|---|----|---|---|---|---|---|---|--|

| addq %r8, <mark>%r9</mark>      | F | D | E۱ | M | W |   |   |   |   |  |

| subq %r9, %r11                  |   |   | D  |   |   |   |   |   |   |  |

| movq 4(%r11), %r10              |   |   | F  | D | Ε | М | W |   |   |  |

| movq <mark>%r9</mark> , 8(%r11) |   |   |    | F | D | Ε | М | W |   |  |

| xorq %r10, %r9                  |   |   |    |   | F | D | Ε | М | W |  |

| cycle #                           | 0 | 1 | 2  | 3              | 4 | 5 | 6 | 7 | 8 |  |

|-----------------------------------|---|---|----|----------------|---|---|---|---|---|--|

| addq %r8, %r9                     | F | D | Εl | М              | W |   |   |   |   |  |

| subq %r9, <mark>%r11</mark>       |   | F | D  | Ε <sub>\</sub> | М | W |   |   |   |  |

| movq 4( <mark>%r11</mark> ), %r10 |   |   | F  | D              | Ε | М | W |   |   |  |

| movq %r9, 8(%r11)                 |   |   |    | F              | D | Ε | М | W |   |  |

| xorq %r10, %r9                    |   |   |    |                | F | D | Ε | М | W |  |

| cycle #                          | 0 | 1 | 2  | 3  | 4 | 5 | 6 | 7 | 8 |  |

|----------------------------------|---|---|----|----|---|---|---|---|---|--|

| addq %r8, %r9                    | F | D | Εl | М  | W |   |   |   |   |  |

| subq %r9, <mark>%r11</mark>      |   | F | D  | E۱ | М | W |   |   |   |  |

| movq 4(%r11), %r10               |   |   | F  | D  | Ε | М | W |   |   |  |

| movq %r9, 8( <mark>%r11</mark> ) |   |   |    | F  | D | Ε | М | W |   |  |

| xorq %r10, %r9                   |   |   |    |    | F | D | Ε | М | W |  |

| cycle #                      | 0 | 1 | 2              | 3 | 4 | 5 | 6 | 7 | 8 |  |

|------------------------------|---|---|----------------|---|---|---|---|---|---|--|

| addq %r8, %r9                | F | D | Ε <sub>\</sub> | M | W |   |   |   |   |  |

| subq %r9, %r11               |   |   | D              |   |   |   |   |   |   |  |

| movq 4(%r11), %r10           |   |   |                |   |   |   | W |   |   |  |

| movq %r9, 8(%r11)            |   |   |                | F | D | Ε | М | W |   |  |

| xorq <mark>%r10</mark> , %r9 |   |   |                |   | F | D | Ε | М | W |  |

| cycle #                     | 0 | 1 | 2              | 3 | 4 | 5 | 6 | 7 | 8 |  |

|-----------------------------|---|---|----------------|---|---|---|---|---|---|--|

| addq %r8, <mark>%r9</mark>  | F | D | Ε <sub>\</sub> | М | W |   |   |   |   |  |

| subq %r9, %r11              |   | F | D              |   |   |   |   |   |   |  |

| movq 4(%r11), %r10          |   |   | F              | D | Ε | M | W |   |   |  |

| movq %r9, 8(%r11)           |   |   |                | F | D | Ε | М | W |   |  |

| xorq %r10, <mark>%r9</mark> |   |   |                |   | F | D | Ε | М | W |  |

| cycle #                       | 0 | 1 | 2  | 3 | 4 | 5 | 6 | 7 | 8 |  |

|-------------------------------|---|---|----|---|---|---|---|---|---|--|

| addq %r8, %r9                 | F | D | E۱ | M | W |   |   |   |   |  |

| subq %r9, %r11                |   |   | D  |   |   |   |   |   |   |  |

| <pre>movq 4(%r11), %r10</pre> |   |   | F  | D | Ε | M | W |   |   |  |

| movq %r9, 8(%r11)             |   |   |    | F | D | Ε | М | W |   |  |

| xorq %r10, %r9                |   |   |    |   | F | D | Ε | М | W |  |

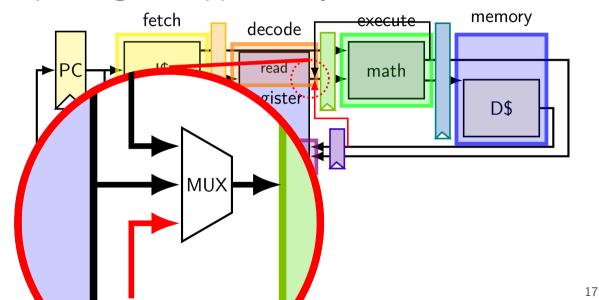

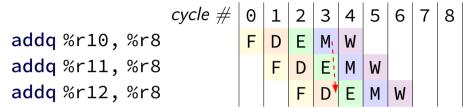

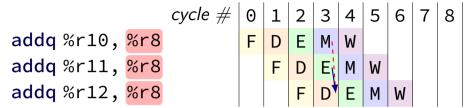

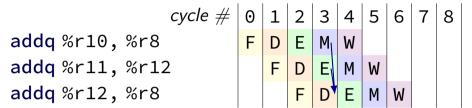

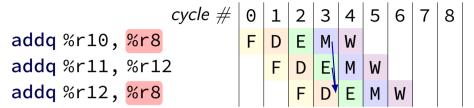

#### multiple forwarding paths (1)

### multiple forwarding paths (1)

### multiple forwarding paths (2)

### multiple forwarding paths (2)

## multiple forwarding paths (2)

```

cycle #

0

1

2

3

4

5

6

7

8

addq %r10, %r8

F

D

E

M

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W</t

```

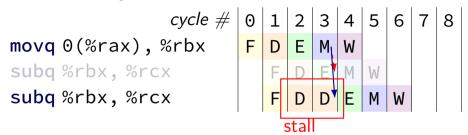

## unsolved problem

combine stalling and forwarding to resolve hazard

assumption in diagram: hazard detected in subq's decode stage (since easier than detecting it in fetch stage)

## unsolved problem

combine stalling and forwarding to resolve hazard

assumption in diagram: hazard detected in subq's decode stage (since easier than detecting it in fetch stage)

### solveable problem

```

cycle #

0

1

2

3

4

5

6

7

8

movq 0(%rax), %rbx

F

D

E

M

W

W

B

B

B

W

W

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

```

### why can't we...

clock cycle needs to be long enough

to go through data cache AND

to go through math circuits!

(which we were trying to avoid by putting them in separate stages)

2

## why can't we...

clock cycle needs to be long enough

to go through data cache AND

to go through math circuits!

(which we were trying to avoid by putting them in separate stages)

2

## hazards versus dependencies

dependency — X needs result of instruction Y?

has potential for being messed up by pipeline

(since part of X may run before Y finishes)

hazard — will it not work in some pipeline?

before extra work is done to "resolve" hazards

multiple kinds: so far, data hazards

```

addq %rax, %rbx

subq %rax, %rcx

movq $100, %rcx

addq %rcx, %r10

addq %rbx, %r10

```

```

addq %rax, %rbx

subq %rax, %rcx

movq $100, %rcx

addq %rcx, %r10

addq %rbx, %r10

```

```

addq %rax, %rbx

subq %rax, %rcx

movq $100, %rcx

addq %rcx, %r10

addq %rbx, %r10

```

```

addq %rax, %rbx

subq %rax, %rcx

movq $100, %rcx

addq %rcx, %r10

addq %rbx, %r10

```

# pipeline with different hazards

```

example: 4-stage pipeline:

fetch/decode/execute+memory/writeback

// 4 stage // 5 stage

addq %rax, %r8 // // W

subq %rax, %r9 // W // M

xorq %rax, %r10 // EM // E

andq %r8, %r11 // D // D

```

# pipeline with different hazards

```

example: 4-stage pipeline:

fetch/decode/execute+memory/writeback

// 4 stage // 5 stage

addq %rax, %r8 // // W

subq %rax, %r9 // W // M

xorq %rax, %r10 // EM // E

andq %r8, %r11 // D // D

```

addq/andq is hazard with 5-stage pipeline addq/andq is **not** a hazard with 4-stage pipeline

# pipeline with different hazards

```

example: 4-stage pipeline:

fetch/decode/execute+memory/writeback

// 4 stage // 5 stage

addq %rax, %r8 // // W

subq %rax, %r9 // W // M

xorq %rax, %r10 // EM // E

andq %r8, %r11 // D // D

```

split execute into two stages: F/D/E1/E2/M/W

result only available near end of second execute stage

where does forwarding, stalls occur?

| cycle #                   | 0 | 1 | 2  | 3  | 4 | 5 | 6 | 7 | 8 |

|---------------------------|---|---|----|----|---|---|---|---|---|

| (1) addq %rcx, %r9        | F | D | E1 | E2 | М | W |   |   |   |

| (2) <b>addq</b> %r9, %rbx |   |   |    |    |   |   |   |   |   |

| (3) addq %rax, %r9        |   |   |    |    |   |   |   |   |   |

| (4) movq %r9, (%rbx)      |   |   |    |    |   |   |   |   |   |

| (5) movq %rcx, %r9        |   |   |    |    |   |   |   |   |   |

split execute into two stages: F/D/E1/E2/M/W

| cycle #                          | 0 | 1 | 2  | 3  | 4 | 5 | 6 | 7 | 8 |  |

|----------------------------------|---|---|----|----|---|---|---|---|---|--|

| addq %rcx, %r9<br>addq %r9, %rbx | F | D | E1 | E2 | М | W |   |   |   |  |

| addq %rax, %r9                   |   |   |    |    |   |   |   |   |   |  |

| movq %r9, (%rbx)                 |   |   |    |    |   |   |   |   |   |  |

|                                  |   |   |    |    |   |   |   |   |   |  |

| split execute into two stages: $F/D/E1/E2/M/W$ |                                  |       |                |     |     |       |      |      |     |  |  |

|------------------------------------------------|----------------------------------|-------|----------------|-----|-----|-------|------|------|-----|--|--|

| cycle #                                        | 0                                | 1     | 2              | 3   | 4   | 5     | 6    | 7    | 8   |  |  |

| addq %rcx, %r9                                 | F                                | :     |                |     |     |       |      |      |     |  |  |

| addq %r9, %rbx                                 |                                  | F     | D <sup>†</sup> | E1  | E2  | М     | W    |      |     |  |  |

|                                                |                                  |       |                |     |     |       |      |      |     |  |  |

| addq %rax, %r r9 not                           | avai                             | lable | e ye           | t — | can | 't fo | orwa | rd h | ere |  |  |

|                                                | so try stalling in addq's decode |       |                |     |     |       |      |      |     |  |  |

| movq %r9, (%rbx)                               |                                  |       |                | F   | D   | E1    | E2   | М    | W   |  |  |

|                                                |                                  |       |                |     |     |       |      |      |     |  |  |

split execute into two stages: F/D/E1/E2/M/W *cycle* # 0 1 2 3 4 5 6 7 8 addg %rcx, %r9 F D E1 E2 M W F D E1 E2 M W addg %r9, %rbx F D D E1 E2 M W addq %r9, %rbx addq %rax, %r after stalling once, now we can forward addq %rax, %r9 F1 E2 M W movg %r9, (%rbx) F D F1 F2 M W movg %r9, (%rbx) F D E1 E2 M W

split execute into two stages: F/D/E1/E2/M/W

| cycle #                 | 0                     | 1 | 2  | 3  | 4  | 5            | 6  | 7  | 8 |   |

|-------------------------|-----------------------|---|----|----|----|--------------|----|----|---|---|

| addq %rcx, %r9          | F                     | D | E1 | E2 | М  | W            |    |    |   |   |

| addq %r9, %rbx          |                       | F | D  | Ε1 | E2 | $\mathbb{M}$ | W  |    |   |   |

| addq %r9, %rbx          |                       | F | D  | D  | E1 | E2           | М  | W  |   |   |

| addq %rax, %r9          |                       |   | F  | D  | E1 | E2           | М  | W  |   |   |

| addq %rax, %r9          | 1<br>1<br>1<br>1<br>1 |   | F  | F  | D  | E1           | E2 | М  | W |   |

| movq %r9, (%rbx)        |                       |   |    | F  | D  | Ε1           | E2 | M  | W |   |

| <b>movq</b> %r9, (%rbx) |                       |   | :  | :  | F  | D            | E1 | E2 | М | W |

movq %rcx, %r9

split execute into two stages: F/D/E1/E2/M/W cvcle # 0 1 2 3 4 5 6 7 8 adda %rcx, %r9 E1 E2 M<sub>1</sub> addq %r9, %rbx addq %r9, %rbx D D T E1 E2 addq %rax, %r9 addq %rax, %r9 F D E1 E2 movg %r9, (%rbx) movg %r9, (%rbx)

#### control hazard

0x00: cmpq %r8, %r9

0x08: je 0xFFFF

0x10: addq %r10, %r11

|       | fetch | $fetch \!\! 	o \!\!$ | decode | lecode- | $\rightarrow$ execut | execute   | execu | te→writeback |  |

|-------|-------|----------------------|--------|---------|----------------------|-----------|-------|--------------|--|

| cycle | PC    | rA                   | rB     | R[rA]   | R[rB]                | result    |       |              |  |

| 0     | 0×0   |                      |        |         |                      |           |       |              |  |

| 1     | 0x8   | 8                    | 9      |         |                      |           |       |              |  |

| 2     | ???   |                      |        | 800     | 900                  |           |       |              |  |

| 3     | ???   |                      |        |         |                      | less than |       |              |  |

#### control hazard

```

0x00: cmpq %r8, %r9

```

0x08: je 0xFFFF

0x10: addq %r10, %r11

|       | fetch | $fetch \!\! 	o \!\!$ | decode d | lecode- | $\rightarrow$ execut | execute   | execu | te→writeback |  |

|-------|-------|----------------------|----------|---------|----------------------|-----------|-------|--------------|--|

| cycle | PC    | rA                   | rB       | R[rA]   | R[rB]                | result    |       |              |  |

| 0     | 0×0   |                      |          |         |                      |           |       |              |  |

| 1     | 9x8   | 9                    | 9        |         |                      |           |       |              |  |

| 2     | ???   |                      |          | 800     | 900                  |           |       |              |  |

| 3     | ???   |                      |          |         |                      | less than |       |              |  |

0xFFFF if R[8] = R[9]; 0x10 otherwise

```

cmpq %r8, %r9

ine LABEL

// not taken

xorq %r10, %r11

movg %r11, 0(%r12)

cvcle # 0 1 2 3 4 5 6 7 8

cmpq %r8, %r9

М

ine LABEL

Ε

W

(do nothing)

D

М

(do nothing)

Е

xorq %r10, %r11

D

М

movq %r11, 0(%r12)

•••

```

```

cmpq %r8, %r9

ine LABEL

// not taken

xorq %r10, %r11

movg %r11, 0(%r12)

cycle # 0 1 2 3 4 5 6 7 8

cmpq %r8, %r9

compare sets flags | E

ine LABEL

W

D

(do nothing)

D

М

(do nothing)

Е

xorq %r10, %r11

D

M

mova %r11, 0(%r12)

•••

```

```

cmpq %r8, %r9

ine LABEL

// not taken

xorq %r10, %r11

movq %r11, 0(%r12)

cycle # 0 1 2 3 4 5 6 7 8

cmpq %r8, %r9

ine LABEL compute if jump goes to LABED

(do nothing)

М

(do nothing)

Е

xorq %r10, %r11

M

mova %r11, 0(%r12)

```

```

cmpq %r8, %r9

ine LABEL

// not taken

xorq %r10, %r11

movg %r11, 0(%r12)

cycle # 0 1 2 3 4 5 6 7 8

cmpq %r8, %r9

М

ine LABEL

(do nothing)

М

(do nothing)

Е

xorq %r10, %r11

use computed result | F

M

mova %r11, 0(%r12)

```

### making guesses

```

cmpq %r8, %r9

jne LABEL

xorq %r10, %r11

movq %r11, 0(%r12)

...

```

```

LABEL: addq %r8, %r9 imul %r13, %r14 ...

```

speculate (guess): jne won't go to LABEL

right: 2 cycles faster!; wrong: undo guess before too late

# jXX: speculating right (1)

```

cmpq %r8, %r9

ine LABEL

xora %r10, %r11

movq %r11, 0(%r12)

. . .

LABEL: addg %r8, %r9

imul %r13, %r14

cycle # 0 1 2 3 4 5 6 7 8

cmpq %r8, %r9

М

ine LABEL

Ε

xorg %r10, %r11

D

М

movq %r11, 0(%r12)

F

```

•••

# jXX: speculating wrong

```

cycle # 0 1 2 3 4 5 6 7 8

cmpq %r8, %r9

ine LABEL

D

xorq %r10, %r11

F

(inserted nop)

movg %r11, 0(%r12)

F

(inserted nop)

F

LABEL: addg %r8, %r9

М

D

imul %r13, %r14

```

34

# jXX: speculating wrong

```

cycle # 0 1 2 3 4 5 6 7 8

cmpg %r8, %r9

ine LABEL

F

D

xorq %r10, %r11

instruction "squashed"

(inserted nop)

movg %r11, 0(%r12)

instruction "squashed"

(inserted nop)

F

LABEL: addg %r8, %r9

Е

М

D

imul %r13, %r14

```

34

### "squashed" instructions

on misprediction need to undo partially executed instructions

mostly: remove from pipeline registers

more complicated pipelines: replace written values in cache/registers/etc.

# backup slides

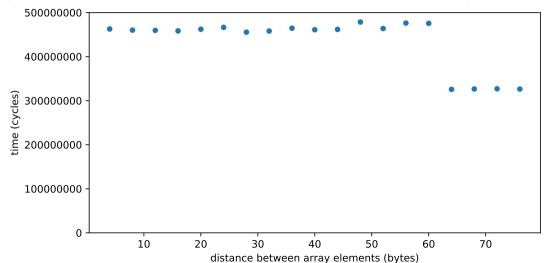

## modifying cache blocks in parallel

cache coherency works on cache blocks

but typical memory access — less than cache block e.g. one 4-byte array element in 64-byte cache block

what if two processors modify different parts same cache block?

4-byte writes to 64-byte cache block

cache coherency — write instructions happen one at a time: processor 'locks' 64-byte cache block, fetching latest version processor updates 4 bytes of 64-byte cache block later, processor might give up cache block

# modifying things in parallel (code)

```

void *sum_up(void *raw_dest) {

int *dest = (int *) raw dest;

for (int i = 0; i < 64 * 1024 * 1024; ++i) {

*dest += data[i]:

__attribute__((aligned(4096)))

int array[1024]; /* aligned = address is mult. of 4096 */

void sum twice(int distance) {

pthread t threads[2];

pthread_create(&threads[0], NULL, sum_up, &array[0]);

pthread create(&threads[1], NULL, sum up, &array[distance]);

pthread_join(threads[0], NULL);

pthread join(threads[1], NULL);

```

## performance v. array element gap

(assuming sum\_up compiled to not omit memory accesses)

## false sharing

synchronizing to access two independent things

two parts of same cache block

solution: separate them