## changelog

17 March 2024: upload full slides (including exercise-related diagrams)

### last time

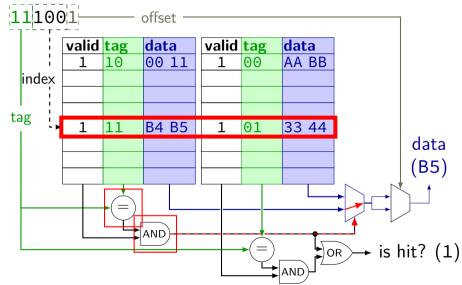

simulating direct-mapped caches find tag/index/offset split lookup index

K-way set-associative caches same tag/index/offset split K direct-mapped caches "stapled together" 'sets' (rows) with multiple blocks

started mapping C accesses to caches

alignment: don't want single values to split blocks

example 4-byte int at multiple of 4 address

but doesn't mean, e.g., array starts at beginning of block

### reminder re: pagetable2

due next Wednesday before first lab

normal late policy *does not apply*late submissions not normally accepted

also, you probably want to start pagetable3 extra parts early (rather than trying to do it in 2-3 days)

#### A reverse order:

```

still good spatial locality (accesses close to each other) just as good temporal locality (repeat accesses, right after each other)(

```

#### B singly-linked list:

```

more spread out (worse spatial locality) more things to access (worse temporal locality)

```

#### C single loop:

better temporal locality

#### D halving N:

better temporal locality

```

0 \times 401 = 100 \ 0000 \ 0001

0 \times 542 = 101 \ 0100 \ 0010

```

#### 4 offset bits

need to have at least 3 index bits for first different bit to be included

3 index bits would be 8 sets

(more index bits would be more sets)

16 bytes fits 4 4-byte integers

array spans 8192/4 = 2048 cache blocks

each cache block needs to be accessed twice

```

array at 0\times1000000

16 byte blocks \rightarrow 4 ints per block

array[0-3]: set 0

array[4-7]: set 1

array[100-103]: set 25

array[1020-1023]: set 255

array[1024-1027]: set 0

array[1028-1031]: set 1

array[1120-1123]: set 25

```

## C and cache misses (warmup 1)

```

int array[4];

...

int even_sum = 0, odd_sum = 0;

even_sum += array[0];

odd_sum += array[1];

even_sum += array[2];

odd_sum += array[3];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on a 1-set direct-mapped cache with 8B blocks?

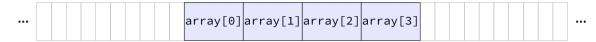

## some possiblities

Q1: how do cache blocks correspond to array elements? not enough information provided!

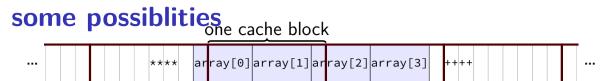

## some possiblities

one cache block

|--|

if array[0] starts at beginning of a cache block... array split across two cache blocks

| memory access        | cache contents afterwards |  |  |  |  |

|----------------------|---------------------------|--|--|--|--|

|                      | (empty)                   |  |  |  |  |

| read array[0] (miss) | {array[0], array[1]}      |  |  |  |  |

| read array[1] (hit)  | {array[0], array[1]}      |  |  |  |  |

| read array[2] (miss) | {array[2], array[3]}      |  |  |  |  |

| read array[3] (hit)  | {array[2], array[3]}      |  |  |  |  |

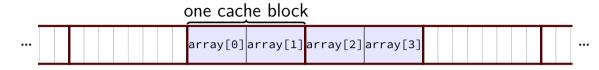

## some possiblities

one cache block

if array[0] starts right in the middle of a cache block array split across three cache blocks

| memory access        | cache contents afterwards |  |  |  |  |  |

|----------------------|---------------------------|--|--|--|--|--|

| _                    | (empty)                   |  |  |  |  |  |

| read array[0] (miss) | {****, array[0]}          |  |  |  |  |  |

| read array[1] (miss) | {array[1], array[2]}      |  |  |  |  |  |

| read array[2] (hit)  | {array[1], array[2]}      |  |  |  |  |  |

| read array[3] (miss) | {array[3], ++++}          |  |  |  |  |  |

if array[0] starts at an odd place in a cache block, need to read two cache blocks to get most array elements

| memory access                 | cache contents afterwards                        |  |  |  |  |  |

|-------------------------------|--------------------------------------------------|--|--|--|--|--|

| _                             | (empty)                                          |  |  |  |  |  |

| read array[0] byte 0 (miss)   | { ****, array[0] byte 0 }                        |  |  |  |  |  |

| read array[0] byte 1-3 (miss) | { array[0] byte 1-3, array[2], array[3] byte 0 } |  |  |  |  |  |

| read array[1] (hit)           | { array[0] byte 1-3, array[2], array[3] byte 0 } |  |  |  |  |  |

| read array[2] byte 0 (hit)    | { array[0] byte 1-3, array[2], array[3] byte 0 } |  |  |  |  |  |

| read array[2] byte 1-3 (miss) | {part of array[2], array[3], $++++$ }            |  |  |  |  |  |

| read array[3] (hit)           | {part of array[2], array[3], $++++$ }            |  |  |  |  |  |

## aside: alignment

compilers and malloc/new implementations usually try align values align = make address be multiple of something

most important reason: don't cross cache block boundaries

# C and cache misses (warmup 2)

```

int array[4];

int even_sum = 0, odd_sum = 0;

even_sum += array[0];

even_sum += array[2];

odd_sum += array[1];

odd_sum += array[3];

Assume everything but array is kept in registers (and the compiler does not do

```

anything funny).

Assume array[0] at beginning of cache block.

How many data cache misses on a 1-set direct-mapped cache with 8B blocks?

| memory access        | cache contents afterwards |  |  |  |  |  |

|----------------------|---------------------------|--|--|--|--|--|

| _                    | (empty)                   |  |  |  |  |  |

| read array[0] (miss) | {array[0], array[1]}      |  |  |  |  |  |

| read array[2] (miss) | {array[2], array[3]}      |  |  |  |  |  |

| read array[1] (miss) | {array[0], array[1]}      |  |  |  |  |  |

| read array[3] (miss) | {array[2], array[3]}      |  |  |  |  |  |

# C and cache misses (warmup 3)

```

int array[8];

...

int even_sum = 0, odd_sum = 0;

even_sum += array[0];

odd_sum += array[1];

even_sum += array[2];

odd_sum += array[3];

even_sum += array[4];

odd_sum += array[5];

even_sum += array[6];

odd_sum += array[7];

```

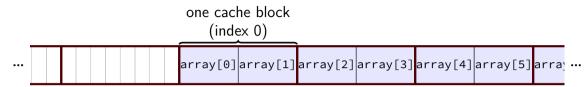

Assume everything but array is kept in registers (and the compiler does not do anything funny), and array[0] at beginning of cache block.

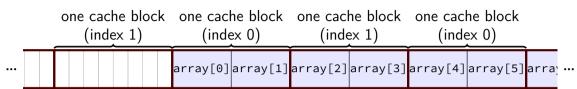

How many data cache misses on a **2**-set direct-mapped cache with 8B blocks?

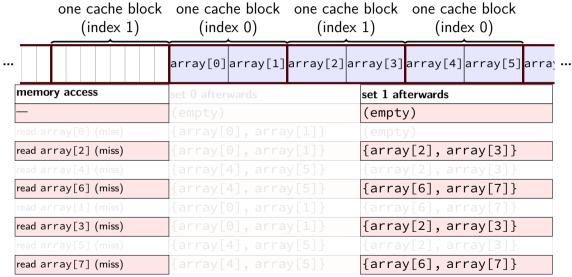

| one cache block<br>(index 1) | one cache block<br>(index 0) | one cach<br>(inde    |          | one cache block<br>(index 0) |          |                   |

|------------------------------|------------------------------|----------------------|----------|------------------------------|----------|-------------------|

|                              | array[0]array[1]             | array[2]a            | array[3] | array[4]                     | array[5] | arra <sub>j</sub> |

| memory access                | set 0 afterwards             |                      | set 1 af | terwards                     |          |                   |

| _                            | (empty)                      |                      | (empt    | y)                           |          |                   |

| read array[0] (miss)         | {array[0], arra              | y[1]}                | (empt    | y)                           |          |                   |

| read array[1] (hit)          | {array[0], arra              | y[1]}                | (empt    | y)                           |          |                   |

| read array[2] (miss)         | {array[0], arra              | y[1]}                | {arra    | y[2], ar                     | ray[3]}  |                   |

| read array[3] (hit)          | {array[0], arra              | y[1]}                | {arra    | y[2], ar                     | ray[3]}  |                   |

| read array[4] (miss)         | {array[4], arra              | y[5]}                | {arra    | y[2], ar                     | ray[3]}  |                   |

| read array[5] (hit)          | {array[4], arra              | {array[2], array[3]} |          |                              |          |                   |

| read array[6] (miss)         | {array[4], arra              | y[5]}                | {arra    | y[6],ar                      | ray[7]}  |                   |

| read array[7] (hit)          | {array[4], arra              | y[5]}                | {arra    | y[6],ar                      | ray[7]}  |                   |

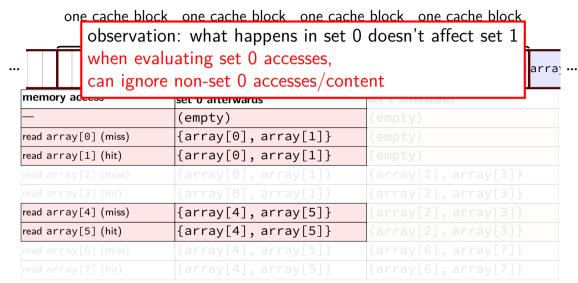

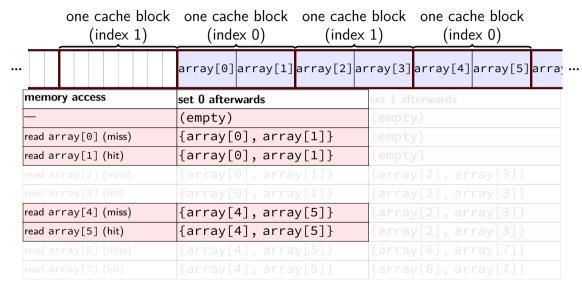

one cache block one cache block one cache block observation: what happens in set 0 doesn't affect set 1 when evaluating set 0 accesses, can ignore non-set 0 accesses/content memory adeess set u arterwarus set i aiterwarus (empty) (empty) {array[0], array[1]} read array[0] (miss) (empty) {array[0], array[1]} (empty) read array[1] (hit) {array[0], array[1]}  $\{array[2], array[3]\}$ read array[2] (miss) {array[0], array[1]}  $\{array[2], array[3]\}$ read array[3] (hit) read array[4] (miss)  $\{array[4], array[5]\}$  $\{array[2], array[3]\}$ {array[2], array[3]}  $\{array[4], array[5]\}$ read array[5] (hit) {array[6], array[7]}  $\{array[4], array[5]\}$ read array[6] (miss) {array[4], array[5]} {array[6], array[7]} read array[7] (hit)

| one cache block<br>(index 1) | one cache block<br>(index 0) |               | one cache block<br>(index 1) |          | one cache block<br>(index 0) |          |      |

|------------------------------|------------------------------|---------------|------------------------------|----------|------------------------------|----------|------|

|                              | array[0                      | ]<br>array[1] | array[2]                     | array[3] | array[4]                     | array[5] | arra |

| memory access                | set 0 afte                   | rwards        | •                            | set 1 af | terwards                     |          |      |

| _                            | (empty)                      |               |                              | (empt    | y)                           |          |      |

| read array[0] (miss)         | {array                       |               |                              | (empt    | у)                           |          |      |

|                              | {array                       |               |                              | (empt    |                              |          |      |

| read array[2] (miss)         | {array                       | [0], arra     |                              | {arra    | y[2], ar                     | ray[3]}  |      |

| read array[3] (hit)          | {array                       | [0], arra     |                              | {arra    | y[2], ar                     | ray[3]}  |      |

| read array[4] (miss)         | {array                       | [4], arra     |                              | {arra    | y[2], ar                     | ray[3]}  |      |

|                              | {array                       | [4], arra     |                              | {arra    |                              |          |      |

| read array[6] (miss)         | {array                       | [4], arra     |                              | {arra    | y[6], ar                     | ray[7]}  |      |

| read array[7] (hit)          | {array                       |               |                              | {arra    | y[6], ar                     | ray[7]}  |      |

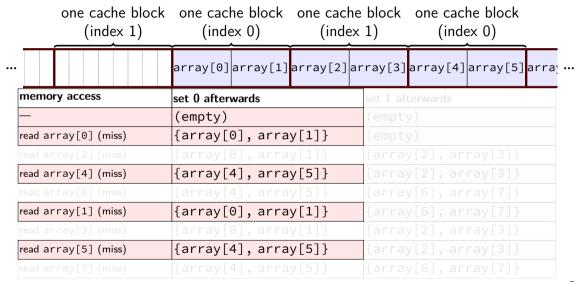

# C and cache misses (warmup 4a)

```

int array[8]; /* assume aligned */

int even sum = 0, odd sum = 0;

even sum += array[0];

even_sum += array[2];

even_sum += array[4];

even sum += array[6];

odd_sum += array[1];

odd_sum += array[3];

odd_sum += array[5];

odd sum += array[7];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on a **2**-set direct-mapped cache with 8B blocks?

| one cache<br>(index : | block one cac<br>1) (ind | he block<br>ex 0)    |          | ne block<br>ex 1) |                      | he block<br>ex 0) |                   |  |

|-----------------------|--------------------------|----------------------|----------|-------------------|----------------------|-------------------|-------------------|--|

|                       | array[0]                 | array[1]             | array[2] | array[3]          | array[4]             | array[5]          | arra <sub>!</sub> |  |

| memory access         | set 0 after              | rwards               |          | set 1 af          | terwards             |                   |                   |  |

| _                     | (empty)                  |                      |          | (empt             | у)                   |                   |                   |  |

| read array[0] (miss)  | {array[                  | [0], arra            | y[1]}    | (empt             | у)                   |                   |                   |  |

| read array[2] (miss)  | {array[                  | [0], arra            | y[1]}    | {arra             | y[2],ar              | ray[3]}           |                   |  |

| read array[4] (miss)  | {array[                  | [4], arra            | y[5]}    | {arra             | y[2],ar              | ray[3]}           |                   |  |

| read array[6] (miss)  | {array[                  | [4], arra            | y[5]}    | {arra             | y[6],ar              | ray[7]}           |                   |  |

| read array[1] (miss)  | {array[                  | {array[0], array[1]} |          |                   | {array[6], array[7]} |                   |                   |  |

| read array[3] (miss)  | {array[                  | {array[0], array[1]} |          |                   | {array[2], array[3]} |                   |                   |  |

| read array[5] (miss)  | {array[                  | {array[4], array[5]} |          |                   | {array[2], array[3]} |                   |                   |  |

| read array[7] (miss)  | {array[                  | [4], arra            | y[5]}    | {arra             | {array[6], array[7]} |                   |                   |  |

# C and cache misses (warmup 4b)

```

int array[8]; /* assume aligned */

int even_sum = 0, odd_sum = 0;

even sum += array[0];

odd_sum += array[3];

even_sum += array[6];

odd sum += array[1];

even_sum += array[4];

odd sum += array[7];

even_sum += array[2]:

odd sum += array[5];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on a **2**-set direct-mapped cache with 8B blocks?

# C and cache misses (warmup 5)

```

int array[1024]; /* assume aligned */ int even = 0, odd = 0;

even += array[0];

even += array[2];

even += array[512];

even += array[514];

odd += array[1];

odd += array[3];

odd += array[511];

odd += array[513];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

observation: array[0] and array[512] exactly 2KB apart

How many data cache misses on a 2KB direct mapped cache with 16B blocks?

## C and cache misses (warmup 6)

```

int array[1024]; /* assume aligned */ int even = 0, odd = 0;

even += array[0];

even += array[2];

even += array[500];

even += array[502];

odd += array[1];

odd += array[3];

odd += array[501];

odd += array[503];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on a 2KB direct mapped cache with 16B blocks?

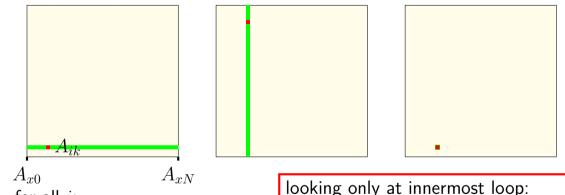

## misses with skipping

```

int array1[512]; int array2[512];

...

for (int i = 0; i < 512; i += 1)

sum += array1[i] * array2[i];

}</pre>

```

Assume everything but array1, array2 is kept in registers (and the compiler does not do anything funny).

About how many data cache misses on a 2KB direct-mapped cache with 16B cache blocks?

Hint: depends on relative placement of array1, array2

## best/worst case

```

array1[i] and array2[i] always different sets:

```

= distance from array1 to array2 not multiple of # sets  $\times$  bytes/set 2 misses every 4 i blocks of 4 array1[X] values loaded, then used 4 times before loading next block (and same for array2[X])

#### array1[i] and array2[i] same sets:

= distance from array1 to array2 is multiple of # sets  $\times$  bytes/set 2 misses every i block of 4 array1[X] values loaded, one value used from it, then, block of 4 array2[X] values replaces it, one value used from it, ...

### worst case in practice?

two rows of matrix?

often sizeof(row) bytes apart

if the row size is multiple of number of sets  $\times$  bytes per block, oops!

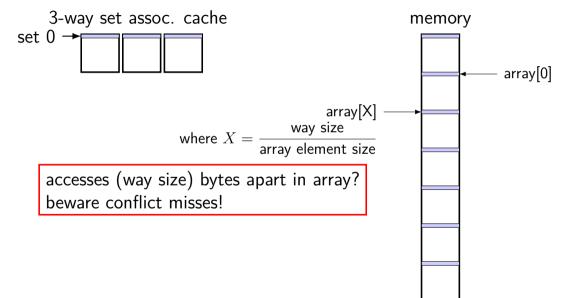

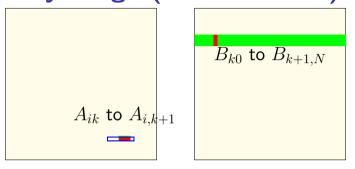

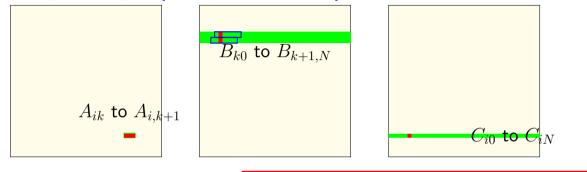

## mapping of sets to memory (3-way)

## mapping of sets to memory (3-way)

## mapping of sets to memory (3-way)

# mapping of sets to memory (3-way)

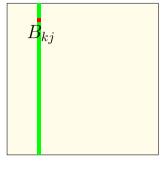

### misses with skipping

```

int array1[512]; int array2[512];

...

for (int i = 0; i < 512; i += 1)

sum += array1[i] * array2[i];

}</pre>

```

Assume everything but array1, array2 is kept in registers (and the compiler does not do anything funny).

About how many data cache misses on a 2KB direct-mapped cache with 16B cache blocks?

Hint: depends on relative placement of array1, array2

How about on a two-way set associative cache?

# C and cache misses (assoc)

```

int array[1024]; /* assume aligned */

int even_sum = 0, odd_sum = 0;

even_sum += array[0];

even_sum += array[2];

even_sum += array[512];

even_sum += array[514];

odd_sum += array[1];

odd_sum += array[3];

odd_sum += array[511];

odd_sum += array[513];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

opbservation: array[0], array[256], array[512], array[768] in same set How many data cache misses on a 2KB 2-way set associative cache with 16B blocks

# C and cache misses (assoc)

```

int array[1024]; /* assume aligned */

int even_sum = 0, odd_sum = 0;

even_sum += array[0];

even_sum += array[256];

even_sum += array[512];

even_sum += array[768];

odd_sum += array[1];

odd_sum += array[257];

odd_sum += array[513];

odd_sum += array[769];

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

observation: array[0], array[256], array[512], array[768] in same set How many data cache misses on a 2KB 2-way set associative cache with 16B blocks?

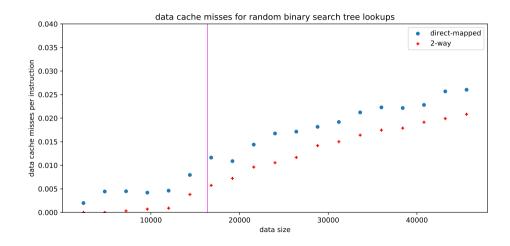

## simulated misses: BST lookups

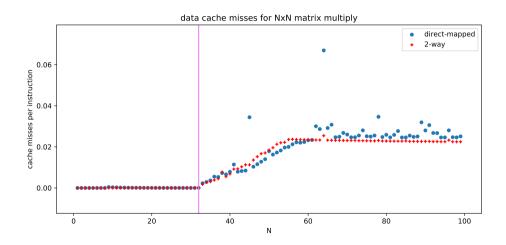

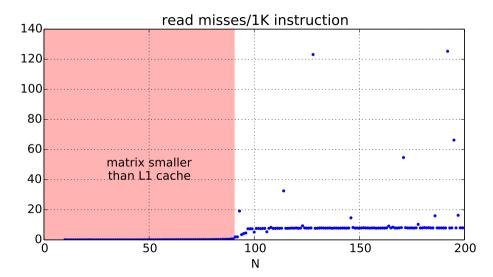

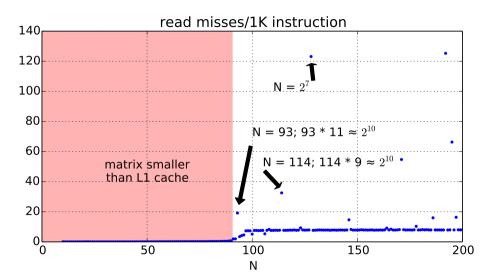

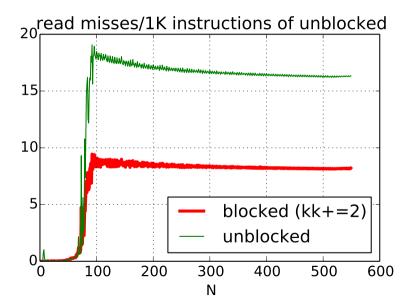

### simulated misses: matrix multiplies

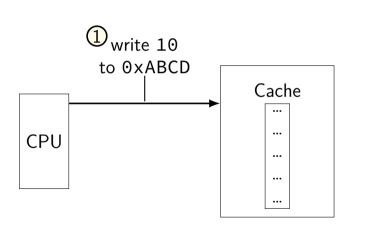

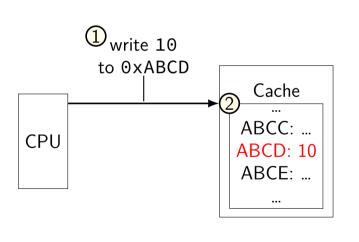

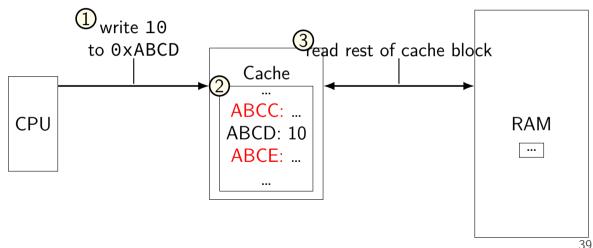

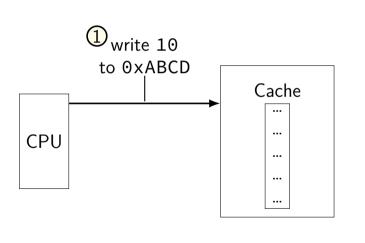

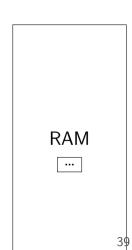

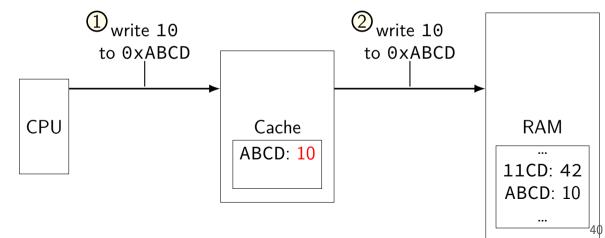

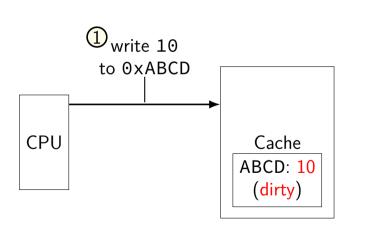

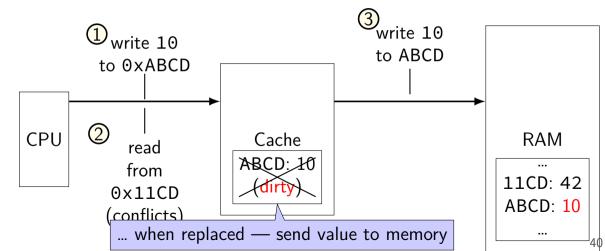

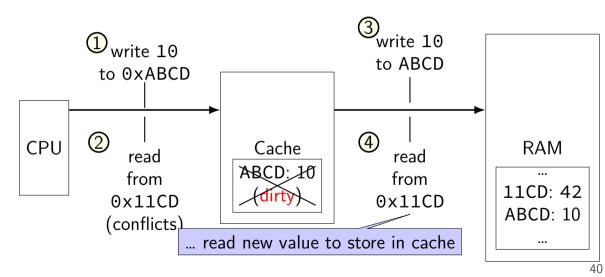

### handling writes

what about writing to the cache?

two decision points:

if the value is not in cache, do we add it?

if yes: need to load rest of block — write-allocate

if no: missing out on locality? write-no-allocate

if value is in cache, when do we update next level?

if immediately: extra writing write-through

if later: need to remember to do so write-back

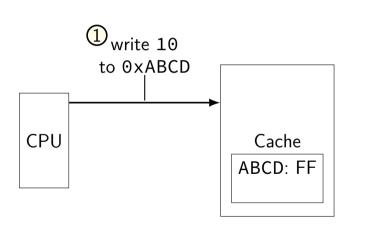

#### allocate on write?

processor writes less than whole cache block

block not yet in cache

two options:

#### write-allocate

fetch rest of cache block, replace written part (then follow write-through or write-back policy)

#### write-no-allocate

don't use cache at all (send write to memory *instead*) guess: not read soon?

#### allocate on write?

processor writes less than whole cache block

block not yet in cache

two options:

#### write-allocate

fetch rest of cache block, replace written part (then follow write-through or write-back policy)

#### write-no-allocate

don't use cache at all (send write to memory *instead*) guess: not read soon?

#### option 1: write-allocate

#### option 1: write-allocate

option 2: write-no-allocate

option 2: write-no-allocate

option 1: write-through

option 1: write-through

option 2: write-back

option 2: write-back

### writeback policy

changed value!

2-way set associative, 4 byte blocks, 2 sets

| index | valid | tag    | value                  | dirty | valid | tag    | value                 | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|-----------------------|-------|-----|

| 0     | 1     | 000000 | mem[0x00]<br>mem[0x01] | 0     | 1     | 011000 | mem[0×60]* mem[0×61]* | 1     | 1   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 0     |        |                       |       | 0   |

1 = dirty (different than memory) needs to be written if evicted

2-way set associative, LRU, writeback

| index | valid | tag | value                  | dirty | valid | tag | value                  | dirty | LRU |

|-------|-------|-----|------------------------|-------|-------|-----|------------------------|-------|-----|

| 0     | 1     |     | mem[0x00]<br>mem[0x01] |       | 1     |     | mem[0x60]<br>mem[0x61] |       | 1   |

| 1     | 1     |     | mem[0x62]<br>mem[0x63] |       | 0     |     |                        |       | 0   |

writing 0xFF into address 0x04? index 0, tag 000001

2-way set associative, LRU, writeback

| index | valid | tag | value                  | dirty | valid | tag | value                  | dirty | LRU |

|-------|-------|-----|------------------------|-------|-------|-----|------------------------|-------|-----|

| 0     | 1     |     | mem[0x00]<br>mem[0x01] |       | 1     |     | mem[0x60]<br>mem[0x61] |       | 1   |

| 1     | 1     |     | mem[0x62]<br>mem[0x63] |       | 0     |     |                        |       | 0   |

writing 0xFF into address 0x04?

index 0, tag 000001

step 1: find least recently used block

2-way set associative, LRU, writeback

| index | valid | tag | value                  | dirty | valid | tag    | value                  | dirty          | LRU |

|-------|-------|-----|------------------------|-------|-------|--------|------------------------|----------------|-----|

| 0     | 1     |     | mem[0x00]<br>mem[0x01] |       | 1     | 011000 | mem[0x60]<br>mem[0x61] | * <del>1</del> | 1   |

| 1     | 1     |     | mem[0x62]<br>mem[0x63] |       | 0     |        |                        |                | 0   |

writing 0xFF into address 0x04?

index 0, tag 000001

step 1: find least recently used block

step 2: possibly writeback old block

2-way set associative, LRU, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value             | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|-------------------|-------|-----|

| 0     | 1     |        | mem[0x00]<br>mem[0x01] | 0     | 1     | 000001 | 0xFF<br>mem[0x05] | 1     | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 0     |        |                   |       | 0   |

writing 0xFF into address 0x04?

index 0, tag 000001

step 1: find least recently used block

step 2: possibly writeback old block

step 3a: read in new block – to get mem[0x05]

step 3b: update LRU information

2-way set associative, LRU, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                  | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|------------------------|-------|-----|

| 0     | 1     | 000000 | mem[0x00]<br>mem[0x01] | 0     | 1     | 011000 | mem[0x60]<br>mem[0x61] | * 1   | 1   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 0     |        |                        |       | 0   |

writing 0xFF into address 0x04?

step 1: is it in cache yet?

step 2: no, just send it to memory

# exercise (1)

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                  | dirty      | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|------------------------|------------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 0     | 1     | 010000 | mem[0x40]<br>mem[0x41] | * <b>1</b> | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 001100 | mem[0x32]<br>mem[0x33] | * <b>1</b> | 1   |

for each of the following accesses, performed alone, would it require (a) reading a value from memory (or next level of cache) and (b) writing a value to the memory (or next level of cache)?

writing 1 byte to 0x33 reading 1 byte from 0x52 reading 1 byte from 0x50

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                 | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|-----------------------|-------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 0     | 1     | 010000 | mem[0x40]* mem[0x41]* | 1     | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 001100 | mem[0x32]* mem[0x33]* | 1     | 1   |

writing 1 byte to 0x33: (set 1, offset 1) no read or write

reading 1 byte from 0x52:

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                    | dirty | LRU            |

|-------|-------|--------|------------------------|-------|-------|--------|--------------------------|-------|----------------|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 0     | 1     | 010000 | mem[0x40]* mem[0x41]*    | 1     | 0              |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 001100 | mem[0x32]*<br>mem[0x33]* | 1     | <del>1</del> 0 |

writing 1 byte to  $0\times33$ : (set 1, offset 1) no read or write

reading 1 byte from 0x52:

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                 | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|-----------------------|-------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 0     | 1     | 010000 | mem[0x40]* mem[0x41]* | 1     | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 001100 | mem[0x32]* mem[0x33]* | 1     | 1   |

writing 1 byte to 0x33: (set 1, offset 1) no read or write

reading 1 byte from 0x52: (set 1, offset 0) write back 0x32-0x33; read 0x52-0x53

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                  | dirty          | LRU            |

|-------|-------|--------|------------------------|-------|-------|--------|------------------------|----------------|----------------|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 0     | 1     | 010000 | mem[0x40]* mem[0x41]*  | 1              | 0              |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 101000 | mem[0x52]<br>mem[0x53] | <del>1</del> 0 | <del>1</del> 0 |

writing 1 byte to 0x33: (set 1, offset 1) no read or write

reading 1 byte from 0x52: (set 1, offset 0) write back 0x32-0x33; read 0x52-0x53

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                 | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|-----------------------|-------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 0     | 1     | 010000 | mem[0x40]* mem[0x41]* | 1     | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 001100 | mem[0x32]* mem[0x33]* | 1     | 1   |

writing 1 byte to 0x33: (set 1, offset 1) no read or write

reading 1 byte from 0x52: (set 1, offset 0) **write** back 0x32-0x33; **read** 0x52-0x53

reading 1 byte from 0x50: (set 0, offset 0) replace 0x30-0x31 (no write back); **read** 0x50-0x51

2-way set associative, LRU, write-allocate, writeback

| index | valid | tag    | value                  | dirty | valid | tag    | value                 | dirty | LRU |

|-------|-------|--------|------------------------|-------|-------|--------|-----------------------|-------|-----|

| 0     | 1     | 101000 | mem[0x50]<br>mem[0x51] | 0     | 1     | 010000 | mem[0x40]* mem[0x41]* | 1     | 01  |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 0     | 1     | 001100 | mem[0x32]* mem[0x33]* | 1     | 1   |

writing 1 byte to 0x33: (set 1, offset 1) no read or write

reading 1 byte from 0x52: (set 1, offset 0) **write** back 0x32-0x33; **read** 0x52-0x53

reading 1 byte from 0x50: (set 0, offset 0) replace 0x30-0x31 (no write back); **read** 0x50-0x51

# exercise (2)

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU |

|-------|-------|--------|------------------------|-------|--------|------------------------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 001100 | mem[0x32]<br>mem[0x33] | 1   |

for each of the following accesses, performed alone, would it require (a) reading a value from memory and (b) writing a value to the memory?

writing 1 byte to 0x33 reading 1 byte from 0x52 reading 1 byte from 0x50

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU |

|-------|-------|--------|------------------------|-------|--------|------------------------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 001100 | mem[0x32]<br>mem[0x33] | 1   |

writing 1 byte to 0x33: (set 1, offset 1) write-through 0x33 modification

reading 1 byte from 0x52:

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU            |

|-------|-------|--------|------------------------|-------|--------|------------------------|----------------|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 0              |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 001100 | mem[0x32]<br>mem[0x33] | <del>1</del> 0 |

writing 1 byte to 0x33: (set 1, offset 1) write-through 0x33 modification

reading 1 byte from 0x52:

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU |

|-------|-------|--------|------------------------|-------|--------|------------------------|-----|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 0   |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 001100 | mem[0x32]<br>mem[0x33] | 1   |

writing 1 byte to 0x33: (set 1, offset 1) write-through 0x33 modification

reading 1 byte from 0x52: (set 1, offset 0) replace 0x32-0x33; **read** 0x52-0x53

reading 1 byte from 0x50:

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU            |

|-------|-------|--------|------------------------|-------|--------|------------------------|----------------|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 0              |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 101000 | mem[0x52]<br>mem[0x53] | <del>1</del> 0 |

writing 1 byte to 0x33: (set 1, offset 1) write-through 0x33 modification

reading 1 byte from 0x52: (set 1, offset 0) replace 0x32-0x33; **read** 0x52-0x53

reading 1 byte from 0x50:

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU |  |

|-------|-------|--------|------------------------|-------|--------|------------------------|-----|--|

| 0     | 1     | 001100 | mem[0x30]<br>mem[0x31] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 0   |  |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 001100 | mem[0x32]<br>mem[0x33] | 1   |  |

writing 1 byte to  $0\times33$ : (set 1, offset 1) write-through  $0\times33$  modification

reading 1 byte from 0x52: (set 1, offset 0) replace 0x32-0x33; **read** 0x52-0x53

reading 1 byte from 0x50: (set 0, offset 0) replace 0x30-0x31; read 0x50-0x51

2-way set associative, LRU, write-no-allocate, write-through

| index | valid | tag    | value                  | valid | tag    | value                  | LRU |

|-------|-------|--------|------------------------|-------|--------|------------------------|-----|

| 0     | 1     | 101000 | mem[0x50]<br>mem[0x51] | 1     | 010000 | mem[0x40]<br>mem[0x41] | 01  |

| 1     | 1     | 011000 | mem[0x62]<br>mem[0x63] | 1     | 001100 | mem[0x32]<br>mem[0x33] | 1   |

writing 1 byte to  $0\times33$ : (set 1, offset 1) write-through  $0\times33$  modification

reading 1 byte from 0x52: (set 1, offset 0) replace 0x32-0x33; **read** 0x52-0x53

reading 1 byte from 0x50: (set 0, offset 0) replace 0x30-0x31; read 0x50-0x51

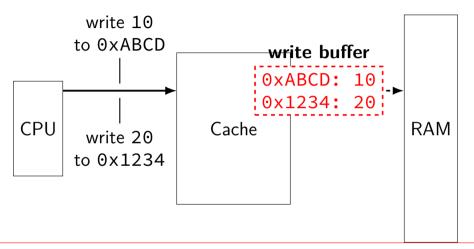

# backup slides

#### fast writes

write appears to complete immediately when placed in buffer memory can be much slower

#### cache tradeoffs briefly

deciding cache size, associativity, etc.?

#### lots of tradeoffs:

more cache hits v. slower cache hits? faster cache hits v. fewer cache hits? more cache hits v. slower cache misses?

#### details depend on programs run

how often is same block used again? how often is same index bits used?

simulation to assess impact of designs

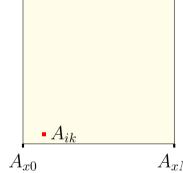

# arrays and cache misses (1)

```

int array[1024]; // 4KB array

int even_sum = 0, odd_sum = 0;

for (int i = 0; i < 1024; i += 2) {

even_sum += array[i + 0];

odd_sum += array[i + 1];

}</pre>

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on initially empty 2KB direct-mapped cache with 16B cache blocks?

# arrays and cache misses (2)

```

int array[1024]; // 4KB array

int even_sum = 0, odd_sum = 0;

for (int i = 0; i < 1024; i += 2)

even_sum += array[i + 0];

for (int i = 0; i < 1024; i += 2)

odd_sum += array[i + 1];</pre>

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on initially empty 2KB direct-mapped cache with 16B cache blocks?

# arrays and cache misses (2b)

```

int array[1024]; // 4KB array

int even_sum = 0, odd_sum = 0;

for (int i = 0; i < 1024; i += 2)

even_sum += array[i + 0];

for (int i = 0; i < 1024; i += 2)

odd_sum += array[i + 1];</pre>

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many data cache misses on initially empty 4KB direct-mapped cache with 16B cache blocks?

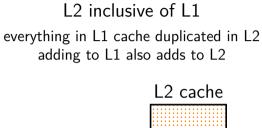

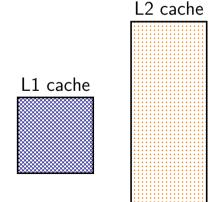

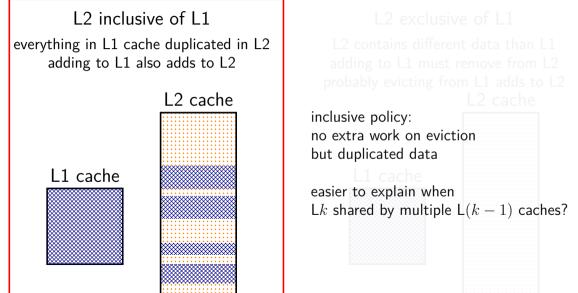

#### inclusive versus exclusive

#### inclusive versus exclusive

#### inclusive versus exclusive

L2 inclusive of L1

everything in L1 cache duplicated in L2 adding to L1 also adds to L2

L2 cache

exclusive policy:

avoid duplicated data

sometimes called *victim cache*(contains cache eviction victims)

makes less sense with multicore

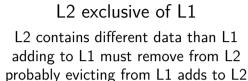

#### L2 exclusive of L1

L2 contains different data than L1 adding to L1 must remove from L2 probably evicting from L1 adds to L2 L2 cache

### Tag-Index-Offset formulas (direct-mapped)

(formulas derivable from prior slides)

$$S=2^s$$

number of sets  $s$  (set) index bits  $B=2^b$  block size  $b$  (block) offset bits

$$t = m - (s + b)$$

tag bits

m

$$C = B \times S$$

cache size (if direct-mapped)

memory addreses bits

### **Tag-Index-Offset formulas (direct-mapped)**

(formulas derivable from prior slides)

$$S = 2^s$$

number of sets

(set) index bits

$$B=2^b$$

block size

(block) offset bits

m

memory addreses bits

```

t = m - (s + b) tag bits

```

$C = B \times S$  cache size (if direct-mapped)

#### cache organization and miss rate

depends on program; one example:

SPEC CPU2000 benchmarks, 64B block size

LRU replacement policies

-lata cacha mica katasi

| data cache | miss rates:   |        |         |              |

|------------|---------------|--------|---------|--------------|

| Cache size | direct-mapped | 2-way  | 8-way   | fully assoc. |

| 1KB        | 8.63%         | 6.97%  | 5.63%   | 5.34%        |

| 2KB        | 5.71%         | 4.23%  | 3.30%   | 3.05%        |

| 4KB        | 3.70%         | 2.60%  | 2.03%   | 1.90%        |

| 16KB       | 1.59%         | 0.86%  | 0.56%   | 0.50%        |

| 64KB       | 0.66%         | 0.37%  | 0.10%   | 0.001%       |

| 128KB      | 0.27%         | 0.001% | 0.0006% | 0.0006%      |

Data: Cantin and Hill, "Cache Performance for SPEC CPU2000 Benchmarks" http://research.cs.wisc.edu/multifacet/misc/spec2000cache-data/

#### cache organization and miss rate

depends on program; one example:

SPEC CPU2000 benchmarks, 64B block size

#### LRU replacement policies

| miss rates:   |                                                            |                                                                                                |                                                                                                                                                                                                                                     |

|---------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| direct-mapped | 2-way                                                      | 8-way                                                                                          | fully assoc.                                                                                                                                                                                                                        |

| 8.63%         | 6.97%                                                      | 5.63%                                                                                          | 5.34%                                                                                                                                                                                                                               |

| 5.71%         | 4.23%                                                      | 3.30%                                                                                          | 3.05%                                                                                                                                                                                                                               |

| 3.70%         | 2.60%                                                      | 2.03%                                                                                          | 1.90%                                                                                                                                                                                                                               |

| 1.59%         | 0.86%                                                      | 0.56%                                                                                          | 0.50%                                                                                                                                                                                                                               |

| 0.66%         | 0.37%                                                      | 0.10%                                                                                          | 0.001%                                                                                                                                                                                                                              |

| 0.27%         | 0.001%                                                     | 0.0006%                                                                                        | 0.0006%                                                                                                                                                                                                                             |

|               | direct-mapped<br>8.63%<br>5.71%<br>3.70%<br>1.59%<br>0.66% | direct-mapped 2-way<br>8.63% 6.97%<br>5.71% 4.23%<br>3.70% 2.60%<br>1.59% 0.86%<br>0.66% 0.37% | direct-mapped       2-way       8-way         8.63%       6.97%       5.63%         5.71%       4.23%       3.30%         3.70%       2.60%       2.03%         1.59%       0.86%       0.56%         0.66%       0.37%       0.10% |

### exercise (1)

initial cache: 64-byte blocks, 64 sets, 8 ways/set

If we leave the other parameters listed above unchanged, which will probably reduce the number of capacity misses in a typical program? (Multiple may be correct.)

- A. quadrupling the block size (256-byte blocks, 64 sets, 8 ways/set)

- B. quadrupling the number of sets

- C. quadrupling the number of ways/set

# exercise (2)

initial cache: 64-byte blocks, 8 ways/set, 64KB cache

If we leave the other parameters listed above unchanged, which will probably reduce the number of capacity misses in a typical program? (Multiple may be correct.)

- A. quadrupling the block size (256-byte block, 8 ways/set, 64KB cache)

- B. quadrupling the number of ways/set

- C. quadrupling the cache size

# exercise (3)

initial cache: 64-byte blocks, 8 ways/set, 64KB cache

If we leave the other parameters listed above unchanged, which will probably reduce the number of conflict misses in a typical program? (Multiple may be correct.)

- A. quadrupling the block size (256-byte block, 8 ways/set, 64KB cache)

- B. quadrupling the number of ways/set

- C. quadrupling the cache size

#### prefetching

seems like we can't really improve cold misses...

have to have a miss to bring value into the cache?

#### prefetching

seems like we can't really improve cold misses...

have to have a miss to bring value into the cache?

solution: don't require miss: 'prefetch' the value before it's accessed

remaining problem: how do we know what to fetch?

#### common access patterns

suppose recently accessed 16B cache blocks are at: 0x48010, 0x48020, 0x48030, 0x48040

guess what's accessed next

#### common access patterns

suppose recently accessed 16B cache blocks are at: 0x48010, 0x48020, 0x48030, 0x48040

guess what's accessed next

common pattern with instruction fetches and array accesses

#### prefetching idea

look for sequential accesses

bring in guess at next-to-be-accessed value

if right: no cache miss (even if never accessed before)

if wrong: possibly evicted something else — could cause more misses

fortunately, sequential access guesses almost always right

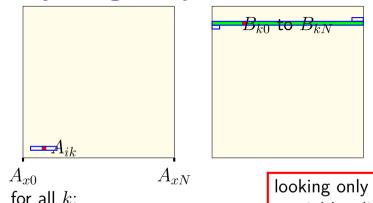

#### quiz exercise solution

one cache block one cache block one cache block (set index 1) (set index 0) (set index 1) (set index 0)

array[0]|array[1]|array[2]|array[3]|array[4]|array[5]|array[6]|array[7]|array

| memory access        | set 0 afterwards     | set 1 afterwards     |

|----------------------|----------------------|----------------------|

| _                    | (empty)              | (empty)              |

| read array[0] (miss) | {array[0], array[1]} | (empty)              |

| read array[3] (miss) | {array[0], array[1]} | {array[2], array[3]} |

| read array[6] (miss) | {array[0], array[1]} | {array[6], array[7]} |

| read array[1] (hit)  | {array[0], array[1]} | {array[6], array[7]} |

| read array[4] (miss) | {array[4], array[5]} | {array[6], array[7]} |

| read array[7] (hit)  | {array[4], array[5]} | {array[6], array[7]} |

| read array[2] (miss) | {array[4], array[5]} | {array[2], array[3]} |

|                      | C [4] [=])           | ( [-1]               |

#### quiz exercise solution

one cache block one cache block one cache block (set index 1) (set index 0) (set index 1) (set index 0)

array[0]array[1]array[2]array[3]array[4]array[5]array[6]array[7]array

| memory access        | set 0 afterwards     | set 1 afterwards     |

|----------------------|----------------------|----------------------|

| _                    | (empty)              | (empty)              |

| read array[0] (miss) | {array[0], array[1]} | (empty)              |

| read array[3] (miss) | {array[0], array[1]} | {array[2], array[3]} |

|                      | {array[0], array[1]} | {array[6],array[7]}  |

| read array[1] (hit)  | {array[0], array[1]} | {array[6], array[7]} |

| read array[4] (miss) | {array[4], array[5]} | {array[6], array[7]} |

| read array[7] (hit)  | {array[4], array[5]} | {array[6],array[7]}  |

|                      | {array[4],array[5]}  | {array[2],array[3]}  |

| read array(E] (hit)  | [2rr2v[4] 2rr2v[5]]  | [array[6] array[7]]  |

#### quiz exercise solution

one cache block one cache block one cache block (set index 1) (set index 0) (set index 1) (set index 0)

array[0] array[1] array[2] array[3] array[4] array[5] array[6] array[7] array

| memory access        | set 0 afterwards     | set 1 afterwards      |

|----------------------|----------------------|-----------------------|

| _                    | (empty)              | (empty)               |

| read array[0] (miss) | {array[0], array[1]} | (empty)               |

| read array[3] (miss) | {array[0], array[1]} | {array[2], array[3]}  |

| read array[6] (miss) | {array[0], array[1]} | {array[6], array[7]}  |

| read array[1] (hit)  | {array[0], array[1]} | {array[6],array[7]}   |

|                      | {array[4], array[5]} | {array[6], array[7]}  |

| read array[7] (hit)  | {array[4], array[5]} | {array[6], array[7]}  |

| read array[2] (miss) | {array[4], array[5]} | {array[2], array[3]}  |

| 1 FE3 (L.)           | [000001[4] 00001[5]] | [08801/[6] 08801/[7]] |

#### not the quiz problem

one cache block one cache block one cache bloc one cache block

array[0] array[1] array[2] array[3] array[4] array[5] array[6] array[7] array

if 1-set 2-way cache instead of 2-set 1-way cache:

| memory access        | single set with 2-ways, LRU first          |

|----------------------|--------------------------------------------|

| _                    | ,                                          |

| read array[0] (miss) | , {array[0], array[1]}                     |

| read array[3] (miss) | {array[0], array[1]}, {array[2], array[3]} |

| read array[6] (miss) | {array[2], array[3]}, {array[6], array[7]} |

| read array[1] (miss) | {array[6], array[7]}, {array[0], array[1]} |

| read array[4] (miss) | {array[0], array[1]}, {array[3], array[4]} |

| read array[7] (miss) | {array[3], array[4]}, {array[6], array[7]} |

| read array[2] (miss) | {array[6], array[7]}, {array[2], array[3]} |

| read array[5] (miss) | {array[2], array[3]}, {array[5], array[6]} |

| read array[8] (miss) | {array[5], array[6]}, {array[8], array[9]} |

70

# C and cache misses (4)

```

typedef struct {

int a value, b value;

int other values[6];

} item:

item items[5];

int a sum = 0, b sum = 0;

for (int i = 0; i < 5; ++i)

a sum += items[i].a value;

for (int i = 0; i < 5; ++i)

b sum += items[i].b value:

```

Assume everything but items is kept in registers (and the compiler does not do anything funny).

# C and cache misses (4, rewrite)

```

int array[40]

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 40; i += 8)

a_sum += array[i];

for (int i = 1; i < 40; i += 8)

b_sum += array[i];</pre>

```

Assume everything but array is kept in registers (and the compiler does not do anything funny) and array starts at beginning of cache block.

How many *data cache misses* on a 2-way set associative 128B cache with 16B cache blocks and LRU replacement?

# C and cache misses (4, solution pt 1)

```

ints 4 byte \rightarrow array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

```

accessing 0, 8, 16, 24, 32, 1, 9, 17, 25, 33

# C and cache misses (4, solution pt 1)

1 (set 0), 9 (set 2), 17 (set 0), 25 (set 2), 33 (set 0)

```

ints 4 byte \rightarrow array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total accessing 0, 8, 16, 24, 32, 1, 9, 17, 25, 33 0 (set 0), 8 (set 2), 16 (set 0), 24 (set 2), 32 (set 0)

```

# C and cache misses (4, solution pt 2)

```

set 0 after (LRU first)

result

access

arrav[0] —. arrav[0 to 3]

miss

array[16] array[0 to 3], array[16 to 19]

miss

6 misses for set 0

array[32]

array[16 to 19], array[32 to 35]

miss

array[32 to 35], array[0 to 3]

array[1]

miss

array[17]

array[0 to 3], array[16 to 19]

miss

array[16 to 19], array[32 to 35]

arrav[32]

miss

```

# C and cache misses (4, solution pt 3)

```

access set 2 after (LRU first) result

— —, —

array[8] —, array[8 to 11] miss

array[24] array[8 to 11], array[24 to 27] miss

array[9] array[8 to 11], array[24 to 27] hit

array[25] array[16 to 19], array[32 to 35] hit

```

# C and cache misses (3)

```

typedef struct {

int a_value, b_value;

int other values[10];

} item;

item items[5]:

int a sum = 0, b sum = 0;

for (int i = 0; i < 5; ++i)

a sum += items[i].a value:

for (int i = 0; i < 5; ++i)

b sum += items[i].b value:

observation: 12 ints in struct: only first two used

```

equivalent to accessing array[0], array[12], array[24], etc.

...then accessing array[1], array[13], array[25], etc.

76

## C and cache misses (3, rewritten?)

```

int array[60];

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 60; i += 12)

a_sum += array[i];

for (int i = 1; i < 60; i += 12)

b_sum += array[i];</pre>

```

Assume everything but array is kept in registers (and the compiler does not do anything funny) and array at beginning of cache block.

How many *data cache misses* on a 128B two-way set associative cache with 16B cache blocks and LRU replacement?

observation 1: first loop has 5 misses — first accesses to blocks observation 2: array[0] and array[1], array[12] and array[13], etc. in

## C and cache misses (3, solution)

```

ints 4 byte \rightarrow array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

```

accessing array indices 0, 12, 24, 36, 48, 1, 13, 25, 37, 49

```

so access to 1, 21, 41, 61, 81 all hits: set 0 contains block with array[0 to 3] set 5 contains block with array[20 to 23] etc.

```

## C and cache misses (3, solution)

```

ints 4 byte \rightarrow array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

```

accessing array indices 0, 12, 24, 36, 48, 1, 13, 25, 37, 49

```

so access to 1, 21, 41, 61, 81 all hits: set 0 contains block with array[0 to 3] set 5 contains block with array[20 to 23] etc.

```

## C and cache misses (3, solution)

```

ints 4 byte \rightarrow array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

```

accessing array indices 0, 12, 24, 36, 48, 1, 13, 25, 37, 49

```

0 (set 0, array[0 to 3]), 12 (set 3), 24 (set 2), 36 (set 1), 48 (set 0) each set used at most twice no replacement needed

```

```

so access to 1, 21, 41, 61, 81 all hits: set 0 contains block with array[0 to 3] set 5 contains block with array[20 to 23] etc.

```

## C and cache misses (3)

```

typedef struct {

int a value, b value;

int boring values[126];

} item;

item items[8]; // 4 KB array

int a sum = 0, b sum = 0;

for (int i = 0; i < 8; ++i)

a sum += items[i].a_value;

for (int i = 0; i < 8; ++i)

b sum += items[i].b value:

```

Assume everything but items is kept in registers (and the compiler does not do anything funny).

How many data cache misses on a 2KB direct-mapped cache with

## C and cache misses (3, rewritten?)

```

item array[1024]; // 4 KB array

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 1024; i += 128)

a_sum += array[i];

for (int i = 1; i < 1024; i += 128)

b_sum += array[i];</pre>

```

## C and cache misses (4)

```

typedef struct {

int a value, b value;

int boring values[126];

} item;

item items[8]; // 4 KB array

int a sum = 0, b sum = 0;

for (int i = 0; i < 8; ++i)

a_sum += items[i].a_value;

for (int i = 0; i < 8; ++i)

b sum += items[i].b value:

```

direct manned cache with 16R cache blocks?

Assume everything but items is kept in registers (and the compiler does not do anything funny).

How many data cache misses on a 4-way set associative 2KB

81

2KB direct-mapped cache with 16B blocks —

set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ...

```

set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ...

```

...

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ...

2KB direct-mapped cache with 16B blocks —

set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ...

```

set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ...

```

...

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ...

2KB direct-mapped cache with 16B blocks —

```

set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ... block at 0: array[0] through array[3]

```

```

set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ... block at 16: array[4] through array[7]

```

...

```

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ... block at 2032: array[508] through array[511]

```

2KB direct-mapped cache with 16B blocks —

```

set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ... block at 0: array[0] through array[3] block at 0+2KB: array[512] through array[515]

```

```

set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ... block at 16: array[4] through array[7] block at 16+2KB: array[516] through array[519]

```

...

```

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ... block at 2032: array[508] through array[511] block at 2032+2KB: array[1020] through array[1023]

```

2KB 2-way set associative cache with 16B blocks: block addresses

set 0: address 0, 0 + 2KB, 0 + 4KB, ...

```

set 1: address 16, 16 + 2KB, 16 + 4KB, ...

```

...

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ...

2KB 2-way set associative cache with 16B blocks: block addresses

set 0: address 0, 0 + 2KB, 0 + 4KB, ... block at 0: array[0] through array[3]

```

set 1: address 16, 16 + 2KB, 16 + 4KB, ... address 16: array[4] through array[7]

```

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ... address 1008: array[252] through array[255]

2KB 2-way set associative cache with 16B blocks: block addresses

```

block at 0+1KB: array[256] through array[259] block at 0+2KB: array[512] through array[515] ... set 1: address 16, 16+2KB, 16+4KB, ... address 16: array[4] through array[7]

```

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ... address 1008: array[252] through array[255]

set 0: address 0, 0 + 2KB, 0 + 4KB, ... block at 0: array[0] through array[3]

83

2KB 2-way set associative cache with 16B blocks: block addresses

```

block at 0+1KB: array[256] through array[259] block at 0+2KB: array[512] through array[515] ... set 1: address 16, 16+2KB, 16+4KB, ... address 16: array[4] through array[7]

```

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ... address 1008: array[252] through array[255]

set 0: address 0, 0 + 2KB, 0 + 4KB, ... block at 0: array[0] through array[3]

83

## arrays and cache misses (3)

anything funny).

```

int sum; int array[1024]; // 4KB array

for (int i = 8; i < 1016; i += 1) {

int local_sum = 0;

for (int j = i - 8; j < i + 8; j += 1) {

local sum += array[i] * (i - i);

sum += (local_sum - array[i]);

Assume everything but array is kept in registers (and the compiler does not do

```

How many *data cache misses* on initially empty 2KB direct-mapped cache with 16B cache blocks?

#### Tag-Index-Offset exercise

```

m memory addreses bits (Y86-64: 64) E number of blocks per set ("ways") S=2^s number of sets s (set) index bits

```

$$B=2^b$$

block size

$$t = m - (s + b)$$

tag bits

$$C = B \times S \times E$$

cache size (excluding metadata)

#### My desktop:

L1 Data Cache: 32 KB, 8 blocks/set, 64 byte blocks

L2 Cache: 256 KB, 4 blocks/set, 64 byte blocks

L3 Cache: 8 MB, 16 blocks/set, 64 byte blocks

Divide the address 0x34567 into tag, index, offset for each cache.

| quantity           | value for L1                   |

|--------------------|--------------------------------|

| block size (given) | B=64Byte                       |

|                    | $B=2^b$ (b: block offset bits) |

| quantity           | value for L1                   |

|--------------------|--------------------------------|

| block size (given) | B = 64Byte                     |

|                    | $B=2^b$ (b: block offset bits) |

| block offset bits  | b = 6                          |

| quantity           | value for L1                     |

|--------------------|----------------------------------|

| block size (given) | B=64Byte                         |

|                    | $B=2^b$ (b: block offset bits)   |

| block offset bits  | b = 6                            |

| blocks/set (given) | E=8                              |

| cache size (given) | $C = 32KB = E \times B \times S$ |

| quantity           | value for L1                                    |

|--------------------|-------------------------------------------------|

| block size (given) | B=64Byte                                        |

|                    | $B=2^b$ (b: block offset bits)                  |

| block offset bits  | b = 6                                           |

| blocks/set (given) | E=8                                             |

| cache size (given) | $C = 32KB = E \times B \times S$                |

|                    | $S = \frac{C}{B \times E} $ (S: number of sets) |

| quantity           | value for L1                                                     |  |  |  |

|--------------------|------------------------------------------------------------------|--|--|--|

| block size (given) | B=64Byte                                                         |  |  |  |

|                    | $B=2^b$ (b: block offset bits)                                   |  |  |  |

| block offset bits  | b = 6                                                            |  |  |  |

| blocks/set (given) | E=8                                                              |  |  |  |

| cache size (given) | $C = 32KB = E \times B \times S$                                 |  |  |  |

|                    | $S = \frac{C}{B \times E}$ (S: number of sets)                   |  |  |  |

| number of sets     | $S = \frac{32\overline{\text{KB}}}{64\text{Byte} \times 8} = 64$ |  |  |  |

| quantity           | value for L1                                                     |  |  |  |

|--------------------|------------------------------------------------------------------|--|--|--|

| block size (given) | $B=64 {\sf Byte}$                                                |  |  |  |

|                    | $B=2^b$ (b: block offset bits)                                   |  |  |  |

| block offset bits  | b = 6                                                            |  |  |  |

| blocks/set (given) | E = 8                                                            |  |  |  |

| cache size (given) | $C = 32KB = E \times B \times S$                                 |  |  |  |

|                    | $S = \frac{C}{B \times E} $ (S: number of sets)                  |  |  |  |

| number of sets     | $S = \frac{32\overline{\text{KB}}}{64\text{Byte} \times 8} = 64$ |  |  |  |

|                    | $S=2^s$ (s: set index bits)                                      |  |  |  |

| set index bits     | $s = \log_2(64) = 6$                                             |  |  |  |

#### T-I-O results

|                   | L1         | L2   | L3   |

|-------------------|------------|------|------|

| sets              | 64         | 1024 | 8192 |

| block offset bits | 6          | 6    | 6    |

| set index bits    | 6          | 10   | 13   |

| tag bits          | (the rest) |      |      |

```

L1 L2 L3

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

```

```

L1 L2 L3

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

```

```

L1 L2 L3

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

L1:

bits 6-11 (L1 set): 01 \ 0101 = 0 \times 15

bits 12- (L1 tag): 0x34

```

```

L1 L2 L3

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

L1:

bits 6-11 (L1 set): 01 \ 0101 = 0 \times 15

bits 12- (L1 tag): 0x34

```

```

11 12 13

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

L2:

bits 6-15 (set for L2): 01 \ 0001 \ 0101 = 0 \times 115

bits 16-: 0x3

```

```

11 12 13

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

L2:

bits 6-15 (set for L2): 01 0001 0101 = 0 \times 115

bits 16-: 0x3

```

88

```

11 12 13

block offset bits 6 6

6

set index bits 6 10 13

tag bits

(the rest)

0x34567:

0100

0101

bits 0-5 (all offsets): 100111 = 0x27

L3:

bits 6-18 (set for L3): 0 1101 0001 0101 = 0 \times D15

bits 18-: 0x0

```

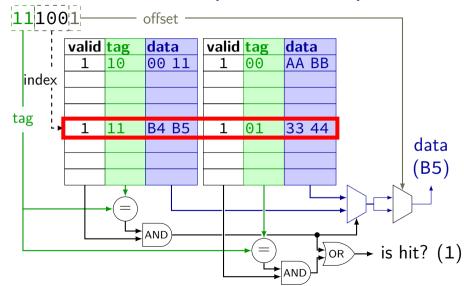

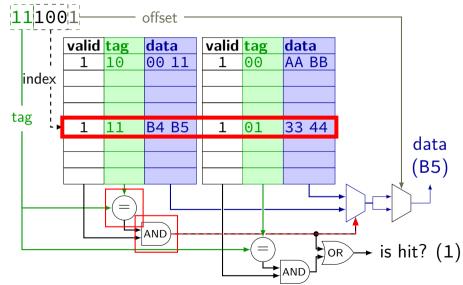

## cache operation (associative)

## cache operation (associative)

## cache operation (associative)

## backup slides — cache performance

#### cache miss types

common to categorize misses:

roughly "cause" of miss assuming cache block size fixed

compulsory (or cold) — first time accessing something adding more sets or blocks/set wouldn't change

${\it conflict} \ -- \ {\it sets aren't big/flexible enough} \\ {\it a fully-associtive (1-set) cache of the same size would have done better}$

capacity — cache was not big enough

coherence — from sync'ing cache with other caches only issue with multiple cores

#### making any cache look bad

- 1. access enough blocks, to fill the cache

- 2. access an additional block, replacing something

- 3. access last block replaced

- 4. access last block replaced

- 5. access last block replaced

...

but — typical real programs have locality

#### cache optimizations

```

(assuming typical locality + keeping cache size constant if possible...)

miss rate hit time miss penalty

increase cache size

better

worse

increase associativity

better

worse?

worse

increase block size

depends

worse

worse

add secondary cache

better

write-allocate

better

writeback

LRU replacement

better

worse?

prefetching

better

prefetching = guess what program will use, access in advance

average time = hit time + miss rate \times miss penalty

```

### cache optimizations by miss type

| (assuming other listed parameters remain constant) |              |              |              |

|----------------------------------------------------|--------------|--------------|--------------|

|                                                    | capacity     | conflict     | compulsory   |

| increase cache size                                | fewer misses | fewer misses |              |

| increase associativity                             | _            | fewer misses | _            |

| increase block size                                | more misses? | more misses? | fewer misses |

|                                                    |              |              |              |

| LRU replacement                                    | _            | fewer misses | _            |

| prefetching                                        |              |              | fewer misses |

#### average memory access time

```

\begin{aligned} \mathsf{AMAT} &= \mathsf{hit} \ \mathsf{time} + \mathsf{miss} \ \mathsf{penalty} \times \mathsf{miss} \ \mathsf{rate} \\ &\quad \mathsf{or} \ \mathsf{AMAT} = \mathsf{hit} \ \mathsf{time} \times \mathsf{hit} \ \mathsf{rate} + \mathsf{miss} \ \mathsf{time} \times \mathsf{miss} \ \mathsf{rate} \end{aligned} effective speed of memory

```

#### AMAT exercise (1)

90% cache hit rate

hit time is 2 cycles

30 cycle miss penalty

what is the average memory access time?

suppose we could increase hit rate by increasing its size, but it would increase the hit time to 3 cycles

how much do we have to increase the hit rate for this to not increase AMAT?

#### **AMAT** exercise (1)

- 90% cache hit rate

- hit time is 2 cycles

- 30 cycle miss penalty

- what is the average memory access time?

- 5 cycles

- suppose we could increase hit rate by increasing its size, but it would increase the hit time to 3 cycles

- how much do we have to increase the hit rate for this to not increase AMAT?

#### **AMAT** exercise (1)

- 90% cache hit rate

- hit time is 2 cycles

- 30 cycle miss penalty

- what is the average memory access time?

- 5 cycles

- suppose we could increase hit rate by increasing its size, but it would increase the hit time to 3 cycles

- how much do we have to increase the hit rate for this to not increase AMAT?

#### exercise: AMAT and multi-level caches

suppose we have L1 cache with

3 cycle hit time

```

90% hit rate

and an 12 cache with

10 cycle hit time

80% hit rate (for accesses that make this far)

(assume all accesses come via this L1)

and main memory has a 100 cycle access time

assume when there's an cache miss, the next level access starts

after the hit time

e.g. an access that misses in L1 and hits in L2 will take 10+3 cycles

what is the average memory access time for the L1 cache?

```

#### exercise: AMAT and multi-level caches

suppose we have L1 cache with

3 cycle hit time

```

90% hit rate

and an 12 cache with

10 cycle hit time

80% hit rate (for accesses that make this far)

(assume all accesses come via this L1)

and main memory has a 100 cycle access time

assume when there's an cache miss, the next level access starts

after the hit time

e.g. an access that misses in L1 and hits in L2 will take 10+3 cycles

what is the average memory access time for the L1 cache?

```

#### exercise: AMAT and multi-level caches

suppose we have L1 cache with

3 cycle hit time

```

90% hit rate

and an 12 cache with

10 cycle hit time

80% hit rate (for accesses that make this far)

(assume all accesses come via this L1)

and main memory has a 100 cycle access time

assume when there's an cache miss, the next level access starts

after the hit time

e.g. an access that misses in L1 and hits in L2 will take 10+3 cycles

what is the average memory access time for the L1 cache?

```

#### approximate miss analysis

very tedious to precisely count cache misses even more tedious when we take advanced cache optimizations into account

```

instead, approximations:

```

```

good or bad temporal/spatial locality

good temporal locality: value stays in cache

good spatial locality: use all parts of cache block

```

```

with nested loops: what does inner loop use?

intuition: values used in inner loop loaded into cache once

(that is, once each time the inner loop is run)

...if they can all fit in the cache

```

#### approximate miss analysis

very tedious to precisely count cache misses

even more tedious when we take advanced cache optimizations into

account

#### instead, approximations:

```

good or bad temporal/spatial locality

```

good temporal locality: value stays in cache good spatial locality: use all parts of cache block

with nested loops: what does inner loop use?

intuition: values used in inner loop loaded into cache once

(that is, once each time the inner loop is run)

...if they can all fit in the cache

#### locality exercise (1)

```

/* version 1 */

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

A[i] += B[i] * C[i * N + j]

/* version 2 */

for (int j = 0; j < N; ++j)

for (int i = 0; i < N; ++i)

A[i] += B[i] * C[i * N + j];

```

exercise: which has better temporal locality in A? in B? in C? how about spatial locality?

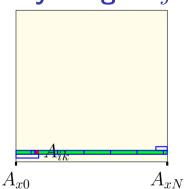

#### exercise: miss estimating (1)

```

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

A[i] += B[j] * C[i * N + j]</pre>

```

Assume: 4 array elements per block, N very large, nothing in cache at beginning.

Example: N/4 estimated misses for A accesses:

A[i] should always be hit on all but first iteration of inner-most loop. first iter: A[i] should be hit about 3/4s of the time (same block as A[i-1] that often)

Exericse: estimate # of misses for B, C

#### a note on matrix storage

```

A - N \times N matrix

represent as array

makes dynamic sizes easier:

float A_2d_array[N][N];

float *A flat = malloc(N * N);

A_flat[i * N + j] === A_2d_array[i][i]

```

#### convertion re: rows/columns

going to call the first index rows

$A_{i,j}$  is A row i, column j

rows are stored together

this is an arbitrary choice

```

array[0*5 + 0] array[0*5 + 1] array[0*5 + 2] array[0*5 + 3] array[0*5 + 4] array[1*5 + 0] array[1*5 + 1] array[1*5 + 2] array[1*5 + 3] array[1*5 + 4] array[2*5 + 0] array[2*5 + 1] array[2*5 + 2] array[2*5 + 3] array[2*5 + 4] array[3*5 + 0] array[3*5 + 1] array[3*5 + 2] array[3*5 + 3] array[3*5 + 4] array[4*5 + 0] array[4*5 + 1] array[4*5 + 2] array[4*5 + 3] array[4*5 + 4]

```

```

array[0*5 + 0]

array[0*5 + 1]

array[0*5 + 2]

array[0*5 + 3]

array[0*5 + 4]

array[1*5 + 0]

array[1*5 + 1]

array[1*5 + 2]

array[1*5 + 3]

array[1*5 + 4]

array[2*5 + 0]

array[2*5 + 1]

array[2*5 + 2]

array[2*5 + 3]

array[2*5 + 4]

array[3*5 + 0]

array[3*5 + 1]

array[3*5 + 2]

array[4*5 + 3]

array[4*5 + 4]

```

if array starts on cache block first cache block = first elements all together in one row!

```

array[0*5 + 0]

array[0*5 + 1]

array[0*5 + 2]

array[0*5 + 3]

array[0*5 + 4]

array[1*5 + 0]

array[1*5 + 1]

array[1*5 + 2]

array[1*5 + 3]

array[1*5 + 4]

array[2*5 + 0]

array[2*5 + 1]

array[2*5 + 2]

array[2*5 + 3]

array[2*5 + 4]

array[3*5 + 0]

array[3*5 + 1]

array[3*5 + 2]

array[3*5 + 3]

array[3*5 + 4]

array[4*5 + 0]

array[4*5 + 1]

array[4*5 + 2]

array[4*5 + 3]

array[4*5 + 4]

```

second cache block:

- 1 from row 0

- 3 from row 1

```

array[0*5 + 0] array[0*5 + 1] array[0*5 + 2] array[0*5 + 3] array[0*5 + 4] array[1*5 + 0] array[1*5 + 1] array[1*5 + 2] array[1*5 + 3] array[1*5 + 4] array[2*5 + 0] array[2*5 + 1] array[2*5 + 2] array[2*5 + 3] array[2*5 + 4] array[3*5 + 0] array[3*5 + 1] array[3*5 + 2] array[3*5 + 3] array[3*5 + 4] array[4*5 + 0] array[4*5 + 1] array[4*5 + 2] array[4*5 + 3] array[4*5 + 4]

```

```

array[0*5 + 0] array[0*5 + 1] array[0*5 + 2] array[0*5 + 3] array[0*5 + 4] array[1*5 + 0] array[1*5 + 1] array[1*5 + 2] array[1*5 + 3] array[1*5 + 4] array[2*5 + 0] array[2*5 + 1] array[2*5 + 2] array[2*5 + 3] array[2*5 + 4] array[3*5 + 0] array[3*5 + 1] array[3*5 + 2] array[3*5 + 3] array[3*5 + 4] array[4*5 + 0] array[4*5 + 1] array[4*5 + 2] array[4*5 + 3] array[4*5 + 4]

```

generally: cache blocks contain data from 1 or 2 rows

$\rightarrow$  better performance from reusing rows

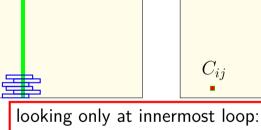

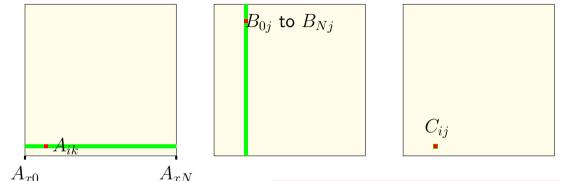

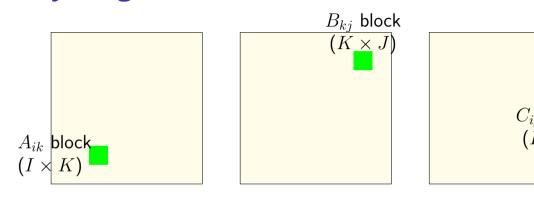

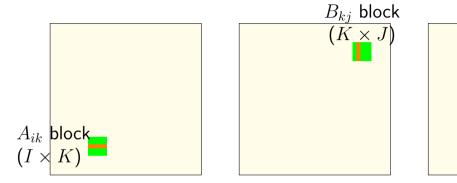

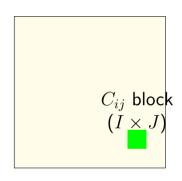

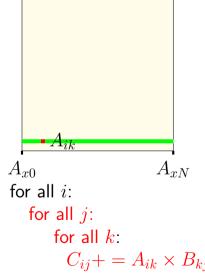

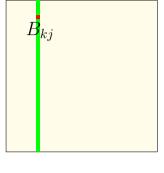

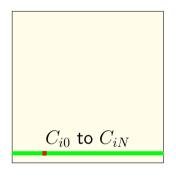

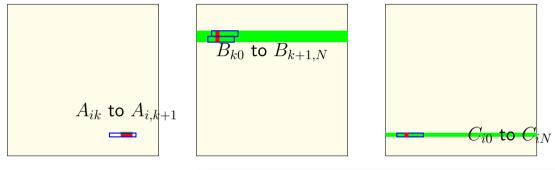

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

```

/* version 1: inner loop is k, middle is j */

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

for (int k = 0; k < N; ++k)

C[i * N + j] += A[i * N + k] * B[k * N + j];</pre>

```

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

```

/* version 1: inner loop is k, middle is j*/

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

for (int k = 0; k < N; ++k)

C[i*N+i] += A[i * N + k] * B[k * N + i]:

/* version 2: outer loop is k, middle is i */

for (int k = 0; k < N; ++k)

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

C[i*N+i] += A[i * N + k] * B[k * N + i];

```

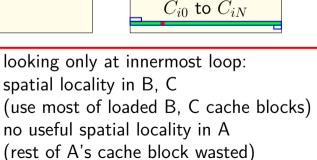

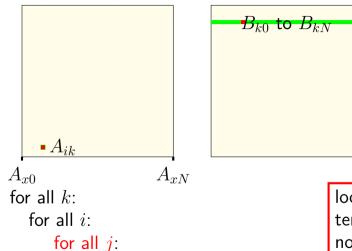

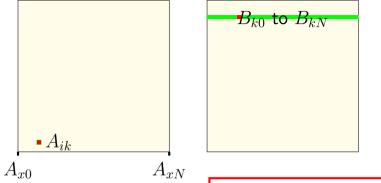

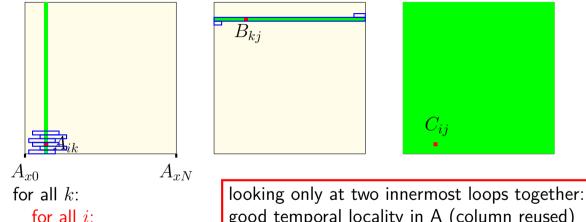

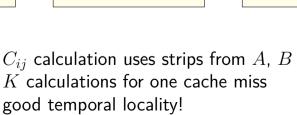

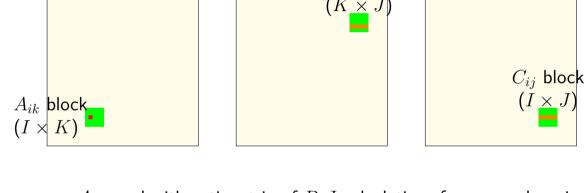

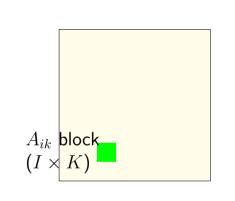

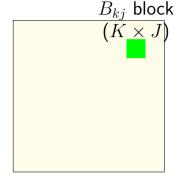

#### loop orders and locality

loop body:  $C_{ij}+=A_{ik}B_{kj}$

kij order:  $C_{ij}$ ,  $B_{kj}$  have spatial locality

kij order:  $A_{ik}$  has temporal locality

... better than ...

ijk order:  $A_{ik}$  has spatial locality

ijk order:  $C_{ij}$  has temporal locality

#### loop orders and locality

loop body:  $C_{ij} += A_{ik}B_{kj}$

kij order:  $C_{ij}$ ,  $B_{kj}$  have spatial locality

kij order:  $A_{ik}$  has temporal locality

... better than ...

ijk order:  $A_{ik}$  has spatial locality

ijk order:  $C_{ij}$  has temporal locality

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

```

/* version 1: inner loop is k, middle is j*/

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

for (int k = 0; k < N; ++k)

C[i*N+i] += A[i * N + k] * B[k * N + i]:

/* version 2: outer loop is k, middle is i */

for (int k = 0; k < N; ++k)

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

C[i*N+i] += A[i * N + k] * B[k * N + i];

```