|  | CS | 3330 | Fall | 2017 | Exam | 2 |

|--|----|------|------|------|------|---|

|--|----|------|------|------|------|---|

Variant C page 1 of 8

| $\Sigma$ mail | 11). |  |  |

|---------------|------|--|--|

| JULICALL      | 117. |  |  |

# CS 3330 Exam 2 Fall 2017

| Name: | Computing ID: |  |

|-------|---------------|--|

|       |               |  |

Letters go in the boxes unless otherwise specified (e.g., for C 8 write "C" not "8").

Write Letters clearly: if we are unsure of what you wrote you will get a zero on that problem. Bubble and Pledge the exam or you will lose points.

Assume unless otherwise specified:

- little-endian 64-bit architecture

- %rsp points to the most recently pushed value, not to the next unused stack address.

- questions are single-selection unless identified as select-all

Variable Weight: point values per question are marked in square brackets.

**Mark clarifications**: If you need to clarify an answer, do so, and also add a  $\star$  to the top right corner of your answer box.

## Information for questions 1–2

For these questions consider a pipelined processor where the execute stage is split into three stages in order to support instructions with complex ALU operations. The resulting stages in this processor are:

- Fetch

- Decode

- Execute 1

- Execute 2

- Execute 3

- Memory

- Writeback

The new split execute stages require the values for the ALU operation near the start of the execute 1 stage and only produces results near the end of end of the execute 3 stage, regardless of the complexity of the ALU operation. The other stages work as in the five-stage processor described in lecture.

Question 1 [2 pt]: (see above) To execute the following assembly snippet on this processor with **minimum stalling**:

warding register values. How many cycles of stalling are required? Write your

```

addq %rax, %rbx

mrmovq 4(%rax), %r13

subq %rbx, %r13

the processor needs to stall for some number of cycles in addition to for-

```

Question 2 [2 pt]: (see above) To execute the following assembly snippet on this processor without stalling:

```

addq %rax, %rbx

xorq %rcx, %rdx

rrmovq %r8, %r9

rmmovq %r11, 4(%r12)

subq %rbx, %r13

```

answer as a base-10 number.

the processor needs to forward the value of %rbx from addq to subq. Which forwarding path can the processor use to do this?

**A** the end of addg's execute 2 stage to the end of subg's decode stage

**B** the end of addq's memory stage to the end of subq's execute 1 stage

C the end of addq's execute 3 stage to the end of subq's execute 1 stage

**D** the end of addq's execute 3 stage to the end of subq's decode stage

**E** the end of addq's memory stage to the end of the subq's decode stage

**F** the end of addq's writeback stage to the end of subq's execute 1 stage

**G** none of the above

# Information for questions 3–4

Consider a 4 KB (2<sup>12</sup> byte) 2-way set-associative write-back, write-allocate cache with 256-byte (2<sup>8</sup> byte) cache blocks, an LRU replacement policy.

Question 3 [2 pt]: (see above) How many sets does this cache have? Write your answer as a base-10 number.

Answer:

Question 4 [2 pt]: (see above) When accessing this cache, which of the following addresses will map to the same cache set as 0x12345? Place a ✓ in each box that will map to the same set. Leave other boxes blank.

Question 5 [2 pt]: Suppose a program reads every byte of a 2MB array starting with the lowest address and proceeding in order to the highest address, then repeats this process 1000 times. On which type of data cache will the program experience the **fewest** cache misses on average? (Assume memory accesses other than those to the array are neglible and that 1MB represents 2<sup>20</sup> bytes.)

$\boldsymbol{\mathsf{A}}$  a 1MB 4-way set associative cache with a random replacement policy and 64B cache blocks

${\bf B}~$  a 1.75MB fully associative cache with an FIFO (first-in, first-out) replacement policy and 64B cache blocks

**C** a 0.5MB direct-mapped cache with 32B cache blocks

${f D}$  a 1MB 8-way set associative cache with an LRU (least recently used) replacement policy and 64B cache blocks

## Information for questions 6–7

Suppose a program reads a single byte at each of the following addresses, in the following order:

- 0x06

- 0x07

- 0x16

- 0x00

- 0x17

- 0x03

- 0x07

Question 6 [2 pt]: (see above) Consider a 16 byte direct-mapped cache with a 4 byte block size. Assume the cache is initially empty. How many of these accesses will be hits? Write your answer as a base-10 number.

Answer:

Question 7 [2 pt]: (see above) Consider a 8 byte 2-way set associative cache with a 2 byte block size and an LRU replacement policy. Assume the cache is initially empty. How many of these accesses will be hits? Write your answer as a base-10 number.

Answer:

Question 8 [2 pt]: Suppose we have two processor designs, with different numbers of pipeline stages. On the first processor 10% of the instructions in a benchmark program stall for exactly 1 cycle and 5% stall for exactly 2 cycles. The second processor has more pipeline stages, so 40% of the instructions in the benchmark program stall for an additional cycle (compared to the first processor), but it has half the cycle time.

If the benchmark program took 10 seconds to run on the first processor, then how long did take on the second processor?

A more than 10 seconds

**B** more than 9 and less than or equal to 10 seconds

**C** more than 8 and less than or equal to 9 seconds

**D** more than 7 and less than or equal to 8 seconds

**E** more than 6 and less than or equal to 7 seconds

**F** 6 or less seconds

#### Information for questions 9–10

Consider the following C code:

```

unsigned char array[1024 * 1024];

/* ... */

int sum = 0;

for (int x = 0; x < 10; ++x) {

for (int i = 0; i < 16; ++i) {

sum += array[i * 128] * array[i * 128 + i];

}

}</pre>

```

Assume that:

- only array is kept in memory (all other variables are stored in registers);

- array is stored at an address that is a multiple of  $4096 (2^{12})$ ;

- that the compiler does not remove or reorder any accesses to the array;

- unsigned chars are 1 byte;

- the cache is empty upon entry to the outer for loop above

Note that 1024/8 = 128.

Question 9 [2 pt]: (see above) If the above nested for loops are run on a system with a 1KB (1024 byte) direct-mapped cache with 1-byte cache blocks, how many data cache misses will it experience?

**A** 16

**B** 24

**C** 31

**D** 160

**E** 175

$\mathbf{F}$  240

**G** 320

**H** none of the above

Answer:

Question 10 [2 pt]: (see above) If the above nested for loops are run on a system with an 4KB (1024 byte) 16-way set associative cache with 64-byte cache blocks and an LRU replacement policy, how many data cache misses will it experience?

**A** 31

**B** 240

**C** 320

**D** 16

**E** 175

**F** 160

**G** 24

**H** none of the above

Answer:

## Information for questions 11–13

Suppose we are running the following assembly snippet in the five-stage pipelined processor with forwarding and branch prediction discussed in the lecture and in the textbook:

```

xorq %rax, %rax

jne after_add

addq %rax, %rsp

after_add:

subq %rax, %rsp

andq %rsp, %rax

rmmovq %rsp, 0(%rax)

popq %rax

```

Recall that this processor predicts all branches as taken and computes the actual result of branches by the end of the execute stage of the conditional jump instruction and fetches the corrected next instruction during the conditional jump's memory stage. **The conditional jump is not taken.**

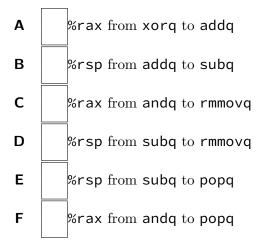

Question 11 [3 pt]: (see above) In order to execute this assembly snippet correctly, which of the following forwarding operations will the processor need to perform? Place a ✓ next to each correct answer. Leave all other boxes blank.

Question 12 [2 pt]: (see above) When the andq instruction is in the fetch stage, what pipeline stages will be running a pipeline "bubble" (nop inserted to handle a pipeline hazard)? Place a ✓ in each box that will have a pipeline bubble. Leave all other boxes blank.

Question 13 [2 pt]: (see above) When the subq instruction is in the writeback stage, the rmmovq instruction is in what stage?

- **A** fetch

- **B** decode

- **C** execute

- **D** memory

- **E** writeback

- **F** none of the above; it is not in the pipeline

#### Information for questions 14–16

Consider the following two pieces C code:

```

/* Version A */

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

A[i * N + j] += B[i + j * 10] * C[j];

```

and:

```

/* Version B */

for (int j = 0; j < N; ++j)

for (int i = 0; i < N; ++i)

A[i * N + j] += B[i + j * 10] * C[j];</pre>

```

Assume that N is a large integer constant and that A, B, and C are large arrays of 4-byte ints. Assume that all values except the accesses to A, B and C are stored in registers.

Question 14 [1 pt]: (see above) Which version has better spatial locality in its accesses to B?

- **A** version A

- **B** version B

- **C** they are about the same

Answer:

Question 15 [1 pt]: (see above) Which version has better temporal locality in its accesses to C?

- A version A

- **B** version B

- **C** they are about the same

Answer:

Question 16 [1 pt]: (see above) Which version has better temporal locality in its accesses to A?

- **A** version A

- **B** version B

- **C** they are about the same

Answer:

Question 17 [2 pt]: Which of the following statements about loop unrolling are true? Put a  $\checkmark$  next to each box that is true. Leave the other boxes blank.

- A loop unrolling is likely to increase the size of an executable

- B loop unrolling improves the temporal locality of instruction accesses

- **C** as long as a loop has enough iterations, loop unrolling will decrease the number of

instructions executed

**D** loop unrolling is not practical if the loop body manipulates two pointers that may alias

#### Information for questions 18–20

Suppose the components of our Y86 processor take the following amounts of time to process their inputs and either produce a corresponding output or (in the case of register file or data memory writes) be ready to store a value if a rising clock edge happens.

| component                        | time required   |

|----------------------------------|-----------------|

| instruction memory               | 250 picoseconds |

| register file reading            | 200 picoseconds |

| register file writing            | 200 picoseconds |

| $\operatorname{ALU}$             | 350 picoseconds |

| data memory (reading or writing) | 300 picoseconds |

| PC increment                     | 30 picoseconds  |

In addition, assume the **register delay for any pipeline registers** is **25 picoseconds**. Assume that other components of the processor take a negligible amount of time.

Question 18 [2 pt]: (see above) If we use these components to build a five-stage pipelined Y86 processor, like the one described in lecture and our textbook, what is the minimum cycle time this processor can have? Write your answer as a base-10 number of picoseconds.

| Answer: |  |

|---------|--|

|         |  |

|         |  |

|         |  |

Question 19 [2 pt]: (see above) If we use these components to build a single-cycle Y86 processor, what is the minimum cycle time this processor can have? Do not include any register delay for the PC register. Write your answer as a base-10 number of picoseconds.

| Answer: |  |

|---------|--|

|         |  |

|         |  |

Question 20 [2 pt]: (see above) Suppose we split the ALU into two halves, each of which takes 175 picoseconds (half of the original 350 picoseconds). Using this, we split the execute stage into two stages to modify our five-stage pipelined into a six-stage pipelined Y86 processor. By how much will this reduce the cycle time of our Y86 processor? Write your answer as a base-10 number of picoseconds.

| Answer: |  |

|---------|--|

|         |  |

|         |  |

# Pledge:

On my honor as a student, I have neither given nor received aid on this exam.

Your signature here