cache performance 2

#### last time

AMAT and multi-level caches

cache tradeoffs:

which effects hit time/hit rate/miss penalty

compulsory (or cold)/conflict/capacity misses

counting misses based on C code

# arrays and cache misses (1)

```

int array[1024]; // 4KB array

int even_sum = 0, odd_sum = 0;

for (int i = 0; i < 1024; i += 2) {

even_sum += array[i + 0];

odd_sum += array[i + 1];

}</pre>

```

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many *data cache misses* on a 2KB direct-mapped cache with 16B cache blocks?

## arrays and cache misses (2)

int array[1024]; // 4KB array

int even\_sum = 0, odd\_sum = 0;

for (int i = 0; i < 1024; i += 2)

even\_sum += array[i + 0];

for (int i = 0; i < 1024; i += 2)

odd\_sum += array[i + 1];</pre>

Assume everything but array is kept in registers (and the compiler does not do anything funny).

How many *data cache misses* on a 2KB direct-mapped cache with 16B cache blocks? Would a set-associtiave cache be better?

#### set-associative not better?

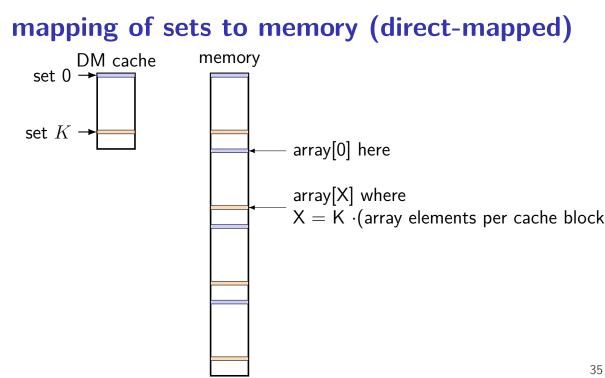

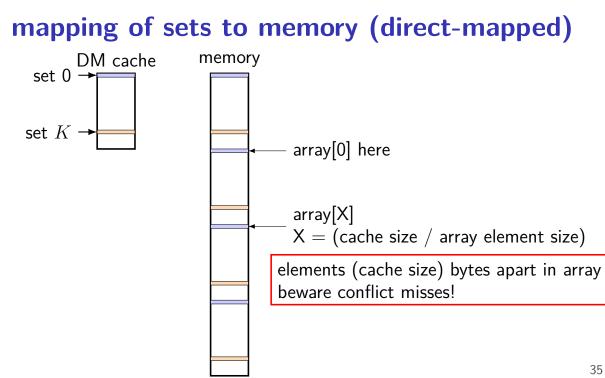

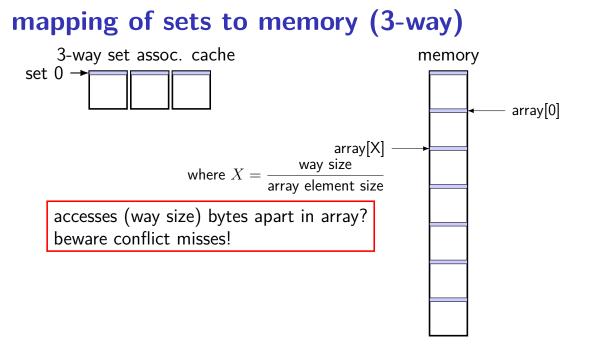

2KB direct-mapped cache, 4B array elements: array[0 to 3] and array[512 to 515] map to same set 2KB apart — mapping "wraps around" four misses for this set access to array[0]+array[2], then array[512]+array[514], then array[1]+array[3], then array[513]+array[515] same for each of other 127 sets

2KB, 2-way set associative cache: array[0 to 3] and array[256 to 259] and array[512 to 515] and array[756 to 759] map to same set 1KB apart — shorter time until mapping wraps around eight misses + same for other 63 sets

## approximate miss analysis

very tedious to precisely count cache misses even more tedious when we take advanced cache optimizations into account

instead, approximations:

good or bad temporal/spatial locality good temporal locality: value stays in cache good spatial locality: use all parts of cache block

with nested loops: what does inner loop use? intuition: values used in inner loop loaded into cache once (that is, once each time the inner loop is run) ...if they can all fit in the cache

## approximate miss analysis

#### very tedious to precisely count cache misses even more tedious when we take advanced cache optimizations into account

#### instead, approximations:

#### good or bad temporal/spatial locality

good temporal locality: value stays in cache good spatial locality: use all parts of cache block

with nested loops: what does inner loop use? intuition: values used in inner loop loaded into cache once (that is, once each time the inner loop is run) ...if they can all fit in the cache

# locality exercise (1)

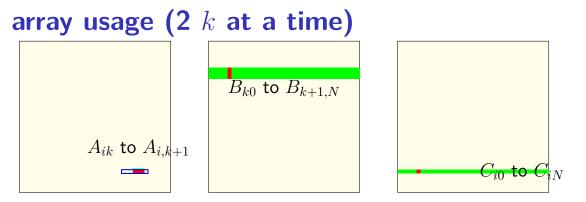

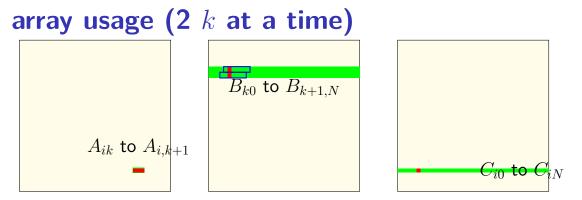

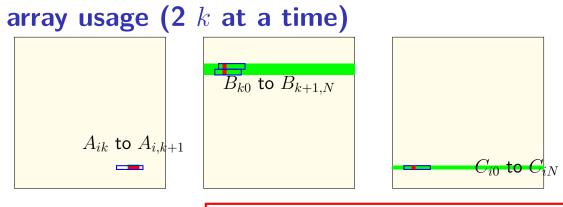

exercise: which has better temporal locality in A? in B? in C? how about spatial locality?

## exercise: miss estimating (1)

Assume: 4 array elements per block, N very large, nothing in cache at beginning.

Example: N/4 estimated misses for A accesses: A[i] should always be hit on all but first iteration of inner-most loop. first iter: A[i] should be hit about 3/4s of the time (same block as A[i-1] that often)

Exericse: estimate # of misses for B, C

### a note on matrix storage

$A - N \times N \text{ matrix}$

represent as array

makes dynamic sizes easier:

```

float A_2d_array[N][N];

float *A_flat = malloc(N * N);

```

A\_flat[i \* N + j] === A\_2d\_array[i][j]

## convertion re: rows/columns

going to call the first index rows

$A_{i,j}$  is A row i, column j

rows are stored together

this is an arbitrary choice

| array[0*5 + 0] | array[0*5 + 1] | array[0*5 + 2] | array[0*5 + 3] | array[0*5 + 4] |

|----------------|----------------|----------------|----------------|----------------|

| array[1*5 + 0] | array[1*5 + 1] | array[1*5 + 2] | array[1*5 + 3] | array[1*5 + 4] |

| array[2*5 + 0] | array[2*5 + 1] | array[2*5 + 2] | array[2*5 + 3] | array[2*5 + 4] |

| array[3*5 + 0] | array[3*5 + 1] | array[3*5 + 2] | array[3*5 + 3] | array[3*5 + 4] |

| array[4*5 + 0] | array[4*5 + 1] | array[4*5 + 2] | array[4*5 + 3] | array[4*5 + 4] |

| array[0*5 + 0] | array[0*5 + 1] | array[0*5 + 2] | array[0*5 + 3] | array[0*5 + 4] |

|----------------|----------------|----------------|----------------|----------------|

| array[1*5 + 0] | array[1*5 + 1] | array[1*5 + 2] | array[1*5 + 3] | array[1*5 + 4] |

| array[2*5 + 0] | array[2*5 + 1] | array[2*5 + 2] | array[2*5 + 3] | array[2*5 + 4] |

| array[3*5 + 0] | array[3*5 + 1] | array[3*5 + 2] | array[3*5 + 3] | array[3*5 + 4] |

| array[4*5 + 0] | array[4*5 + 1] | array[4*5 + 2] | array[4*5 + 3] | array[4*5 + 4] |

if array starts on cache block first cache block = first elements all together in one row!

| array[0*5 + 0] | array[0*5 + 1] | array[0*5 + 2] | array[0*5 + 3] | array[0*5 + 4] |

|----------------|----------------|----------------|----------------|----------------|

| array[1*5+0]   | array[1*5 + 1] | array[1*5 + 2] | array[1*5 + 3] | array[1*5 + 4] |

| array[2*5 + 0] | array[2*5 + 1] | array[2*5 + 2] | array[2*5 + 3] | array[2*5 + 4] |

| array[3*5 + 0] | array[3*5 + 1] | array[3*5 + 2] | array[3*5 + 3] | array[3*5 + 4] |

| array[4*5 + 0] | array[4*5 + 1] | array[4*5 + 2] | array[4*5 + 3] | array[4*5 + 4] |

second cache block: 1 from row 0 3 from row 1

| array[0*5 + 0] | array[0*5 + 1] | array[0*5 + 2] | array[0*5 + 3] | array[0*5 + 4] |

|----------------|----------------|----------------|----------------|----------------|

| array[1*5 + 0] | array[1*5 + 1] | array[1*5 + 2] | array[1*5 + 3] | array[1*5 + 4] |

| array[2*5 + 0] | array[2*5 + 1] | array[2*5 + 2] | array[2*5 + 3] | array[2*5 + 4] |

| array[3*5 + 0] | array[3*5 + 1] | array[3*5 + 2] | array[3*5 + 3] | array[3*5 + 4] |

| array[4*5 + 0] | array[4*5 + 1] | array[4*5 + 2] | array[4*5 + 3] | array[4*5 + 4] |

| array[0*5 + 0] | array[0*5 + 1] | array[0*5 + 2] | array[0*5 + 3] | array[0*5 + 4] |

|----------------|----------------|----------------|----------------|----------------|

| array[1*5 + 0] | array[1*5 + 1] | array[1*5 + 2] | array[1*5 + 3] | array[1*5 + 4] |

| array[2*5 + 0] | array[2*5 + 1] | array[2*5 + 2] | array[2*5 + 3] | array[2*5 + 4] |

| array[3*5 + 0] | array[3*5 + 1] | array[3*5 + 2] | array[3*5 + 3] | array[3*5 + 4] |

| array[4*5 + 0] | array[4*5 + 1] | array[4*5 + 2] | array[4*5 + 3] | array[4*5 + 4] |

generally: cache blocks contain data from 1 or 2 rows  $\rightarrow$  better performance from reusing rows

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

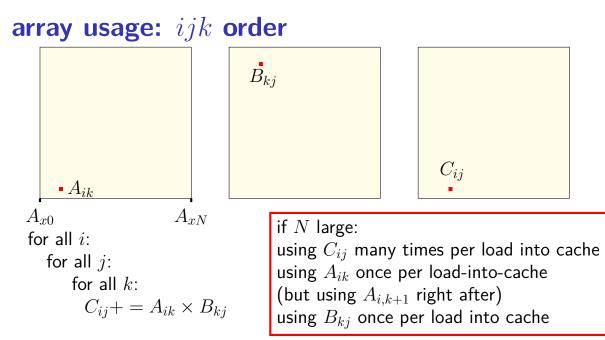

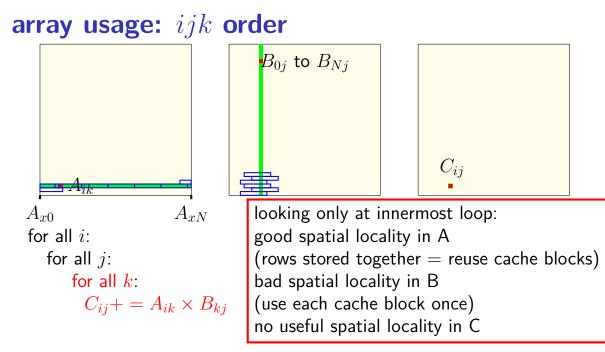

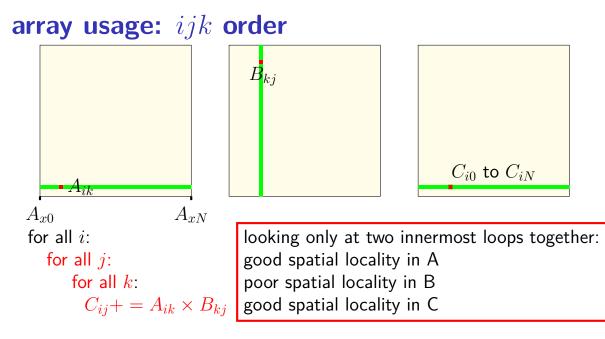

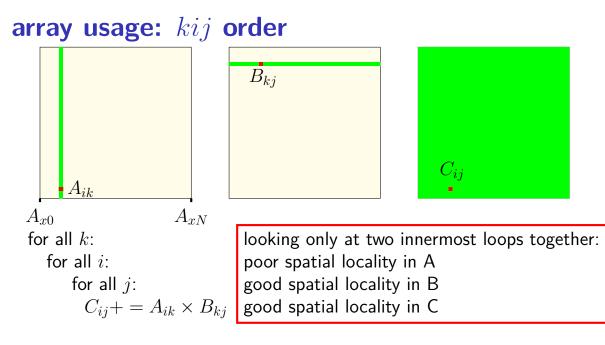

#### which is better?

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

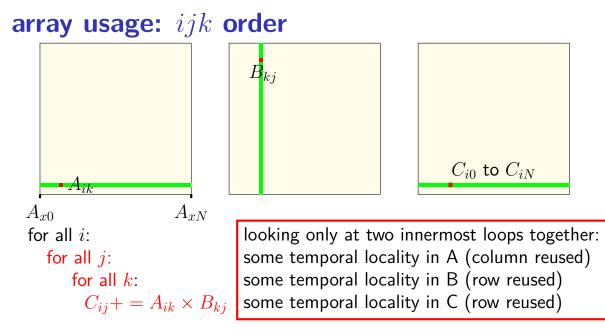

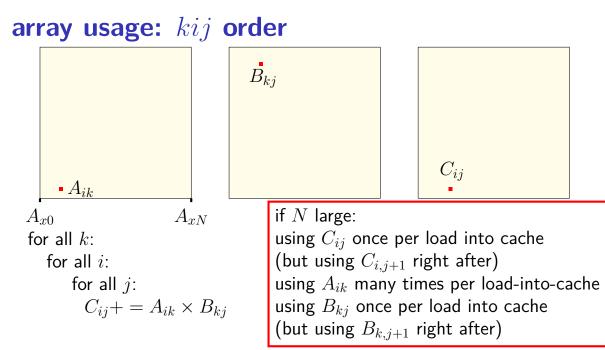

exercise: Which version has better spatial/temporal locality for... ...accesses to C? ...accesses to A? ...accesses to B?

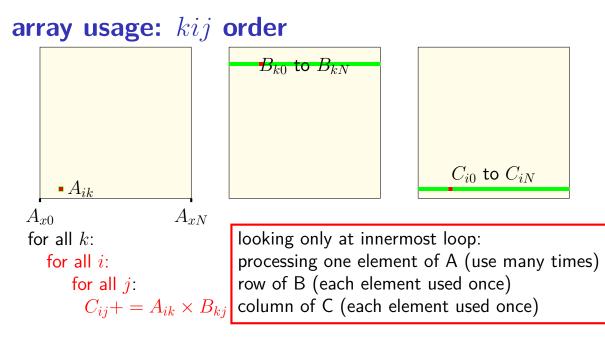

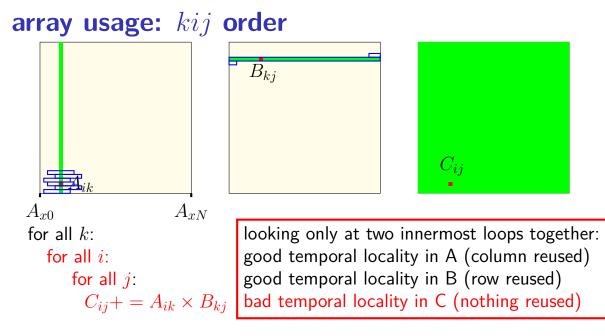

## loop orders and locality

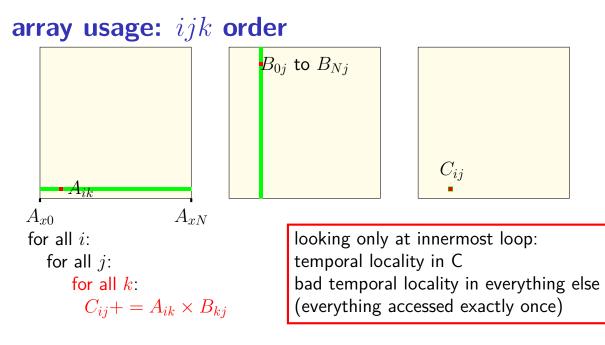

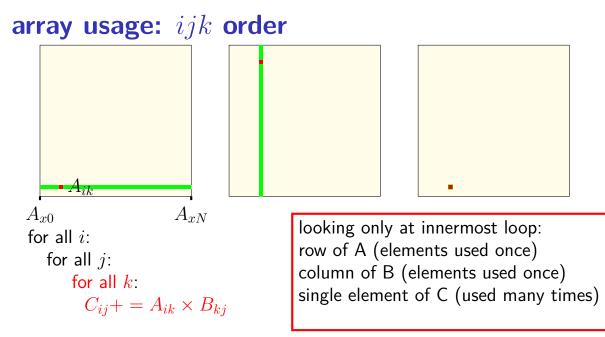

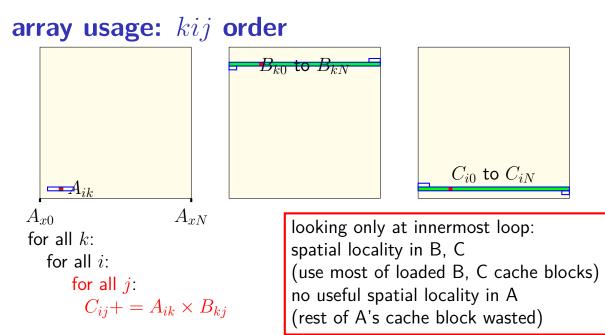

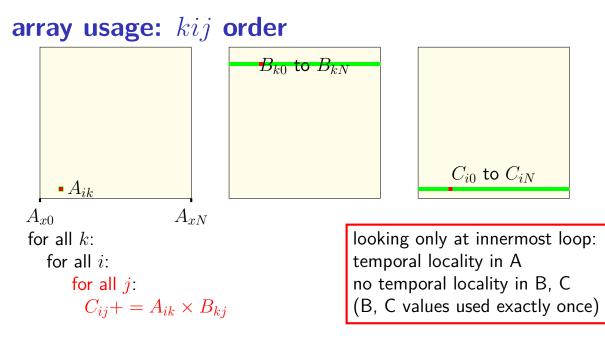

loop body:  $C_{ij} + = A_{ik}B_{kj}$

kij order:  $C_{ij}$ ,  $B_{kj}$  have spatial locality

kij order:  $A_{ik}$  has temporal locality

... better than ...

ijk order:  $A_{ik}$  has spatial locality

ijk order:  $C_{ij}$  has temporal locality

## loop orders and locality

loop body:  $C_{ij} + = A_{ik}B_{kj}$

kij order:  $C_{ij}$ ,  $B_{kj}$  have spatial locality

kij order:  $A_{ik}$  has temporal locality

... better than ...

ijk order:  $A_{ik}$  has spatial locality

ijk order:  $C_{ij}$  has temporal locality

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

### counting misses: version 1

if N really large assumption: can't get close to storing N values in cache at once

for A: about  $N \div \text{block}$  size misses per k-loop total misses:  $N^3 \div \text{block}$  size

- for B: about N misses per k-loop total misses:  $N^3$

- for C: about  $1 \div \text{block}$  size miss per k-loop total misses:  $N^2 \div \text{block}$  size

### counting misses: version 2

- for A: about 1 misses per j-loop total misses:  $N^2$

- for B: about  $N \div \text{block}$  size miss per j-loop total misses:  $N^3 \div \text{block}$  size

- for C: about  $N \div \text{block}$  size miss per j-loop total misses:  $N^3 \div \text{block}$  size

### matrix multiply

$$C_{ij} = \sum_{k=1}^{n} A_{ik} \times B_{kj}$$

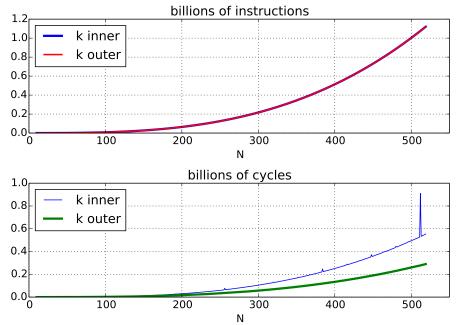

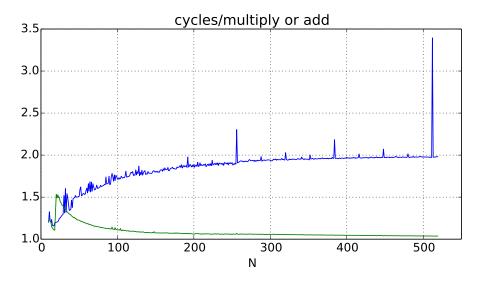

# performance (with A=B)

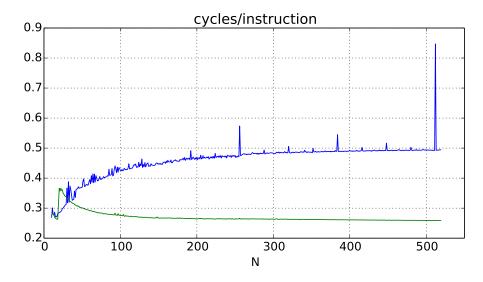

### alternate view 1: cycles/instruction

### alternate view 2: cycles/operation

### backup slides

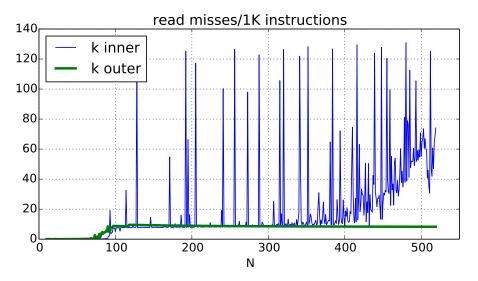

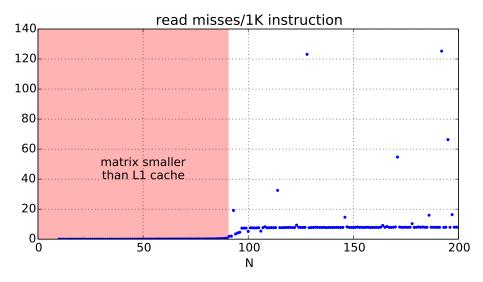

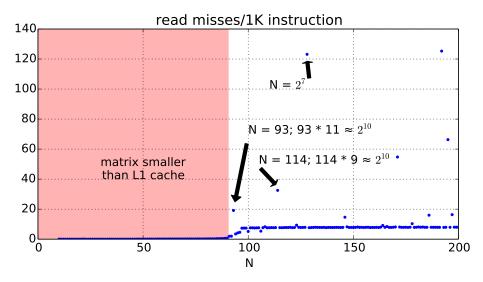

# L1 misses (with A=B)

# L1 miss detail (1)

# L1 miss detail (2)

#### addresses

B[k\*114+j] is at 10 0000 0000 0100 B[k\*114+j+1] is at 10 0000 0000 1000 B[(k+1)\*114+j] is at 10 0011 1001 0100 B[(k+2)\*114+j] is at 10 0101 0101 1100 ... B[(k+9)\*114+j] is at 11 0000 0000 1100

#### addresses

B[k\*114+j]

is at 10 0000 0000 0100

B[k\*114+j+1]

is at 10 0000 0000 1000

B[(k+1)\*114+j]

is at 10 0011 1001 0100

B[(k+2)\*114+j]

is at 10 0101 0101 1100

...

B[(k+9)\*114+j]

test system L1 cache: 6 index bits, 6 block offset bits

### conflict misses

powers of two — lower order bits unchanged

B[k\*93+j] and B[(k+11)\*93+j]:

1023 elements apart (4092 bytes; 63.9 cache blocks)

64 sets in L1 cache: usually maps to same set

B[k\*93+(j+1)] will not be cached (next *i* loop)

even if in same block as B[k\*93+j]

how to fix? improve spatial locality (maybe even if it requires copying)

#### quiz exercise solution

one cache block one cache block one cache block one cache block (set index 1) (set index 0) (set index 1) (set index 0) ... array[0] array[1] array[2] array[3] array[4] array[5] array[6] array[7] array.

| memory access        | set 0 afterwards     | set 1 afterwards     |  |

|----------------------|----------------------|----------------------|--|

| _                    | (empty)              | (empty)              |  |

| read array[0] (miss) | {array[0],array[1]}  | (empty)              |  |

| read array[3] (miss) | {array[0],array[1]}  | {array[2], array[3]} |  |

| read array[6] (miss) | {array[0],array[1]}  | {array[6],array[7]}  |  |

| read array[1] (hit)  | {array[0], array[1]} | {array[6], array[7]} |  |

| read array[4] (miss) | {array[4],array[5]}  | {array[6], array[7]} |  |

| read array[7] (hit)  | {array[4],array[5]}  | {array[6], array[7]} |  |

| read array[2] (miss) | {array[4],array[5]}  | {array[2], array[3]} |  |

| read array[5] (hit)  | {array[4],array[5]}  | {array[6],array[7]}  |  |

| read array[8] (miss) | {array[8],array[9]}  | {array[6],array[7]}  |  |

#### quiz exercise solution

one cache block one cache block one cache block one cache block (set index 1) (set index 0) (set index 1) (set index 0) ... array[0] array[1] array[2] array[3] array[4] array[5] array[6] array[7] array.

| memory access        | set 0 afterwards     | set 1 afterwards                |

|----------------------|----------------------|---------------------------------|

| —                    | (empty)              | (empty)                         |

| read array[0] (miss) | {array[0], array[1]} | (empty)                         |

| read array[3] (miss) | {array[0], array[1]} | {array[2],array[3]}             |

|                      | {array[0],array[1]}  |                                 |

| read array[1] (hit)  | {array[0], array[1]} | <pre>{array[6], array[7]}</pre> |

| read array[4] (miss) | {array[4], array[5]} | {array[6],array[7]}             |

| read array[7] (hit)  | {array[4],array[5]}  | {array[6],array[7]}             |

|                      | {array[4],array[5]}  |                                 |

| read array[5] (hit)  | {array[4],array[5]}  | {array[6],array[7]}             |

| read array[8] (miss) | {array[8],array[9]}  | {array[6],array[7]}             |

### quiz exercise solution

|  |          | he block<br>dex 1) |          |          |          | he block<br>dex 1) | one cacl<br>(set in |          |      |  |

|--|----------|--------------------|----------|----------|----------|--------------------|---------------------|----------|------|--|

|  | array[0] | array[1]           | array[2] | array[3] | array[4] | array[5]           | array[6]            | array[7] | arra |  |

| memory access        | set 0 afterwards                | set 1 afterwards                |

|----------------------|---------------------------------|---------------------------------|

| —                    | (empty)                         | (empty)                         |

| read array[0] (miss) | {array[0],array[1]}             | (empty)                         |

| read array[3] (miss) | <pre>{array[0], array[1]}</pre> | <pre>{array[2], array[3]}</pre> |

| read array[6] (miss) | {array[0], array[1]}            | <pre>{array[6], array[7]}</pre> |

| read array[1] (hit)  | {array[0],array[1]}             | <pre>{array[6], array[7]}</pre> |

|                      | {array[4],array[5]}             | {array[6],array[7]}             |

| read array[7] (hit)  | <pre>{array[4], array[5]}</pre> | <pre>{array[6], array[7]}</pre> |

| read array[2] (miss) | <pre>{array[4], array[5]}</pre> | <pre>{array[2], array[3]}</pre> |

| read array[5] (hit)  | {array[4],array[5]}             | <pre>{array[6], array[7]}</pre> |

|                      | {array[8],array[9]}             | {array[6],array[7]}             |

#### not the quiz problem

...

one cache block one cache block one cache bloc one cache block

array[0]array[1]array[2]array[3]array[4]array[5]array[6]array[7]arra

if 1-set 2-way cache instead of 2-set 1-way cache:

| memory access        | single set with 2-ways, LRU first                     |  |  |

|----------------------|-------------------------------------------------------|--|--|

| —                    | ,                                                     |  |  |

| read array[0] (miss) | , {array[0], array[1]}                                |  |  |

| read array[3] (miss) | <pre>{array[0], array[1]}, {array[2], array[3]}</pre> |  |  |

| read array[6] (miss) | <pre>{array[2], array[3]}, {array[6], array[7]}</pre> |  |  |

| read array[1] (miss) | {array[6], array[7]}, {array[0], array[1]}            |  |  |

| read array[4] (miss) | <pre>{array[0], array[1]}, {array[3], array[4]}</pre> |  |  |

| read array[7] (miss) | <pre>{array[3], array[4]}, {array[6], array[7]}</pre> |  |  |

| read array[2] (miss) | {array[6], array[7]}, {array[2], array[3]}            |  |  |

| read array[5] (miss) | {array[2], array[3]}, {array[5], array[6]}            |  |  |

| read array[8] (miss) | {array[5], array[6]}, {array[8], array[9]}            |  |  |

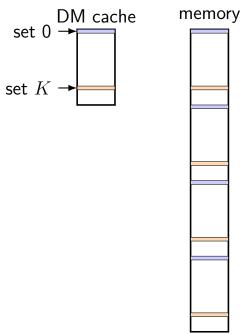

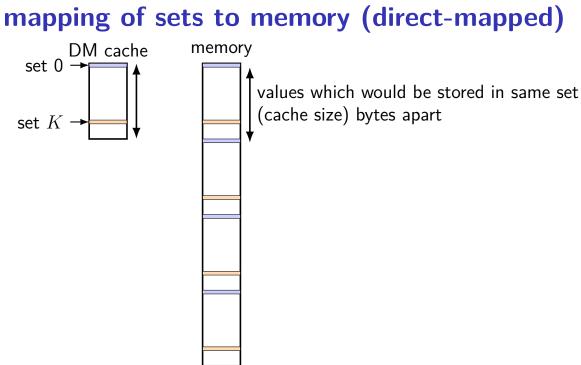

## mapping of sets to memory (direct-mapped)

### mapping of sets to memory (3-way)

### mapping of sets to memory (3-way)

### mapping of sets to memory (3-way)

# C and cache misses (4)

```

typedef struct {

int a_value, b_value;

int other_values[6];

} item;

item items[5];

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 5; ++i)

a_sum += items[i].a_value;

for (int i = 0; i < 5; ++i)

b_sum += items[i].b_value;</pre>

```

Assume everything but items is kept in registers (and the compiler does not do anything funny).

# C and cache misses (4, rewrite)

Assume everything but array is kept in registers (and the compiler does not do anything funny) and array starts at beginning of cache block.

How many *data cache misses* on a 2-way set associative 128B cache with 16B cache blocks and LRU replacement?

## C and cache misses (4, solution pt 1)

ints 4 byte  $\rightarrow$  array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

accessing 0, 8, 16, 24, 32, 1, 9, 17, 25, 33

### C and cache misses (4, solution pt 1)

ints 4 byte  $\rightarrow$  array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

accessing 0, 8, 16, 24, 32, 1, 9, 17, 25, 33

0 (set 0), 8 (set 2), 16 (set 0), 24 (set 2), 32 (set 0)

1 (set 0), 9 (set 2), 17 (set 0), 25 (set 2), 33 (set 0)

### C and cache misses (4, solution pt 2)

set 0 after (LRU first) access

\_. \_\_

result

array[1] array[17] array[32]

array[0] —, array[0 to 3]miss array[16] array[0 to 3], array[16 to 19] miss array[32] array[16 to 19], array[32 to 35] miss array[32 to 35], array[0 to 3]miss array[0 to 3], array[16 to 19] miss array[16 to 19], array[32 to 35] miss

6 misses for set 0

### C and cache misses (4, solution pt 3)

set 2 after (LRU first) access

result

array[25]

\_, \_\_\_ array[8] —, array[8 to 11]miss array[24] array[8 to 11], array[24 to 27] miss array[9] array[8 to 11], array[24 to 27] hit array[16 to 19], array[32 to 35] hit

2 misses for set 1

# C and cache misses (3)

```

typedef struct {

int a_value, b_value;

int other_values[10];

} item;

item items[5];

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 5; ++i)

a_sum += items[i].a_value;

for (int i = 0; i < 5; ++i)

b_sum += items[i].b_value;</pre>

```

observation: 12 ints in struct: only first two used

equivalent to accessing array[0], array[12], array[24], etc.

...then accessing array[1], array[13], array[25], etc.

## C and cache misses (3, rewritten?)

Assume everything but array is kept in registers (and the compiler does not do anything funny) and array at beginning of cache block.

How many *data cache misses* on a 128B two-way set associative cache with 16B cache blocks and LRU replacement?

observation 1: first loop has 5 misses - first accesses to blocks

observation 2: array[0] and array[1], array[12] and array[13], etc. in same cache block

## C and cache misses (3, solution)

ints 4 byte  $\rightarrow$  array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

accessing array indices 0, 12, 24, 36, 48, 1, 13, 25, 37, 49

so access to 1, 21, 41, 61, 81 all hits: set 0 contains block with array[0 to 3] set 5 contains block with array[20 to 23] etc.

## C and cache misses (3, solution)

ints 4 byte  $\rightarrow$  array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

accessing array indices 0, 12, 24, 36, 48, 1, 13, 25, 37, 49

so access to 1, 21, 41, 61, 81 all hits: set 0 contains block with array[0 to 3] set 5 contains block with array[20 to 23] etc.

# C and cache misses (3, solution)

ints 4 byte  $\rightarrow$  array[0 to 3] and array[16 to 19] in same cache set 64B = 16 ints stored per way 4 sets total

accessing array indices 0, 12, 24, 36, 48, 1, 13, 25, 37, 49

0 (set 0, array[0 to 3]), 12 (set 3), 24 (set 2), 36 (set 1), 48 (set 0) each set used at most twice no replacement needed

```

so access to 1, 21, 41, 61, 81 all hits:

set 0 contains block with array[0 to 3]

set 5 contains block with array[20 to 23]

etc.

```

# C and cache misses (3)

```

typedef struct {

int a_value, b_value;

int boring_values[126];

} item;

item items[8]; // 4 KB array

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 8; ++i)

a_sum += items[i].a_value;

for (int i = 0; i < 8; ++i)

b_sum += items[i].b_value;</pre>

```

Assume everything but items is kept in registers (and the compiler does not do anything funny).

How many *data cache misses* on a 2KB direct-mapped cache with 16B cache blocks?

## C and cache misses (3, rewritten?)

# C and cache misses (4)

```

typedef struct {

int a_value, b_value;

int boring_values[126];

} item;

item items[8]; // 4 KB array

int a_sum = 0, b_sum = 0;

for (int i = 0; i < 8; ++i)

a_sum += items[i].a_value;

for (int i = 0; i < 8; ++i)

b_sum += items[i].b_value;</pre>

```

Assume everything but items is kept in registers (and the compiler does not do anything funny).

How many *data cache misses* on a 4-way set associative 2KB direct-mapped cache with 16B cache blocks?

2KB direct-mapped cache with 16B blocks — set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ...

set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ...

•••

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ...

2KB direct-mapped cache with 16B blocks — set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ...

set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ...

•••

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ...

2KB direct-mapped cache with 16B blocks —

- set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ... block at 0: array[0] through array[3]

- set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ... block at 16: array[4] through array[7]

•••

set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ... block at 2032: array[508] through array[511]

2KB direct-mapped cache with 16B blocks —

- set 0: address 0 to 15, (0 to 15) + 2KB, (0 to 15) + 4KB, ... block at 0: array[0] through array[3] block at 0+2KB: array[512] through array[515]

- set 1: address 16 to 31, (16 to 31) + 2KB, (16 to 31) + 4KB, ... block at 16: array[4] through array[7] block at 16+2KB: array[516] through array[519]

- •••

- set 127: address 2032 to 2047, (2032 to 2047) + 2KB, ... block at 2032: array[508] through array[511] block at 2032+2KB: array[1020] through array[1023]

2KB 2-way set associative cache with 16B blocks: block addresses

set 0: address 0, 0 + 2KB, 0 + 4KB, ...

#### set 1: address 16, 16 + 2KB, 16 + 4KB, ...

•••

set 63: address 1008, 2032 + 2KB, 2032 + 4KB  $\ldots$

2KB 2-way set associative cache with 16B blocks: block addresses

set 0: address 0, 0 + 2KB, 0 + 4KB, ... block at 0: array[0] through array[3]

```

set 1: address 16, 16 + 2KB, 16 + 4KB, ...

address 16: array[4] through array[7]

```

...

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ... address 1008: array[252] through array[255]

2KB 2-way set associative cache with 16B blocks: block addresses

set 0: address 0, 0 + 2KB, 0 + 4KB, ... block at 0: array[0] through array[3] block at 0+1KB: array[256] through array[259] block at 0+2KB: array[512] through array[515] ...

set 1: address 16, 16 + 2KB, 16 + 4KB, ... address 16: array[4] through array[7]

...

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ... address 1008: array[252] through array[255]

2KB 2-way set associative cache with 16B blocks: block addresses

```

set 0: address 0, 0 + 2KB, 0 + 4KB, ...

block at 0: array[0] through array[3]

block at 0+1KB: array[256] through array[259]

block at 0+2KB: array[512] through array[515]

...

```

```

set 1: address 16, 16 + 2KB, 16 + 4KB, ...

address 16: array[4] through array[7]

```

...

```

set 63: address 1008, 2032 + 2KB, 2032 + 4KB ... address 1008: array[252] through array[255]

```

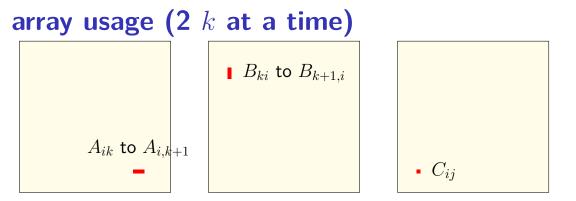

## simple blocking – with 3?

for (int kk = 0; kk < N; kk += 3) for (int i = 0; i < N; i += 1) for (int j = 0; j < N; ++j) {</pre> C[i\*N+j] += A[i\*N+kk+0] \* B[(kk+0)\*N+j];C[i\*N+i] += A[i\*N+kk+1] \* B[(kk+1)\*N+i];C[i\*N+j] += A[i\*N+kk+2] \* B[(kk+2)\*N+j];}  $\frac{N}{3} \cdot N$  j-loop iterations, and (assuming N large): about 1 misses from A per j-loop iteration  $N^2/3$  total misses (before blocking:  $N^2$ ) about  $3N \div block$  size misses from B per j-loop iteration  $N^3 \div$  block size total misses (same as before) about  $3N \div \text{block}$  size misses from C per j-loop iteration  $N^3 \div$  block size total misses (same as before)

## simple blocking – with 3?

```

for (int kk = 0; kk < N; kk += 3)

for (int i = 0; i < N; i += 1)

for (int j = 0; j < N; ++j) {</pre>

C[i*N+j] += A[i*N+kk+0] * B[(kk+0)*N+j];

C[i*N+i] += A[i*N+kk+1] * B[(kk+1)*N+i];

C[i*N+j] += A[i*N+kk+2] * B[(kk+2)*N+j];

}

\frac{N}{3} \cdot N j-loop iterations, and (assuming N large):

about 1 misses from A per j-loop iteration

N^2/3 total misses (before blocking: N^2)

about 3N \div block size misses from B per j-loop iteration

N^3 \div block size total misses (same as before)

about 3N \div \text{block} size misses from C per j-loop iteration

N^3 \div block size total misses (same as before)

```

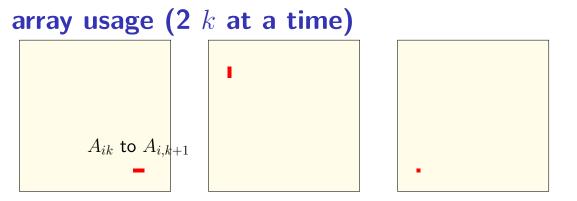

#### more than 3?

can we just keep doing this increase from 3 to some large X? ... assumption: X values from A would stay in cache

X too large — cache not big enough

assumption: X blocks from B would help with spatial locality X too large — evicted from cache before next iteration

within innermost loop good spatial locality in  ${\cal A}$  bad locality in  ${\cal B}$  good temporal locality in C

loop over j: better spatial locality over A than before; still good temporal locality for A

loop over j: spatial locality over B is worse but probably not more misses cache needs to keep two cache blocks for next iter instead of one (probably has the space left over!)

for each kk: for each i: for each j: for k=kk,kk+1  $C_{ij}+=A_{ik}$

right now: only really care about keeping 4 cache blocks in j loop

for k=kk,kk+1: have more than 4 cache blocks?  $C_{ij}+=A_{ik}$ . increasing kk increment would use more of them

#### keeping values in cache

can't explicitly ensure values are kept in cache

...but reusing values *effectively* does this cache will try to keep recently used values

cache optimization ideas: choose what's in the cache for thinking about it: load values explicitly for implementing it: access only values we want loaded