### Caches

Samira Khan March 23, 2017

### Agenda

- Review from last lecture

- Data flow model

- Memory hierarchy

- More Caches

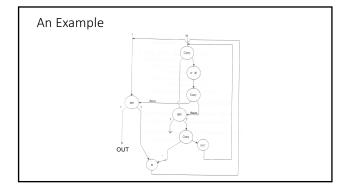

### The Dataflow Model (of a Computer)

- Von Neumann model: An instruction is fetched and executed in control flow order

• As specified by the instruction pointer

- Sequential unless explicit control flow instruction

- Dataflow model: An instruction is fetched and executed in data flow order

- i.e., when its operands are ready

- I.e., when its operants are ready

i.e., there is no instruction pointer

Instruction ordering specified by data flow dependence

Each instruction specifies "who" should receive the result

An instruction can "fire" whenever all operands are received

Potentially many instructions can execute at the same time

Inherently more parallel

### Data Flow Advantages/Disadvantages

- Advantages

- Very good at exploiting irregular parallelism

- Only real dependencies constrain processing

- Disadvantages

- Debugging difficult (no precise state)

- Interrupt/exception handling is difficult (what is precise state semantics?)

- Too much parallelism? (Parallelism control needed)

High bookkeeping overhead (tag matching, data storage)

Memory locality is not exploited

### OOO EXECUTION: RESTRICTED DATAFLOW

- An out-of-order engine dynamically builds the dataflow graph of a piece of the program

which piece?

- The dataflow graph is limited to the instruction window

Instruction window: all decoded but not yet retired instructions

- Can we do it for the whole program?

The Memory Hierarchy

### Ideal Memory

- Zero access time (latency)

- Infinite capacity

- Zero cost

- Infinite bandwidth (to support multiple accesses in parallel)

### The Problem

- Ideal memory's requirements oppose each other

- - Bigger → Takes longer to determine the location

- Faster is more expensive

- Memory technology: SRAM vs. DRAM vs. Disk vs. Tape

- Higher bandwidth is more expensive

- Need more banks, more ports, higher frequency, or faster

### Why Memory Hierarchy?

- We want both fast and large

- · But we cannot achieve both with a single level of memory

- Idea: Have multiple levels of storage (progressively bigger and slower as the levels are farther from the processor) and ensure most of the data the processor needs is kept in the fast(er) level(s)

### The Memory Hierarchy With good locality of reference, memory appears as fast as and as large as big but slow

### Memory Locality

- A "typical" program has a lot of locality in memory references

- typical programs are composed of "loops"

- Temporal: A program tends to reference the same memory location many times and all within a small window of time

- Spatial: A program tends to reference a cluster of memory locations at a time

- · most notable examples:

- instruction memory references

- array/data structure references

### Hierarchical Latency Analysis

- For a given memory hierarchy level i it has a technology-intrinsic access time of t<sub>L</sub>. The perceived access time  $T_i$  is longer than  $t_i$

- Except for the outer-most hierarchy, when looking for a given address there is

a chance (hit-rate h<sub>i</sub>) you "hit" and access time is t<sub>i</sub>

- a chance (miss-rate m<sub>i</sub>) you "miss" and access time t<sub>i</sub> +T<sub>i+1</sub>

- Thus

$\mathsf{T}_i = \mathsf{h}_i {\cdot} \mathsf{t}_i + \mathsf{m}_i {\cdot} (\mathsf{t}_i + \mathsf{T}_{i+1})$  $T_i = t_i + m_i \cdot T_{i+1}$

• Miss-rate of just the references that missed at Li-1

### Hierarchy Design Considerations

• Recursive latency equation

$$T_i = t_i + m_i \cdot T_{i+1}$$

- The goal: achieve desired T<sub>1</sub> within allowed cost

- $T_i \approx t_i$  is desirable

- Keep m; low

- increasing capacity C<sub>i</sub> lowers m<sub>i</sub>, but beware of increasing t<sub>i</sub>

- lower m, by smarter management (replacement::anticipate what you don't need, prefetching::anticipate what you will need)

- Keep T<sub>i+1</sub> low

faster lower hierarchies, but beware of increasing cost

- introduce intermediate hierarchies as a compromise

### Intel Pentium 4 Example

- 90nm P4, 3.6 GHz

- L1 D-cache

- if  $m_1$ =0.1,  $m_2$ =0.1  $T_1$ =7.6,  $T_2$ =36 • C<sub>1</sub> = 16K if m<sub>1</sub>=0.01, m<sub>2</sub>=0.01 • t<sub>1</sub> = 4 cyc int / 9 cycle fp T<sub>1</sub>=4.2, T<sub>2</sub>=19.8

if  $m_1$ =0.05,  $m_2$ =0.01 T<sub>1</sub>=5.00, T<sub>2</sub>=19.8

if m<sub>1</sub>=0.01, m<sub>2</sub>=0.50

T<sub>1</sub>=5.08, T<sub>2</sub>=108

- L2 D-cache

- C<sub>2</sub> =1024 KB • t<sub>2</sub> = 18 cyc int / 18 cyc fp

- Main memory

- $t_3 = \sim 50$ ns or 180 cyc

- best case latency is not 1

- worst case access latencies are into 500+ cycles

### Caching Basics

- Block (line): Unit of storage in the cache

Memory is logically divided into cache blocks that map to locations in the cache

- · When data referenced

- HIT: If in cache, use cached data instead of accessing memory

- MISS: If not in cache, bring block into cache

Maybe have to kick something else out to do it

- Some important cache design decisions

- Placement: where and how to place/find a block in cache?

Replacement: what data to remove to make room in cache?

- Granularity of management: large, small, uniform blocks?

Write policy: what do we do about writes?

Instructions/data: Do we treat them separately?

## A Basic Hardware Cache Design • We will start with a basic hardware cache design • Then, we will examine a multitude of ideas to make it better

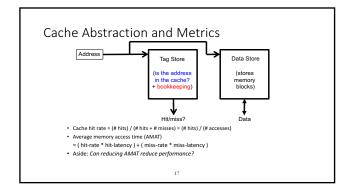

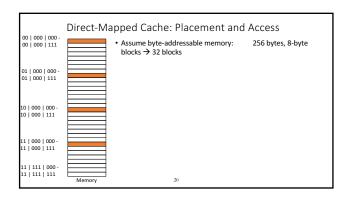

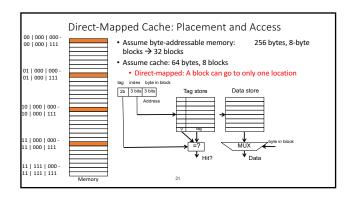

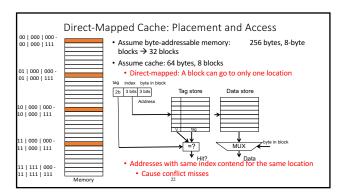

## Blocks and Addressing the Cache Memory is logically divided into fixed-size blocks Each block maps to a location in the cache, determined by the index bits in the address used to index into the tag and data stores Cache access: 1) index into the tag and data stores with index bits in address 2) check valid bit in tag store 3) compare tag bits in address with the stored tag in tag store If a block is in the cache (cache hit), the stored tag should be valid and match the tag of the block

### **Direct-Mapped Caches**

- Direct-mapped cache: Two blocks in memory that map to the same index in the cache cannot be present in the cache at the same time

- One index → one entry

- Can lead to 0% hit rate if more than one block accessed in an interleaved manner map to the same index

- Assume addresses A and B have the same index bits but different tag bits

- A, B, A, B, A, B, A, B, ...  $\rightarrow$  conflict in the cache index

- All accesses are conflict misses

23

### Exercise on Cache Indexing

- We assumed 8 byte blocks

- What happens if we have 16 byte blocks?

tag index byte in block

| ? bits | ? bits | 4 bits |

| 8-bit address

tag index byte in block

1 bits 3 bits 4 bits

8-bit address Direct mapped

- Cache is 128B, 8 blocks

- Direct mapped

- 2-way?

- 4-way?

- 8-way?

### Tag-Index-Offset

- m memory address bits

- S = 2<sup>s</sup> number of sets

- s (set) index bits

- B = 2<sup>b</sup> block size

- b (block) offset bits

- t = m (s + b) tag bits

- C = B \* S cache size (if direct-mapped)

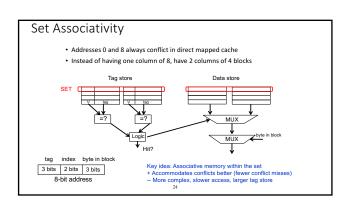

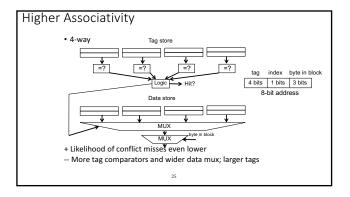

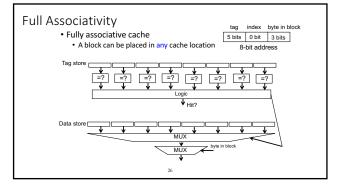

# Associativity (and Tradeoffs) • Degree of associativity: How many blocks can map to the same index (or set)? • Higher associativity ++ Higher hit rate - Slower cache access time (hit latency and data access latency) -- More expensive hardware (more comparators) • Diminishing returns from higher associativity

### Issues in Set-Associative Caches • Think of each block in a set having a "priority" • Indicating how important it is to keep the block in the cache • Key issue: How do you determine/adjust block priorities? • There are three key decisions in a set: • Insertion, promotion, eviction (replacement) • Insertion: What happens to priorities on a cache fill? • Where to insert the incoming block, whether or not to insert the block • Promotion: What happens to priorities on a cache hit? • Whether and how to change block priority • Eviction/replacement: What happens to priorities on a cache miss? • Which block to evict and how to adjust priorities

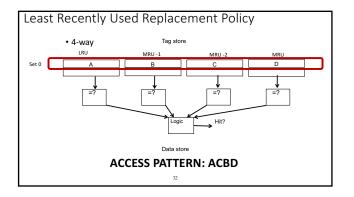

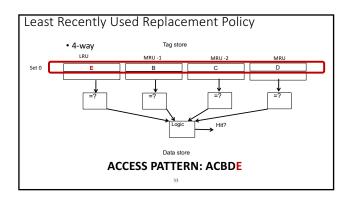

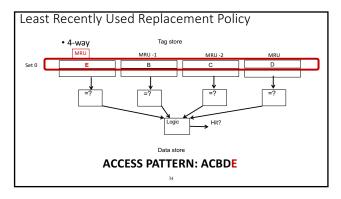

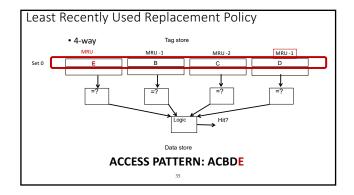

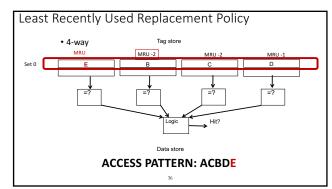

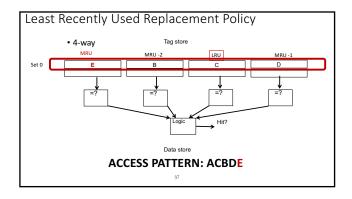

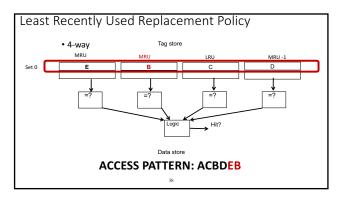

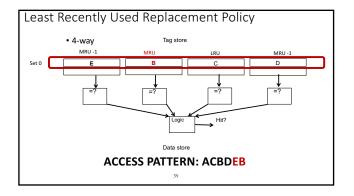

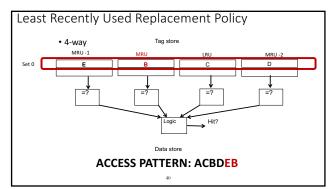

# Eviction/Replacement Policy • Which block in the set to replace on a cache miss? • Any invalid block first • If all are valid, consult the replacement policy • Random • FIFO • Least recently used (how to implement?) • Not most recently used • Least frequently used • Hybrid replacement policies • Optimal replacement policy?

### Eviction/Replacement Policy

- Which block in the set to replace on a cache miss?

Any invalid block first

If all are valid, consult the replacement policy

Random

FIFO

Least recently used (how to implement?)

Not most recently used

Least frequently used

Hybrid replacement policies

Optimal replacement policy?