# Unification of Register Allocation and Instruction Scheduling in Compilers for Fine-Grain Parallel Architectures

by

David A. Berson

B.A., Coe College, 1984

M.S., University of DePaul, 1988

Submitted to the Graduate Faculty of Arts and Sciences in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> University of Pittsburgh 1996

© Copyright by David A. Berson 1996

# UNIVERSITY OF PITTSBURGH FACULTY OF ARTS AND SCIENCES

| This dissertation was presented |  |

|---------------------------------|--|

| by                              |  |

| <br>David A. Berson             |  |

|                                 |  |

| It was defended on              |  |

| <br>Novemember 21 1996          |  |

| and approved by                 |  |

| Prof. Rajiv Gupta               |  |

| Prof. Mary Lou Soffa            |  |

| Prof. Henry Chuang              |  |

| Prof. Thomas Cain               |  |

|                                 |  |

|                                 |  |

# UNIFICATION OF REGISTER ALLOCATION AND INSTRUCTION SCHEDULING IN COMPILERS FOR FINE-GRAIN PARALLEL ARCHITECTURES

David A. Berson, Ph.D. University of Pittsburgh, 1996

The interaction between instruction scheduling and register allocation has significant impact on the quality of code generated, particularly in compilers targeting fine grain parallel architectures. The problem results from the fact that instruction scheduling and register allocation have conflicting goals. Instruction scheduling tries to maximize parallelism by scheduling as many instructions as possible in parallel, which requires a large number of values to be held in registers for short periods of time. On the other hand, register allocation attempts to hold a small number of values in registers for long periods of time, resulting in limiting the number of instructions that can be scheduled in parallel.

This dissertation presents a method for unifying these tasks by allocating all needed registers and functional units to an instruction simultaneously. No previous technique has achieved this degree of integration between the two tasks. The work in this dissertation is based on a framework consisting of three components: a technique for measuring a program's demand for all resources, a single intermediate representation of the measured demands, and a set of transformations that perform resource allocation.

The approach taken in this work is based on a new paradigm of resource allocation, called Measure and Reduce in which the resource requirements of the program are measured and excessive demands are removed by reduction transformations. The information computed during the measurement of the demands for each resource is incorporated into a single intermediate representation. The reduction transformations for all resources operate on this intermediate representation, allowing transformations for different types of resources to be performed simultaneously. Therefore, an instruction can be allocated all resources it needs at once, resulting in unified resource allocation. The intermediate representation is based on a hierarchical form of dependence DAGs, enabling the transformations to naturally handle instruction level parallelism. In particular, the register transformations form a framework for live range splitting in the absence of a full ordering of the instructions, as required by previous splitting techniques.

Application of the reduction transformations is first demonstrated by a heuristic for performing register allocation during local instruction scheduling. Global register allocation is performed by exploiting the hierarchical nature of the intermediate representation. Heuristics are also given for using the transformations during global code motion, resulting in unified allocation and a more flexible use of available resources than previous resource constrained techniques.

The results of numerous experiments comparing the new techniques to previous attempts at phase integration are reported. The experiments indicate that the unified allocation of resources generates higher quality code than methods that partially integrate the allocation phases. In addition, while precise measurement of register requirements is NP-Complete, in practice precise measurements are obtained easily and efficiently. Thus, when these measurements are combined with traditional register allocation techniques in hybrid algorithms, the quality of code generated is improved.

In memory of Elizabeth Marie Hartquist, who saw her son start.

For everything there is a season, and a time for every matter under heaven. Ecclesiastes  $3{:}1$

### Acknowledgements

During the phases of this research I have been aided by a number of people. I take this opportunity to thank them for the various contributions they have made to help me reach my goals.

I would like to express my appreciation and thanks to my co-advisors, Drs. Rajiv Gupta and Mary Lou Soffa for their guidance, examples as teachers and researchers, and their patience. I am also grateful to the members of my thesis committee, Drs. Henry Chuang and Thomas Cain, for their review and suggestions concerning this research.

I acknowledge the Dean of Faculty of Arts and Sciences Office and the Mellon Foundation for providing financial support in the form of fellowships. This work was also supported in part by the NSF<sup>1</sup>.

I would like to give special thanks to my fellow graduate students. Thanks to Claude-Nicholas Fiechter, Russ Bodik, and Phil Kamp for their work on the Program Dependence Graph C Compiler and for listening to all my suggestions and implementing the reasonable ones.

I would also like to thank the Intel Corporation for their willingness to hire me before I was quite finished and their patience while I completed the writing.

I would especially like to thank my wife, Karen, for her constant love, emotional support, and understanding through all the stages of this degree. I give my deepest appreciation to my daughter, Alannah, for her child's unconditional love and being my motivation to finish. I would like to thank my parents for their love and for instilling their value of education in me. Without their belief in my abilities and continual encouragement I never would have come so far.

Finally, I thank God for this experience. Without His love and gifts none of this would have been possible.

$<sup>^1</sup>$ National Science Foundation Presidential Young Investigator Award CCR-9157371 and Grant CCR-91090808 to the University of Pittsburgh

# Table of Contents

| Li | st of Figures                                                                                                                                                                                                                                                                                                                                                                           |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Li | st of Tables                                                                                                                                                                                                                                                                                                                                                                            |

| 1  | Introduction                                                                                                                                                                                                                                                                                                                                                                            |

| 2  | Related Work  2.1 Program Representations  2.2 Global Code Motion  2.3 Register Allocation 1  2.4 Integrated Register Allocation and Instruction Scheduling 1                                                                                                                                                                                                                           |

| 3  | Overview13.1 Unified Resource Allocation Framework13.2 URSA Applications1                                                                                                                                                                                                                                                                                                               |

| 4  | Resource Requirements       2         4.1       Measuring Resource Requirements       2         4.1.1       Measurement definitions       2         4.1.2       Measurement specifics for functional units and registers       2         4.2       Excessive Sets       2         4.3       Resource Holes       2                                                                      |

| 5  | Global Unified Resource Requirements Representation         3           5.1 Integrated Resource Allocation Representation         3           5.1.1 Integrated Resource Allocation Properties         3           5.1.2 GURRR         3           5.2 Computing GURRR         4           5.2.1 Construction of GURRR         4           5.2.2 Incremental Updating of GURRR         4 |

| 6  | Resource Spackling46.1 Filling Spanning Resource Holes46.2 Filling Non-spanning Resource holes5                                                                                                                                                                                                                                                                                         |

| 7  | Unified Allocation57.1 Local Scheduling and Register Allocation57.2 Finding Overlapping Holes57.3 Selection Heuristics5                                                                                                                                                                                                                                                                 |

| 8  | Global Code Motion                                                                                                                                                                                                                                                                                                                                                                      |

|     | 8.2          | Selection of Fill Sets                                 |       | <br> | <br> | <br>   |   | 68       |

|-----|--------------|--------------------------------------------------------|-------|------|------|--------|---|----------|

| 9   | HAR<br>9.1   | RE                                                     |       |      |      |        |   | 69<br>69 |

|     | $9.1 \\ 9.2$ | Allocation and spill code placement                    |       |      |      |        |   | 72       |

|     |              |                                                        |       |      |      |        |   |          |

|     | 9.3          | Assignment and placement of copy instructions          |       | <br> | <br> | <br>   | • | 77       |

| 10  |              | itectural Considerations                               |       |      |      |        |   | 81       |

|     |              | Instruction Pipelining                                 |       |      |      |        |   | 81       |

|     | 10.2         | Modeling Architectural Constraints                     |       |      |      |        |   | 86       |

|     |              | 10.2.1 Reserved Resource Copies                        |       |      |      |        |   | 86       |

|     |              | 10.2.2 Generic Instructions                            |       | <br> | <br> | <br>   |   | 88       |

| 11  | Impl         | lementation                                            |       | <br> | <br> | <br>   |   | 91       |

|     | _            | URSA Interfaces                                        |       |      |      |        |   | 91       |

|     |              | Representation                                         |       |      |      |        |   | 93       |

|     |              | Reuse DAG Decomposition                                |       |      |      |        |   | 96       |

| 10  | т.           |                                                        |       |      |      |        |   | 0.0      |

| 12  | 1            | erimentation                                           |       |      |      |        |   | 99       |

|     |              | Experimental Design                                    |       |      |      |        |   | 99       |

|     | 12.2         | Overview of the Algorithms                             |       | <br> | <br> | <br>٠. | • | 101      |

|     | 12.3         | Register Sensitive Schedulers (RSS)                    |       |      |      |        |   | 102      |

|     |              | 12.3.1 Base Techniques                                 |       |      |      |        |   | 103      |

|     |              | 12.3.2 Hybrid Register Sensitive Schedulers            |       |      |      |        |   | 104      |

|     | 12.4         | Schedule Sensitive Register Allocation (SSRA)          |       |      |      |        |   | 106      |

|     |              | 12.4.1 Base Techniques                                 |       |      |      |        |   | 106      |

|     |              | 12.4.2 Hybrid SSRA techniques                          |       |      |      |        |   | 107      |

|     |              | Unified Resource Allocation                            |       |      |      |        |   | 109      |

|     | 12.6         | Measurement and Compile Time Statistics                |       |      |      |        |   | 112      |

|     |              | 12.6.1 Measurement Heuristics                          |       |      |      |        |   | 112      |

|     |              | 12.6.2 Compilation Time                                |       |      |      |        |   | 115      |

|     | 12.7         | Comments                                               |       | <br> | <br> | <br>   |   | 115      |

| 13  | Conc         | cluding Remarks                                        |       | <br> | <br> | <br>   |   | 117      |

|     |              | Summary                                                |       |      |      |        |   | 117      |

|     |              | Future Work                                            |       |      |      |        |   | 119      |

|     | 1.           | : A ND C 14 1 H : 4: C C 1: W                          | :11() |      |      |        |   | 100      |

| Ap  | -            | ix A NP-Completeness and a Heuristic for Computing $K$ |       |      |      |        |   | 122      |

|     |              | NP-Completeness                                        |       |      |      |        |   | 122      |

|     | A.2          | Computing $Kill()$                                     |       | <br> | <br> | <br>   |   | 124      |

| Ap  | pendi        | ix B Speedup Tables                                    |       | <br> | <br> | <br>   |   | 128      |

| Bil | hliogr       | nhv                                                    |       |      |      |        |   | 147      |

# List of Figures

| 1.1 | Intermediate program representations                       | 3  |

|-----|------------------------------------------------------------|----|

| 1.2 | Resource conscious schedule                                | 5  |

| 3.1 | Comparison of back end organizations                       | 18 |

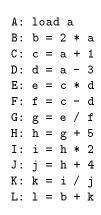

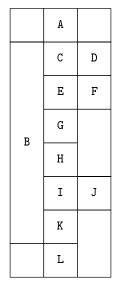

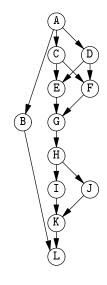

| 4.1 | Example code and corresponding DAG                         | 22 |

| 4.2 | Function measureRequirements()                             | 24 |

| 4.3 | A bipartite graph matching                                 | 25 |

| 4.4 | A complex case for defining $\mathit{Kill}()$              | 25 |

| 4.5 | Example DAG of a basic block                               | 30 |

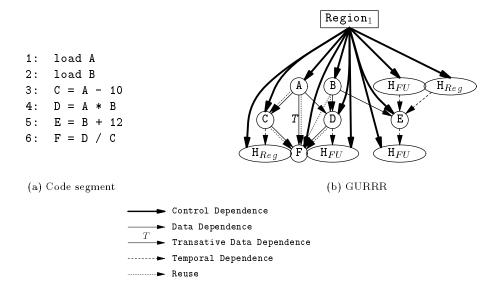

| 5.1 | Example of GURRR                                           | 36 |

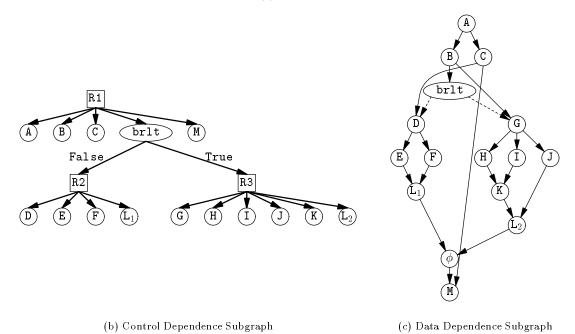

| 5.2 | Sample Code and GURRR Dependence Subgraphs                 | 38 |

| 5.3 | GURRR Resource Usage Information                           | 39 |

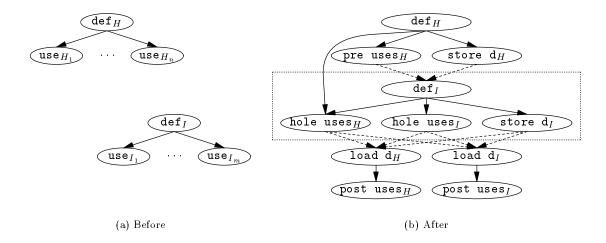

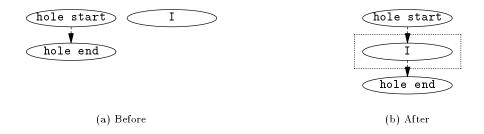

| 6.1 | Filling a non-spanning resource hole                       | 44 |

| 6.2 | Procedure spackleSpanning()                                | 46 |

| 6.3 | Procedure reduceSpanning()                                 | 47 |

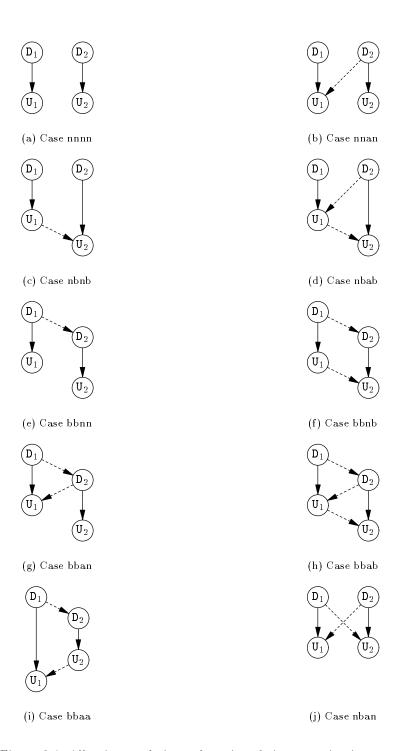

| 6.4 | All unique orderings of two interfering spanning instances | 51 |

| 6.5 | Filling a non-spanning resource hole                       | 53 |

| 7.1 | Function reduceBlock()                                     | 56 |

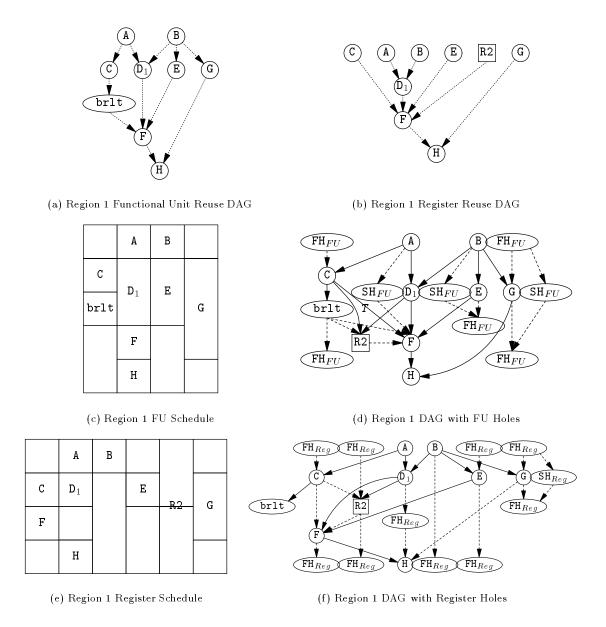

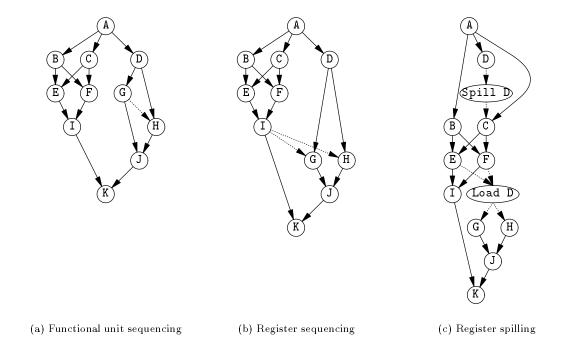

| 7.2 | Local reductions of resource requirements                  | 57 |

| 7.3 | Function findOverlappingHoles()                            | 58 |

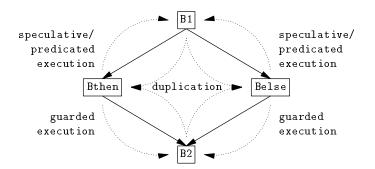

| 8.1 | Code motion techniques and architectural supports          | 63 |

| 8.2 | Function fill()                                            | 64 |

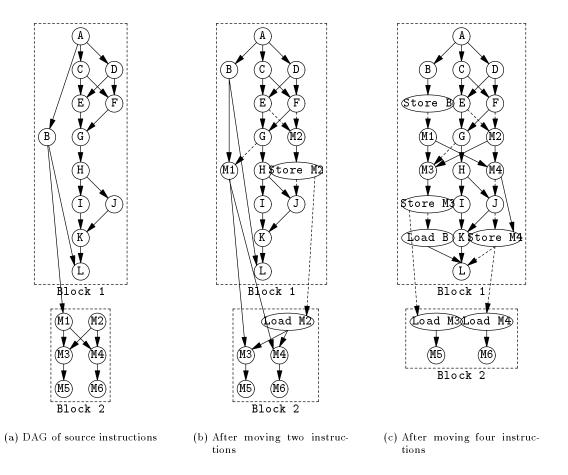

| 8.3         | Example of global code motion                          | 65  |

|-------------|--------------------------------------------------------|-----|

| 9.1         | Top level register allocation algorithm                | 70  |

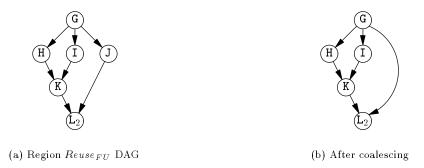

| 9.2         | Example of coalescing                                  | 72  |

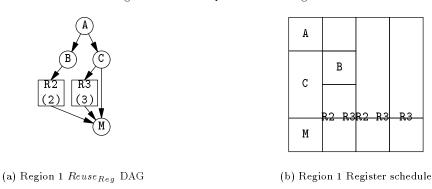

| 9.3         | Region 1 Register usage                                | 72  |

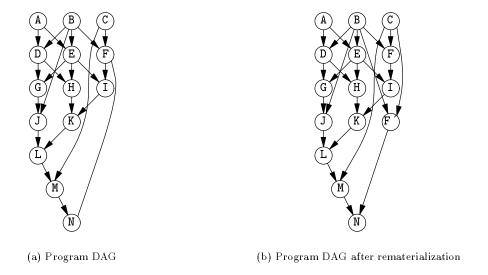

| 9.4         | Example of rematerialization                           | 73  |

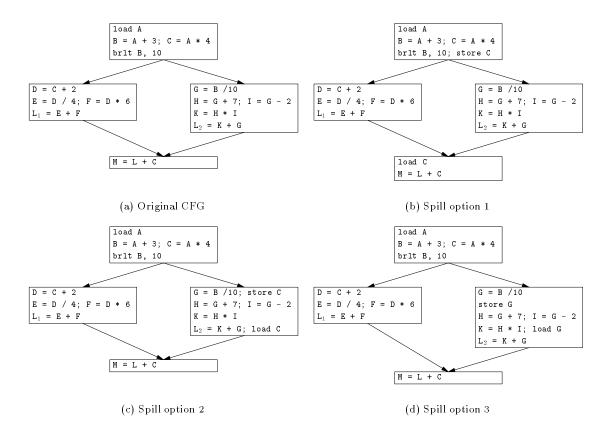

| 9.5         | CFGs for the spill options                             | 74  |

| 9.6         | Allocation cost estimation algorithm                   | 75  |

| 9.7         | Assignment algorithm                                   | 78  |

| 9.8         | SSA assignment algorithm                               | 79  |

| 9.9         | Final register assignment                              | 80  |

| 10.1        | Pipeline Example                                       | 84  |

| 10.2        | Relaxation procedures                                  | 84  |

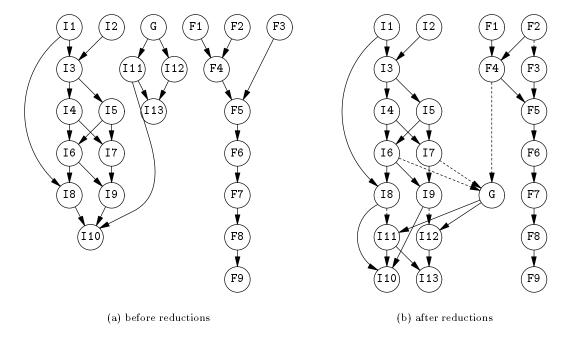

| 10.3        | DAG with reserved copy instructions                    | 87  |

| 10.4        | DAG with a generic requirement                         | 89  |

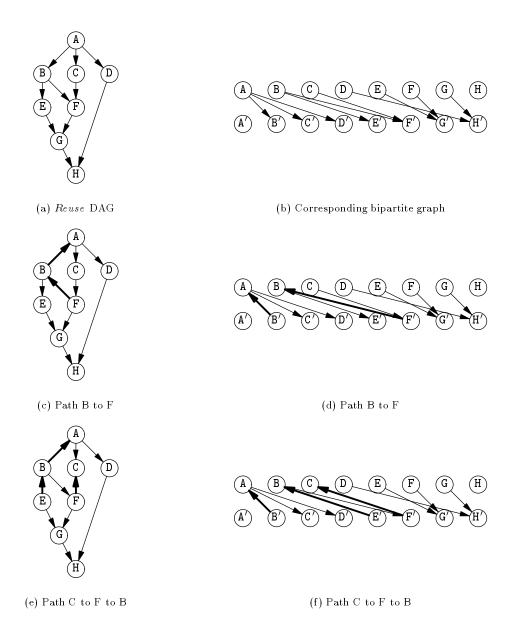

| 11.1        | Chain decomposition steps                              | 97  |

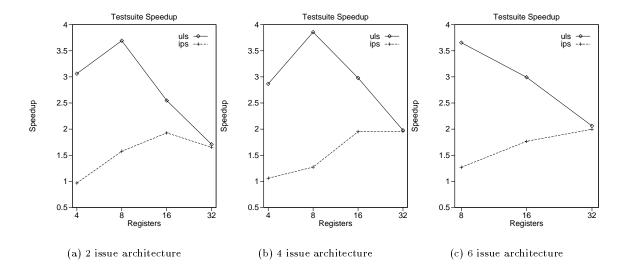

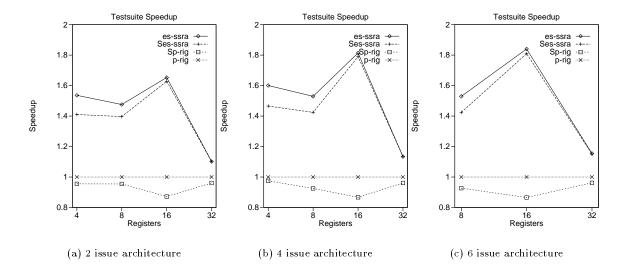

| 12.1        | Comparison of base RSS techniques                      | 103 |

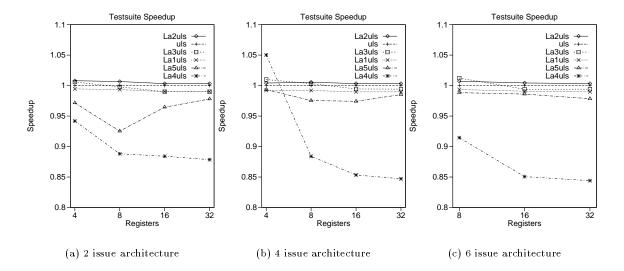

| 12.2        | Comparison of hybrid RSS techniques                    | 105 |

| 12.3        | Comparison of SSRA and RSS techniques                  | 107 |

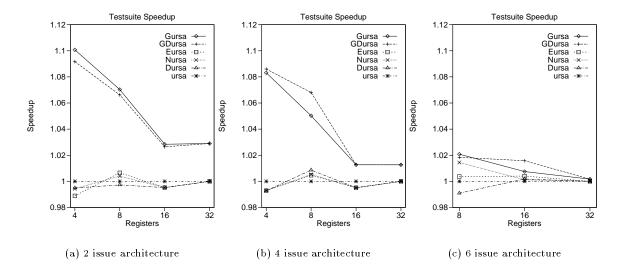

| 12.4        | Comparison of hybrid SSRA techniques                   | 108 |

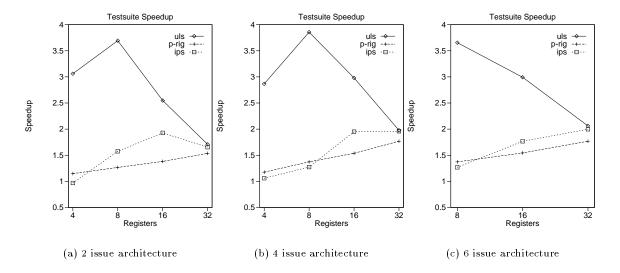

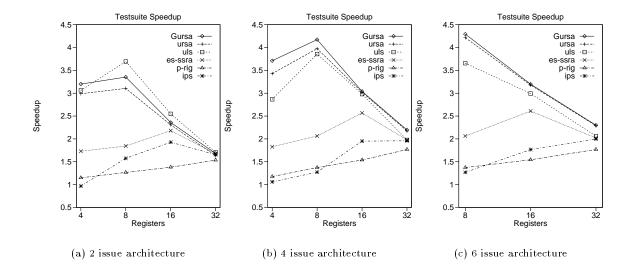

| 12.5        | Comparison of variant URSA techniques                  | 110 |

| 12.6        | Comparison of base and best techniques                 | 111 |

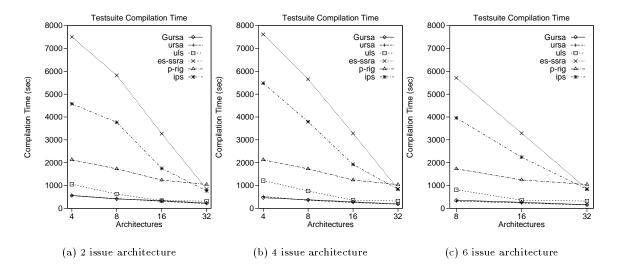

| 12.7        | Comparison of compilation times                        | 114 |

| <b>A</b> .1 | A complex case for defining $Kill()$                   | 123 |

| A.2         | A special case for partitioning into bipartite subDAGs | 125 |

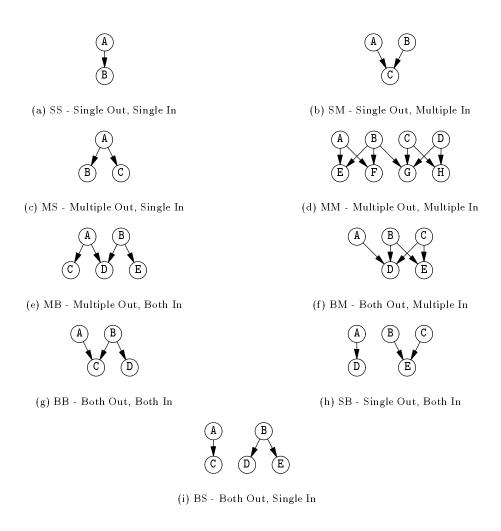

| A.3         | All combinations of Out and In nodes                   | 125 |

| A .4        | Function computeKill()                                 | 127 |

# List of Tables

| 4.1          | Computation of hole properties                                        | 29  |

|--------------|-----------------------------------------------------------------------|-----|

| 6.1          | Invalid and symmetrical orderings removed from consideration          | 50  |

| 6.2          | Splittings of interfering spanning instances                          | 52  |

| 12.1         | Benchmarks used for experimentation                                   | 100 |

| 12.2         | Critical path lengths and number of instructions for 2-4 architecture | 111 |

| B.1          | Individual speedups for the rss heuristics on architecture 2-4        | 128 |

| B.2          | Individual speedups for the rss heuristics on architecture 2-8        | 129 |

| B.3          | Individual speedups for the rss heuristics on architecture 2-16       | 129 |

| B.4          | Individual speedups for the rss heuristics on architecture 2-32       | 130 |

| B.5          | Individual speedups for the rss heuristics on architecture 4-4        | 130 |

| B.6          | Individual speedups for the rss heuristics on architecture 4-8        | 131 |

| B.7          | Individual speedups for the rss heuristics on architecture 4-16       | 131 |

| B.8          | Individual speedups for the rss heuristics on architecture 4-32       | 132 |

| <b>B</b> .9  | Individual speedups for the rss heuristics on architecture 6-8        | 132 |

| <b>B</b> .10 | Individual speedups for the rss heuristics on architecture 6-16       | 133 |

| B.11         | Individual speedups for the rss heuristics on architecture 6-32       | 133 |

| B.12         | Individual speedups for the ssra heuristics on architecture 2-4       | 134 |

| B.13         | Individual speedups for the ssra heuristics on architecture 2-8       | 134 |

| B.14         | Individual speedups for the ssra heuristics on architecture 2-16      | 135 |

| B.15         | Individual speedups for the ssra heuristics on architecture 2-32      | 135 |

| B.16         | Individual speedups for the ssra heuristics on architecture 4-4       | 136 |

| B.17         | Individual speedups for the ssra heuristics on architecture 4-8       | 136 |

| B.18 Individual speedups for the ssra heuristics on architecture 4-16 | 137 |

|-----------------------------------------------------------------------|-----|

| B.19 Individual speedups for the ssra heuristics on architecture 4-32 | 137 |

| B.20 Individual speedups for the ssra heuristics on architecture 6-8  | 138 |

| B.21 Individual speedups for the ssra heuristics on architecture 6-16 | 138 |

| B.22 Individual speedups for the ssra heuristics on architecture 6-32 | 139 |

| B.23 Individual speedups for the ursa heuristics on architecture 2-4  | 140 |

| B.24 Individual speedups for the ursa heuristics on architecture 2-8  | 140 |

| B.25 Individual speedups for the ursa heuristics on architecture 2-16 | 141 |

| B.26 Individual speedups for the ursa heuristics on architecture 2-32 | 141 |

| B.27 Individual speedups for the ursa heuristics on architecture 4-4  | 142 |

| B.28 Individual speedups for the ursa heuristics on architecture 4-8  | 142 |

| B.29 Individual speedups for the ursa heuristics on architecture 4-16 | 143 |

| B.30 Individual speedups for the ursa heuristics on architecture 4-32 | 143 |

| B.31 Individual speedups for the ursa heuristics on architecture 6-8  | 144 |

| B.32 Individual speedups for the ursa heuristics on architecture 6-16 | 144 |

| B.33 Individual speedups for the ursa heuristics on architecture 6-32 | 145 |

## Chapter 1

#### Introduction

The relentless push for more computing power has brought computer architectures that exploit instruction level parallelism (ILP) into every day environments in the form of superscalar and VLIW workstations and desktop computers. With each advance in computer architectures, the synergy between architectures and compilers becomes more apparent, presenting new challenges for compilers. These challenges introduce new complexities to previously addressed tasks and high-light the drawbacks of the way in which compilers were structured for previous architectures. This dissertation presents new methods to generate higher quality code for ILP architectures by creating advanced techniques for register allocation and instruction scheduling. These techniques are specifically designed to address the new complexities caused by ILP while avoiding the drawbacks resulting from straightforward extensions of previous register allocation and instruction scheduling techniques.

Because of the number and complexity of tasks that must be performed in a compiler, the compilation process has been divided into manageable units called phases. These phases are grouped together based on the representation of the program that they use. Each phase typically solves one particular problem. As a result of addressing each problem separately, effective heuristics can be developed for each problem, allowing a good solution to the individual translation problems. However, the results of one phase can have an impact on the solution of the next phase, and thus the overall quality of the generated code. This impact can have a negative result on the overall code quality.

The separation of the compilation process into phases does not consider possible interactions between the tasks performed. For example, consider the interaction between instruction scheduling and register allocation. Both precedence constrained instruction scheduling and register allocation are well known NP-complete problems. Therefore, for purposes of achieving reasonable compile times, heuristics are used for both tasks. Instruction scheduling tends to require a large number of values to be live in registers to keep all of the functional units busy. On the other hand, register

allocation tends to keep fewer values live at a time in an effort to avoid the need for expensive memory accesses through register spills.

If register allocation is performed first, it limits the amount of ILP available by introducing additional dependences between the instructions based on temporal sharing of registers. If instruction scheduling is performed first it can create a schedule demanding more registers than are available, creating more work for the register allocator. In addition, the spill code subsequently generated must be placed in the schedule by a post pass cleanup scheduler.

In addition to the problem of interactions between the register allocation and instruction scheduling phases, the heuristics themselves must be changed to compensate for the added complexities of ILP. To fully exploit ILP the sequential order in which the instructions appear in the source code must be replaced with the partial ordering imposed by the data and control dependencies inherent in the program. In this partial ordering there is some freedom for instructions to move around in the schedule. While some instructions are on a maximum length path through the ordering, others have slack time in when they can be scheduled. Techniques must be developed to guide the selection of an instruction order that exploits ILP while maintaining resource requirements at a level supported by the architecture.

The goal of this research is to redesign the compiler back end to unify the phases performing resource allocation and to make the remaining phases, such as global code motion, conscious of their impact on resource allocation and thus the resulting execution time of the program being compiled. Performing the allocation of all resources simultaneously achieves a higher degree of integration than previous techniques proposed. The benefit of this degree of integration is that the impact of all allocation decisions can be assessed in terms of the overall resource allocation problem and thus the quality of code generated.

#### 1.1 Previous Approaches

Approaches to integrating register allocation and instruction scheduling can be characterized by three properties: the degree of exploitation of ILP, the degree of integration, and the representations used. The degree of exploitation of ILP can be viewed as the extent to which the information about inherent parallelism is used during instruction scheduling and register allocation. At one end are heuristics that assume a complete ordering, typically the ordering provided by the programmer. At the other end are techniques that rely solely on the partial ordering determined by the minimal dependences needed to preserve semantic correctness. In the middle are techniques that use the partial ordering

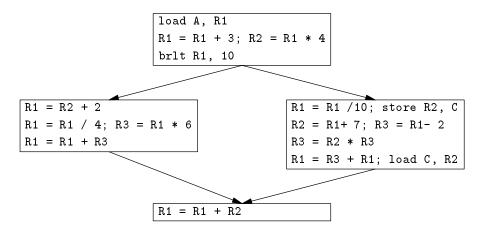

Figure 1.1: Intermediate program representations

for only some tasks, (e.g., instruction scheduling) or use it for parts of a task (e.g., during register allocation information about parallelism may be used for computing live ranges but not for selecting spill points). Such techniques exploit parallelism by selecting orderings of instructions to achieve better resource utilization without unnecessarily reducing available parallelism.

The degree of integration achieved between the heuristics can also vary significantly. At one end are approaches in which the tasks are performed independently in separate phases, resulting in no integration. At the other end is unification, that is, both tasks are performed simultaneously in a single phase. A unified phase gives equal consideration to both tasks during each allocation decision. In the middle of the spectrum are a number of approaches that use separate phases for each task but incorporate varying types and amounts of information from one heuristic into the other to add limited "awareness" of the heuristic's impact on subsequent heuristics. Closely related to the integration of phases is the types of representations used for each task. The use of vastly different representations used by instruction scheduling and register allocation presents a major obstacle to integration as incorporation of information in different forms is difficult.

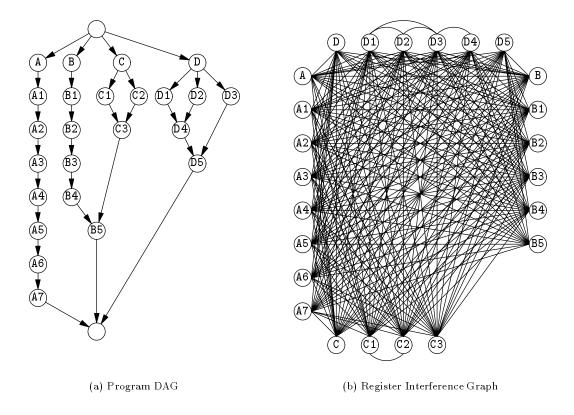

The straightforward approach to generate code for ILP architectures is to first schedule the instructions using list scheduling and then allocate registers using traditional graph coloring algorithms. List scheduling naturally exploits inherent ILP as it traverses the program's instructions. Coloring based register allocation has no concept of ILP and only takes advantage of parallelism if it happens to generate spill code near idle slots in the schedule. The separation of the tasks offers little opportunity for integration as each task uses a vastly different representation of the program. List scheduling uses a Directed Acyclic Graph (DAG) while coloring base register allocation uses an interference graph. Figure 1.1(a) shows a sample program DAG while Figure 1.1(b) shows the corresponding interference graph. There is no obvious method to incorporate the information in these two representations into one common representation. Thus, it is not obvious how to consider register interferences during instruction scheduling or instruction heights during register allocation.

An alternative to considering register interferences during scheduling is to track register pressure. Goodman and Hsu present such an algorithm [GH88]. In their algorithm the scheduler alternates between two states. In the first state register pressure is low and the scheduler selects instructions to exploit ILP. When the register pressure crosses a threshold the scheduler switches to a second state that selects instructions to reduce register pressure, possibly sacrificing opportunities to exploit ILP in the process. Additionally, no spilling of values is performed. When register pressure falls back below the threshold, the first state is reentered. In this manner scheduling and allocation are partially integrated using a single representation. A problem arises in that the scheduler cannot always select instructions to keep register pressure below the maximum allowed by the architecture. Furthermore, some programs have sufficiently complex register interferences such that some values must be spilled. As a result, a cleanup register allocation phase must be run subsequent to the integrated scheduler. This cleanup phase uses traditional coloring base register allocation, resulting in the degradation of instruction scheduling.

A problem with considering register allocation issues during instruction scheduling is that scheduling for ILP replaces the programmer's complete ordering of instructions with a partial order representing the parallelism available. As a result, live ranges that did not interfere because they were temporally ordered will interfere once the temporal ordering is removed. Recent research has extended register allocation techniques to address this possible overlapping of live ranges [Pin93, NP93]. However, these techniques still do not fully exploit the partial ordering information available to address the problems of which values to select for spilling and where to place the spill code.

A fundamental problem in integrating instruction scheduling and register allocation is the fact that heuristics for each problem use vastly different representations that do not provide uniformly adequate information for both problems being addressed. Consider the program DAG in Figure 1.1(a) and assume that there are three functional units and five registers available to execute the DAG. To exploit all available parallelism seven functional units and seven registers are needed to execute the

Figure 1.2: Resource conscious schedule

instructions A1, B1, C1, C2, D1, D2, and D3 in parallel. List scheduling based on critical path lengths would select A and B for the first instruction issue slot and then would have to make a choice between C and D. Ideally, the scheduler would be able to "look ahead" and see that scheduling D with A and B would push register pressure over the limit when attempting to schedule subsequent cycles. As a result C would be scheduled with A and B, while D would be delayed until more registers are available. The result of such a scheduling decision is shown in Figure 1.2. By delaying D the length of the schedule has increased by only one instruction cycle and no spill code is needed.

Previous integration of register pressure into list scheduling is only able to compute register pressure based on the instructions already scheduled. After selecting A and B for the first slot the register pressure is only two, suggesting that there is no problem. Previous techniques for integrating scheduling information into register allocation guide the selection of which value to spill based on the relative slack times of the candidates for spilling. Unfortunately, slack time does not provide sufficient information to determine when spilling can be avoided.

#### 1.2 Unification

This dissertation develops a new technique to integrate register allocation and instruction scheduling.

The technique includes a new representation and algorithms that use the representation to alloca-

tion registers and functional units simultaneously. The representation, the Global Unified Resource Requirements Representation (GURRR), combines information about a program's requirements for both registers and functional units with scheduling information in a single DAG based representation. In this manner GURRR facilitates the determination of the impact of all scheduling and allocation decisions on the critical path length of the code affected.

GURRR is based on a key concept of computing resource requirement measurements, referred to as Unified ReSource Allocation (URSA), which computes sets of instructions that can safely share a single instance of a resource. From this information URSA computes the minimum number of instances of the resource needed to exploit all available parallelism. In terms of registers, this computation determines the maximum number of values that can be alive simultaneously. Although the specific computations of resource sharing differ for functional units and registers, the results of the computations for both types of resources are easily incorporated onto the program DAG.

A byproduct of the computation of how many instances of a particular resource are needed by a program is a set of elements that each represents a group of instructions that can share a single instance of the resource. This information is used to precisely identify the areas of the program where the resource is either over or under utilized. GURRR also incorporates this utilization information in its representation.

The availability of utilization level information suggests a new approach to resource allocation, the *Measure and Reduce* paradigm. This paradigm is based on the observation that allocation decisions are only required when the need for resources exceeds the number actually available. Under this paradigm, the resource usage information is used to select instructions to move from over utilized areas to under utilized areas. This process of moving instructions to the under utilized areas is referred to as *Resource Spackling*. The combination of utilization level information for all resources with direct access to scheduling information enables new unified resource allocation techniques. By allocating all resources needed by an instruction simultaneously, and making allocation decisions based on their impact on the critical path length, a unified allocation phase is achieved.

Advantageous application of Resource Spackling to individual instructions depends on heuristics that select instructions and determine the best place to spackle them. Several such heuristics are presented. The first heuristic applies Resource Spackling to local instruction scheduling and register allocation. This heuristic naturally performs global register allocation when applied to a hierarchical intermediate representation in a bottom up manner. Global register allocation and assignment include other issues such as assignment and copy placement. Hierarchical Allocation of REgisters (HARE) was developed as a part of this work to be such a heuristic. A heuristic for incorporating

Resource Spackling into global code motion is also presented. These heuristics must also consider architectural features such as pipeline interlocks and resources with special usage characteristics. Extensions to the heuristics to address these features are discussed.

#### 1.3 Organization of the Thesis

The remainder of this dissertation discusses the realization of the techniques highlighted here, and addresses the practical considerations of target architectures and comparisons to previous techniques. Chapter 2 discusses previous work by other researchers related to the work presented in this dissertation. Chapter 3 gives an overview of the components developed in this work and how they fit together. Chapter 4 describes the measurement of resource requirements. Chapter 5 shows how the resource requirements are incorporated into an intermediate representation. Chapter 6 gives the theoretical basis for performing resource allocation using the information computed and provided in the intermediate representation. Chapter 7 describes heuristics for performing resource allocation for functional units and registers simultaneously in a local scheduler. Chapter 8 describes how unified resource allocation is performed during global code motion. Chapter 9 addresses issues related to global register allocation and assignment. Chapter 10 incorporates ILP architectural features and constraints into the resource measurement and allocation model. Chapter 11 describes important methods used in the prototype implementation. Chapter 12 presents and analyzes the experiments performed in this work. Finally, chapter 13 contains the conclusions of this work and directions for future research.

# Chapter 2

### Related Work

Register allocation and instruction scheduling are well known problems in compiler research and their interactions have been previously studied. This chapter discusses research in these areas as it relates to the dissertation, as well as the intermediate representations on which the heuristics for these problems depend.

#### 2.1 Program Representations

The contribution of each in task in the compiler to the quality of code generated is dependent on the power of transformations enabled by the intermediate representation used. In particular, instruction scheduling and global code motion depend on specific properties of the representation to perform powerful transformations.

Traditionally, compilers have used the Control Flow Graph (CFG) and basic block dependence DAGs as the intermediate representations for instruction scheduling due to their straightforward computation and concise representation of the program. The CFG is also used to collect a variety of information, including dataflow information and value live ranges, used to construct register interference graphs [ASU86]. A number of extensions to the CFG have been created to aid the various tasks performed in the back end of the compiler.

In order to provide a larger scope for global code motion heuristics, basic blocks have been grouped together in a variety of ways. Traces [Fis81], Super Blocks [HMC+93], and Hyper Blocks [MLC+92] each form collections of basic blocks which satisfy properties required by specific scheduling techniques.

The Program Dependence Graph (PDG) is another representation which combines control and data dependence information in a way that simplifies many transformations [FOW87]. Control dependencies are used to identify regions of instructions that execute under the same conditions.

Regions support more powerful global code motion techniques than are possible on CFG based representations [GS90, BR91].

Another method for enabling global code motions is to convert the intermediate representation into Static Single Assignment (SSA) form, which uniquely assigns names to each definition of a variable [RWZ88]. The use of unique names simplifies constant propagation and other analysis [AWZ88]. Furthermore, SSA removes false dependences which would otherwise limit the range of motion for instructions, *i.e.*, due to anti and output dependencies. SSA was originally formulated on the CFG but has been incorporated in PDG based representations [BMO90].

The Program Structure Tree (PST) is a hierarchical representation that can be used by divide-and-conquer algorithms to speedup dataflow analysis and computation of SSA [JPP94]. A number of representations allowing direct interpretation have been proposed, including the Dependence Flow Graph [PBJ+91, JP93] and Value Dependence Graph [WCES94]. However, these representations do not directly identify the control dependencies desired by region-based global code motion algorithms. The Program Dependence Web [BMO90] is an interpretable representation that places a variation of SSA form on the PDG.

While many of the representations mentioned support powerful forms of instruction scheduling and global code motion, none of them provide resource usage information such as total register and functional unit demands. As a result, these representations cannot be used as is for unified resource allocation.

#### 2.2 Global Code Motion

The movement of instructions between basic blocks is limited by both data and control dependences. In some cases architectural features can reduce these limitations. Speculative execution allows instructions to be moved above conditional branches by placing the results of the moved instructions in a shadow area [HP87, SHL92]. These results are then committed to the register file and memory only if and when the conditions for the instructions' execution are later met. Guarded execution associates a predicate with each instruction to be executed [DHB89, HD86]. The predicate represents the conditions under which the instruction should be executed. Instructions can be moved below a join in the control flow graph by using guarded execution to determine if the instruction should be executed or not. These techniques allow compilers more options when performing code motion.

Several compilation techniques that perform code motion to increase ILP have been developed. These techniques include Trace Scheduling [Fis81], Percolation Scheduling [AN88], and

Region Scheduling [GS90]. Each of these techniques has a different method of identifying instructions that may be moved and considers different approaches in selecting their potential destinations.

Trace Scheduling creates large basic blocks, called traces, consisting of sequences of basic blocks along a program path that has a high probability of being executed. Code reordering within a trace is used to generate a good schedule for the trace at the expense of decreased performance on off-trace blocks due to the insertion of compensation code in those blocks. Percolation Scheduling uses code motion operations on a control flow graph. The operations perform less code duplication than trace scheduling and place fewer restrictions on the movement of instructions. Region Scheduling's code motion operations operate on a Program Dependence Graph (PDG) [FOW87]. Region Scheduling identifies the largest set of potential destinations for an instruction and produces the least amount of code duplication.

Each of the above techniques uses list scheduling to schedule instructions and considers only functional units. There are several extensions to Percolation Scheduling to handle resource constraints. The first presents the idea of using a heuristic to control the application of operations in the presence of functional unit constraints [EN89]. Register constraints have also been addressed in a limited manner [ME92, Nor95]. However, these extensions do not consider using spilling to improve usage.

Another technique for increasing ILP across basic block boundaries is Shape Matching [MGS92]. This technique handles only functional units and attempts to overlap the ends of adjacent blocks. It is similar to Moon and Ebcioğlu's approach in that available resources in the middle of a block are not considered.

The scheduling techniques discussed so far have concentrated on using all available functional units, while mostly ignoring their impact on register allocation. Scheduling which consider the impact of scheduling on register allocation are discussed in section 2.4.

#### 2.3 Register Allocation

Traditionally, register allocation is performed by coloring an interference graph, whose nodes represent live ranges and edges the interference between the live ranges [CAC+81, Cha82]. This process assigns colors representing registers to live ranges. When there are insufficient registers available a live range is spilled to memory. Such a live range must be loaded into a register before each use and written back to memory after each definition. A priority function is used to select which live range to spill. The goal of the priority function is to minimize the number of memory accesses, both as a

result of the number of live ranges spilled and the number of times each value must be accessed from memory. The priority function is based on the cost of a spill divided by the number of interfering live ranges.

Several enhancements to the basic coloring process have been proposed to reduce the number of spills generated by the coloring process. Briggs suggests several heuristics for simplifying the interference graph to increase the likelihood of coloring the graph without resorting to spilling [BCKT89]. Although the original proposed priority function included an execution estimate factor in the computation of the cost of a spill, most subsequent methods have favored a factor using the loop nesting depth instead. The use of the loop nesting depth is motivated by the observation that spills inside of nested loops are executed more frequently than those at a shallower nesting depth or outside loops. Bernstein et al. use a combination of three different priority functions to select values for spilling that will remove the most interferences from the graph [BGM<sup>+</sup>89].

Live range splitting was introduced in an effort to reduce the cost of spilling [CH90, KH93]. When spilling is required the live range selected for spilling is split into several smaller live ranges. The smaller live ranges are then treated as separate values requiring registers. The essential idea is that some of the smaller live ranges will not need to be spilled and so will not need to access memory. Memory accesses will only be required for those smaller live ranges that are spilled.

Hierarchical register allocation has been introduced as a method for reducing the number of dynamic memory references [CK91]. This technique creates tiles corresponding to basic blocks in the control flow graph. The tiles are colored from the inside out with respect to the nesting of control structures. The result is that values in loops have a better chance of remaining in registers. This results in spilling pass-thru values, those values that are alive at entry and exit and are not used in a block, [CAC+81]. More recently, hierarchical allocation has been extended to PDGs [NP94].

These hierarchical approaches suffer from two problems. First, they only consider one case of placing spills in less frequently executed locations, *i.e.*, outside of loops. They do not try to place more spills in conditionally executed code and fewer spills in unconditionally executed code. Second, once a tile or region has been allocated registers, its values are never candidates for future spilling. The relative execution frequencies may be such that spilling inside a previously allocated tile or region results in a lower overall execution time.

The RASE technique attempts to balance the use of registers by local and global values by computing a cost function for each basic block [BEH91]. The cost function estimates the increase in the block's critical path length for a given number of registers. The cost includes a factor of the execution frequency of the block. The interference graph represents the number of registers required

by each basic block and the cost function is used to select basic blocks that should have their number of allocated registers reduced. Although RASE considers both execution counts and resulting critical paths lengths, it has a limited hierarchical view of registers, by viewing them as either global or local.

Probabilistic register allocation takes a different approach to register allocation [PF92]. This technique is based on the principle that the probability that a value is still in a register when an instruction needs to use it is roughly proportional to the inverse of the distance from its definition or last use to the current use. The technique uses the distances between definitions and uses of each value to compute initial value probabilities. Probabilities are also assigned to each control branch in the program. These branch probabilities are then multiplied with the initial value probabilities to reflect the effect of different control paths on the final value probabilities. The final value probabilities are then used as priorities for allocating registers to the values. The technique iteratively selects the highest priority value and allocates a register to it and then recomputes the probabilities and priorities of the remaining values.

Probabilistic register allocation does address the cost of spills from the point of view of spilling values that are least frequently executed; it favors spills in shallowly nested loops over deeply nested loops and in conditionally executed code over unconditionally executed code. However, it does not consider the scheduling of the generated spill code.

All of the allocation techniques discussed so far have been developed for single issue architectures. Two recent techniques have considered the impact of multiple issue architectures on the interference graph. Pinter has developed the parallel interference graph to represent the additional interferences between live ranges that occur when instructions can be reordered and issued in parallel [Pin93]. Norris and Pollock use a similar interference graph and attempt to reduce register pressure by making some scheduling decisions during register allocation [NP93]. Neither of these techniques addresses the selection of values for spilling to minimize the spill code's impact on the program's execution time.

All of these techniques use some form of the register interference graph as their intermediate representation. Although this graph is typically constructed by performing live range analysis on the CFG, it is quite different from the CFG. As a result, the representations used for instruction scheduling and register allocation do not lend themselves well to incorporating information about the impact of one task on the other.

#### 2.4 Integrated Register Allocation and Instruction Scheduling

Due to the known interaction between register allocation and instruction scheduling and its impact on resulting quality of generated code, previous research has investigated methods for integrating the two tasks. These techniques can be characterized as making one of the two tasks partially aware of its impact on the other. Two such approaches are possible based on the order in which the tasks are performed: register sensitive scheduling and schedule sensitive register allocation.

The register sensitive scheduling approach performs scheduling prior to register allocation so that the scheduler can make scheduling decisions that keep the demand for registers at or below the number available. Goodman and Hsu use a list scheduling approach that monitors the register pressure of the instructions scheduled in the form of the number of values live at each point in the schedule [GH88]. As each instruction is scheduled the register pressure value is updated by the number of live values defined and killed by the instruction. In its normal mode, the list scheduler selects instructions to schedule which are on the critical path of the block. However, when the register pressure rises above a preset threshold an alternate selection criteria is used. In this situation the scheduler selects instructions which reduce the register pressure by killing more values than it defines. Coloring based register allocation is subsequently performed to insert spills where scheduling was unable to restrict the number of registers needed to the number available. Extensions to this approach haven been made by Bradlee et al. [BEH91].

The schedule sensitive register allocator approach performs register allocation prior to instruction scheduling. One such approach is proposed by Bradlee et al. [BEH91]. A prepass scheduling phase is performed to construct a cost function for each basic block. These cost functions estimate the minimum number of registers that can be allocated to the block without significantly impacting its critical path length. Register allocation is then performed using register limits computed by the cost functions. A final instruction scheduling phase is then performed.

Another schedule sensitive register allocation approach is described by Norris and Pollock [NP93]. In their approach, the register allocator considers the impact of register allocations on the subsequent phase instruction scheduling. Since register allocation is performed first the instructions are not yet fully ordered. Thus the parallel form of the register inference graph must be used to represent live range interferences. The advantage of using only a partial ordering of the instructions is that register interferences can sometimes be removed by imposing temporal dependences on the instructions so that live ranges do not overlap. The disadvantage is that prior to this dissertation, no methods were known for performing live range splitting on a partial ordering of the instructions. Thus spilling was performed instead.

The integration techniques described were created to address the parallelism available in pipelined architectures. While they can be extended to target multiple issue architectures, they were not designed with the added complexities of these architectures in mind.

An integrated register allocation and scheduling method has also been introduced for soft-ware pipelining [NG93]. The goal of the technique is to minimize register requirements for a time optimal pipelined loop. It does not consider actual resource constraints and does not incorporate register spilling. In addition, the formulation of the problem as a linear programming problem limits its application to software pipelining of loops.

### Chapter 3

#### Overview

The research presented in this dissertation consists of a number of components designed to incorporate unified resource allocation into a compiler. As a result, there are many dependencies and interactions among these components. This chapter gives an overview of the concepts and components developed.

First, a framework is presented to support unified resource allocation. Second, compiler back end phases are either replaced with phases that perform unified resource allocation or are modified to take resource allocation into account when making decisions. These new or modified phases achieve unified resource allocation or resource allocation awareness by using the presented framework.

#### 3.1 Unified Resource Allocation Framework

The objective of Unified Resource Allocation is to support both the Measure and Reduce paradigm, and the ability to make back end phases aware of their impact on resource allocation. The Measure and Reduce paradigm is based on the observation that resource allocation decisions are only required when there is a demand for more resources than are available. When there are sufficient resources to meet the demand, only resource assignment must be performed, which must also consider its impact on the program's resulting execution time. In this paradigm, the task of resource allocation is viewed as reducing resource usage in the areas with excessive resource demands. These excessive areas must be located by measuring the resource demands of the program. The reductions are accomplished by performing transformations on the intermediate representation of a program. The URSA framework consists of three components: techniques for measuring the program's demands for resources, an intermediate representation of a program that indicates resource demands, and techniques to implement reductions in resource requirements.

The first component of the URSA framework is a set of techniques to compute resource requirements. When compiling a program to exploit ILP, the dependencies in an acyclic segment of the program are used to represent the set of all semantically correct ways of scheduling the segment. Different schedules may result in different resource requirements. The approach taken in the Measure and Reduce paradigm is to remove all schedules that result in excessive resource demands using the reduction techniques. The remaining set of schedules can safely be assigned the available resources. Thus, the measurement technique must consider the worst case schedule in terms of the number of resources required. Each type of resource may have one or more schedules that produces its worst case requirements.

In addition to computing the maximum number of resources required, the measurement techniques must identify the locations in a program where there are excessive resource demands and the locations where a resource is under utilized and available for additional allocations. These three types of resource measures are the result of the analysis techniques developed in this research.

Although resources like functional units and registers have different usage properties, their requirements are measured using a common technique. The technique uses a special relation that models the various usage properties to hide the details from the measurement technique. Issues of the precision of the measurements are addressed when dealing with register types of resources.

By operating on acyclic segments of a program, the measurement techniques can be used by a wide variety of compilers using different intermediate representations. This work concentrates on one particular intermediate representation which supports several advanced phases of interest for integration.

The intermediate representation used in URSA is called the Global Unified Resource Requirements Representation (GURRR). GURRR is based on an instruction level Program Dependence Graph (PDG). The PDG representation was chosen for several reasons. First, the dependencies represented in the PDG indicate which instructions in the program can be executed in parallel and which must be executed sequentially. Second, the PDG provides valuable control dependence information used by powerful global code motion techniques, which are important in exploiting ILP. Finally, the PDG is usable by many common optimization phases; therefore the phases do not have to be rewritten or designed for a new intermediate representation. A GURRR of a program is obtained from its PDG by adding the three types of resource requirements information computed by the first component of URSA.

The third component of the URSA framework is a set of techniques to perform the allocation of resources to instructions. The techniques refer to special nodes in GURRR that indicate resources

available for allocation as Resource Holes. The techniques are called Resource Spackling because they perform allocations by trying to fill the resource holes with instructions. The spackling techniques compute properties of the resource holes that affect how instructions can be placed in them. Cases are then identified as to whether or not the placement of instructions in a hole will increase the execution time of the program.

#### 3.2 URSA Applications

The URSA framework is used as the basis for the new and modified compiler back end phases. GURRR provides the resource requirements measurements in an intermediate representation usable by the phases. The spackling techniques are used in any phase that wishes to allocate resources. This research examines three areas of optimization in the compiler back end: resource allocation, application of transformations such as global code motion, and exploitation of architectural features and constraints.

URSA's spackling techniques are general enough to be used in several allocation schemes. This research develops a reduction phase which replaces the phases for local scheduling and global register allocation. It also presents a global scheduling phase modified to perform unified allocation.

The reduction phase implements the Measure and Reduce paradigm to produce an intermediate representation of a program that can be feasibly scheduled. Conceptually, the reduction phase removes excessive parallelism, either in the form of too many instructions that can be executed in parallel or too many values simultaneously alive in registers, by introducing additional sequentially between the offending instructions. The introduction of sequential dependencies is performed by the reduction transformations. The reduction transformations result in moving instructions from the locations with excessive requirements and placing them in resource holes. Simultaneous allocation is achievable by finding overlapping resource holes for all resources that an instruction demands.

Global scheduling consists of moving instructions between control dependence regions in GURRR to evenly distribute ILP on a larger scale than simply within individual regions. URSA techniques are used to ensure that such global code motions are only performed when there are available resources and would result in a reduction in a program's execution time. The availability of resources is ensured by spackling the moved instructions into resource holes in the destination region.

The application of code transformations serves several purposes. They can be used to introduce more ILP, ideally reducing the execution time of a program. They can also be used to

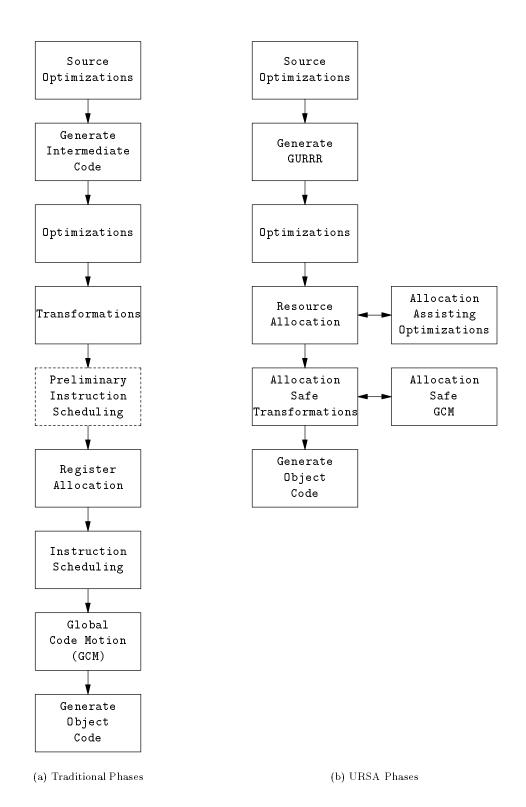

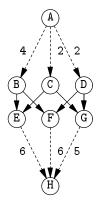

Figure 3.1: Comparison of back end organizations

enable additional transformations, such as ILP exposing transformations, global code motions, and partial dead code elimination. Transformations interact with resource allocation in two ways. First, the resource requirement measurements can be used to drive the application of transformations. The measurements indicate pairs of areas where resource demands are unbalanced; one area demands too many resources while the other under utilizes them. In such situations either ILP exposing transformations or global code motion should be performed to redistribute the parallelism. When areas are not imbalanced neither redistributing or enabling transformations need to be considered.

The second interaction between transformations and resource allocation is predicting the effect of a transformation. For example, assume at a particular point in a program, resources maybe under utilized and several ILP exposing transformations maybe applicable. The different transformations may each expose a different amount of parallelism. The transformation selected should be the one that exposes an amount of parallelism that most closely matches the unused resources. If too much parallelism is exposed, then the resulting excessive resource requirements that must be reduced after the transformation. The incremental nature of the computation of the resource requirements information enables the effects of each candidate transformation to be estimated and the best one to be chosen.

A comparison of phases between a typical traditional compiler back end and a URSA based compiler is shown in Figure 3.1. In both cases source level optimizations are performed before the generation of their respective intermediate representations. Figure 3.1(a) shows the phases in a traditional compiler back end. Following the application of optimizations and transformations, local and global instruction scheduling is performed and then register allocation is carried out. A second local instruction scheduling phase is performed to schedule any inserted spill code. Finally object code is generated. Figure 3.1(b) shows the phases in an URSA based back end. Most optimizations are performed immediately after the GURRR intermediate form is generated. These optimizations are ones that will always reduce execution time (e.g., strength reduction) or register demands (e.g., copy propagation). Resource allocation is performed next using the spackling techniques of URSA to perform requirements reductions. The allocation phase may elect to perform optional optimizations and transformations that aid the reductions (e.q., reordering commutative operations). Once all resources have been allocated, additional code improvements are performed. These improvements include transformations to uncover appropriate amounts of additional parallelism and global code motions to evenly distribute parallelism and reduce critical path lengths. Such improvements are only performed if there are sufficient resources available for the instructions either locally or in areas reachable through global code motions.

### Chapter 4

## Resource Requirements

The first step in developing techniques for the measure and reduce paradigm is performing the analysis of a program's resource needs. This chapter discusses the problems to produce such an analysis, including handling of resources with different usage characteristics, operating on segments of a program, and computing the different types of usage information needed.

A number of different intermediate representations are used by the back ends of compilers. All of these representations break up a program into small segments to simplify the tasks performed in the back end. Although different techniques are used to partition the segments and result in different sets of information available about the segments, all representations use a segment that is acyclic. Examples of acyclic segments include basic blocks in a Control Flow Graph [ASU86], superblocks [HMC+93], traces from Trace Scheduling [Fis81], and control dependence regions from a Program Dependence Graph [FOW87]. These different types of acyclic segments are generically referred to as blocks.

Acyclic blocks provide convenient pieces of a program to analyze for resource requirements, as instruction level parallelism is easily expressed and control flow can be considered as needed. Blocks are typically represented using the Directed Acyclic Graph (DAG)<sup>1</sup>. The nodes of the DAG represent the instructions or operations being scheduled. The edges in a DAG represent several types of dependencies, including data dependencies, preservation of semantic correctness, and scheduler imposed temporal dependencies. The temporal dependence edges are added to introduce sequentiality, that is, reduce parallelism where needed to reduce resource requirements. Thus, the DAG representation of dependence information represents a partial ordering of the instructions, *i.e.*, the DAG represents all schedules which honor the required dependencies.

To support the reduction of excess resource requirements, the measurement algorithm must

<sup>&</sup>lt;sup>1</sup>This work uses the following conventions when representing and discussing DAGs: if node b is dependent on node a then the edge is drawn from a to b, and if a node is not dependent on any other node, it is called a root and is placed at the top of the DAG.

provide several types of information about resource usage in each block. In particular, three types of information must be determined:

- 1. Total number of resources required;

- 2. Locations where requirements exceed available resources; and

- 3. Locations where requirements are less than available resources.

The first item is compared to the number of resources available in the architecture to determine if there are areas with allocation problems. The second item identifies exactly what set(s) of instructions cause allocation problems. The third item indicates where there are additional resources available for allocation.

#### 4.1 Measuring Resource Requirements

This section defines the resource measurements and presents techniques for computing them. The general framework for measuring the various types of resources in the work is described first. The details for the two primary categories of resources are then discussed.

#### 4.1.1 Measurement definitions

The measurements of requirements for the various types of resources in a block are obtained using a single algorithm which operates on a data structure, called a Reuse DAG. A Reuse DAG indicates which instructions can reuse a resource used by an earlier instruction. The difference in the usage characteristics of the various types of resources is handled during the construction of the Reuse DAG for each resource. Resources are placed in one of two categories based upon their usage characteristics.

DEFINITION 1 A resource R is a non-spanning resource if it is in use only during the execution of a single instruction.

DEFINITION 2 A resource R is a spanning resource if a use can start during the execution of one instruction and the use continues until the execution of a subsequent instruction. The beginning and ending instructions are called the defining and killing instructions, respectively.

Since a functional unit is in use only while an instruction is being executed, it is a non-spanning resource. A register is in use from the time that one instruction, the defining instruction,

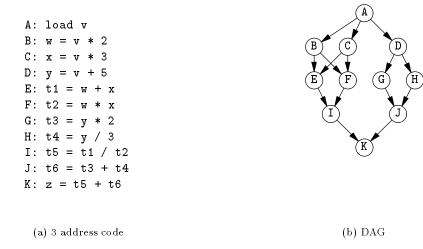

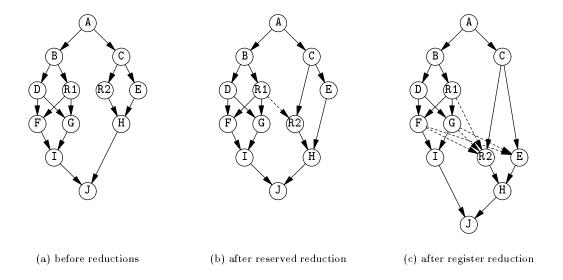

Figure 4.1: Example code and corresponding DAG

places a value in the register until all instructions that need the value have used it from the register.

The last instruction to read the value is the killing instruction.

Several different types of resources may belong to the same resource class. For example, an architecture may have both integer and floating point functional units. In this case there are two functional unit resource types, integer and floating point. Each register bank in an architecture is also a separate resource type.

The first kind of resource requirements information that is computed is the maximum resource requirements for each block. The maximum requirements for a resource, in a given block of a program, is the maximum amount of that resource required under any feasible schedule. It should be noted that a single schedule may not realize the maximum requirements for all resources, but instead different schedules may achieve maximum resource requirements for different resources. Thus the maximum resource requirements represent a worst case scenario.

The algorithm for obtaining the measurements of resource requirements operates on a DAG representing a partial order describing the dependencies. A chain in a partial order is a subset of elements such that every pair of elements in the subset are related. Every path in a DAG is a chain in the corresponding partial order, but a chain is not necessarily a path since it may be noncontiguous. Figure 4.1(a) shows a basic block of code and Figure 4.1(b) shows the corresponding DAG. In Figure 4.1(b), the sets of nodes {A, B, F, K}, {C, E, I}, {D, G, J}, and {H} are all chains.

DEFINITION 3 Let relation Q be a partial order on set  $S^2$ . A chain is a set  $S' \subset S$  such that if  $a,b \in S'$  then either  $(a,b) \in Q$  or  $(b,a) \in Q$ .

<sup>&</sup>lt;sup>2</sup>A relation Q on a set S is a partial ordering if and only if Q is reflexive, transitive, and anti-symmetric.

DEFINITION 4 A decomposition of a partial order P is a partition of P into chains. A decomposition is minimal if there is no other decomposition with fewer chains.

If two nodes are independent, then they may be executed in parallel. The following theorem relates the maximum amount of parallelism to a minimal chain decomposition.

THEOREM 1 The maximum number of independent elements in a partial order is equal to the number of chains in a minimal decomposition[Dil50].

The DAG in Figure 4.1(b) can be minimally decomposed into a set of four chains, such as  $\{A, B, E, I, K\}$ ,  $\{C, F\}$ ,  $\{D, G, J\}$ , and  $\{H\}$ . Thus, at most four nodes at a time can execute in parallel.

If the resources needed can be represented as a partial ordering on the instructions, the task of computing maximum resource requirements can be performed using Theorem 1. The partial ordering on the nodes of a DAG, with respect to resource R, is defined as follows:

DEFINITION 5 Let  $CanReuse_R$  be a relation on nodes of the DAG for resource type R indicating if a resource instance r of type R used by a node can be reused by one of its descendants, i.e.,  $(a,b) \in CanReuse_R$  if and only if there is a node c that ends a's use of r and  $c \in Ancestors(b) \cup \{b\}$ .

In other words, given that (a,b) belongs to the relation  $CanReuse_R$ , there is no schedule such that node b can execute while resource instance r is still in use as a result of executing a. The computation of the  $CanReuse_R$  relation is different for spanning and non-spanning resources.

Definition 6 Reuse<sub>R</sub> DAG  $(N, \bar{E})$  for resource type R is constructed from a program DAG (N, E). All edges  $(a, b) \in \bar{E}$  must meet the following two conditions:

- 1.  $(a,b) \in CanReuse_R$ , and

- 2.  $\not\exists c \ni (a,c) \in CanReuse_R \ and \ (c,b) \in CanReuse_R$ .

The second condition simply eliminates transitive edges from the  $Reuse_R$  DAG. Although this condition is not necessary, it simplifies later discussions and techniques.  $Reuse_R$  DAGs for functional units and registers are denoted as  $Reuse_{FU}$  DAG and  $Reuse_{Reg}$  DAG, respectively. The notation  $Reuse_R$  DAG is used when a reference is not restricted to a particular resource. The DAG in Figure 4.1(b) is both a program DAG and a  $Reuse_{FU}$  DAG.

Definition 7 An allocation chain for resource R is a chain  $n_1, n_2, ...n_l$  such that  $(n_i, n_{i+1}) \in Reuse_RDAG$  for any consecutive members  $n_i, n_{i+1}$  in the chain.

```

function MeasureRequirements ( Reuse_R DAG (N, E) )

returns set of allocation chains

{

/* build the bipartite graph */

for each n \in N

add nodes s_n and t_n to \hat{N};

foreach pair of nodes n, m \in N \times N

if (m \in Ancestors(n))

add the edge (s_m, t_n) to \hat{E};

/* find the maximum matching */

M = BipartiteMatch(\hat{N}, \hat{E})

/* record the allocation chains in AC */

numChains = 0;

for each n \in N such that t_n is not matched

numChains = numChains + 1;

i = n:

add i to AC[numChains];

while ( s_i is matched )

\{i = j, \text{ where } s_i \text{ is matched to } t_j;

add i to AC[numChains];

return AC

}

```

Figure 4.2: Function measureRequirements()

After a  $Reuse_R$  DAG has been decomposed into allocation chains each allocation chain can be assigned a different copy of the resource. However, if there are insufficient resources, these chains provide a measure of the resource requirements. Clearly, all chains in a  $Reuse_R$  DAG are allocation chains. Therefore, by Theorem 1, a minimum decomposition of a  $Reuse_R$  DAG into allocation chains gives the maximum resource requirements of R for the original DAG.

Ford and Fulkerson [FF65] have shown that the problem of finding a minimum chain decomposition can be solved by transforming it into a maximum bipartite graph matching problem. The bipartite graph represents all possible pairs of nodes  $(a,b) \in CanReuse_R$ . Since each node in the  $Reuse_R$  DAG must participate in exactly one chain, a maximum matching finds a minimum number of allocation chains.

Figure 4.2 gives the Function measureRequirements(), which computes and returns the set of allocation chains. The algorithm first builds the bipartite graph from the  $Reuse_R$  DAG by adding a node to each partition corresponding to each node in the DAG and then by adding an edge between each pair of nodes if the sink node can reuse the source node's resource. Next, the bipartite matching algorithm is applied. Finally, the allocation chains are constructed by traversing the matching edges.

Figure 4.3: A bipartite graph matching

Figure 4.4: A complex case for defining Kill()